|

|

PDF CDP1853 Data sheet ( Hoja de datos )

| Número de pieza | CDP1853 | |

| Descripción | N-Bit 1 of 8 Decoder | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CDP1853 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

CDP1853,

CDP1853C

March 1997

N-Bit 1 of 8 Decoder

Features

• Provides Direct Control of Up to 7 Input and 7 Output

Devices

• CHIP ENABLE (CE) Allows Easy Expansion for Multi-

level I/O Systems

Ordering Information

PACKAGE TEMP. RANGE

5V

PKG.

10V NO.

PDIP

-40oC to +85oC CDP1853CE CDP1853E E16.3

Burn-In

SBDIP

CDP1853CEX - E16.3

-40oC to +85oC CDP1853CD CDP1853D D16.3

Burn-In

CDP1853CDX - D16.3

Description

The CDP1853 and CDP1853C are 1 of 8 decoders designed for

use in general purpose microprocessor systems. These

devices, which are functionally identical, are specifically

designed for use as gated N-bit decoders and interface directly

with the 1800-series microprocessors without additional compo-

nents. The CDP1853 has a recommended operating voltage

range of 4V to 10.5V, and the CDP1853C has a recommended

operating voltage range of 4V to 6.5V.

When CHIP ENABLE (CE) is high, the selected output will be

true (high) from the trailing edge of CLOCK A (high-to-low tran-

sition) to the trailing edge of CLOCK B (high-to-low transition).

All outputs will be low when the device is not selected (CE = 0)

and during conditions of CLOCK A and CLOCK B as shown in

Figure 2. The CDP1853 inputs N0, N1, N2, CLOCK A, and

CLOCK B are connected to an 1800-series microprocessor out-

puts N0, N1, N2, TPA, and TPB respectively, when used to

decode I/O commands as shown in Figure 5. The CHIP

ENABLE (CE) input provides the capability for multiple levels of

decoding as shown in Figure 6.

The CDP1853 can also be used as a general 1 of 8 decoder for

I/O and memory system applications as shown in Figure 4.

The CDP1853 and CDP1853C are supplied in hermetic 16-lead

dual-in-line ceramic (D suffix) and plastic (E suffix) packages.

Pinout

16 LEAD DIP

TOP VIEW

CLK A 1

N0 2

N1 3

OUT 0 4

OUT 1 5

OUT 2 6

OUT 3 7

VSS 8

16 VDD

15 CLK B

14 N2

13 CE

12 OUT 4

11 OUT 5

10 OUT 6

9 OUT 7

CDP1853 Functional Diagram

2

N0

3

N1

14

N2

13

CE

1 OF 8

DECODER

EN

4

OUT 0

5 OUT 1

6 OUT 2

7

OUT 3

12 OUT 4

11 OUT 5

10 OUT 6

9 OUT 7

1

CLOCK

A

(TPA)

Qn

15

CLOCK

B

(TPB)

FIGURE 1.

TRUTH TABLE

CE

CL A

CL B

EN

1 0 0 Qn-1†

1011

1100

1111

0XX0

N2 N1 N0 EN 0 1 2 3 4 5 6 7

0 0 0 1 10000000

0 0 1 1 01000000

0 1 0 1 00100000

0 1 1 1 00010000

1 0 0 1 00001000

1 0 1 1 00000100

1 1 0 1 00000010

1 1 1 1 00000001

X X X 0 00000000

1 = High level, 0 = Low level, X = Don’t care

† Qn-1 = Enable remains in previous state.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

4-35

File Number 1189.2

1 page

CDP1853, CDP1853C

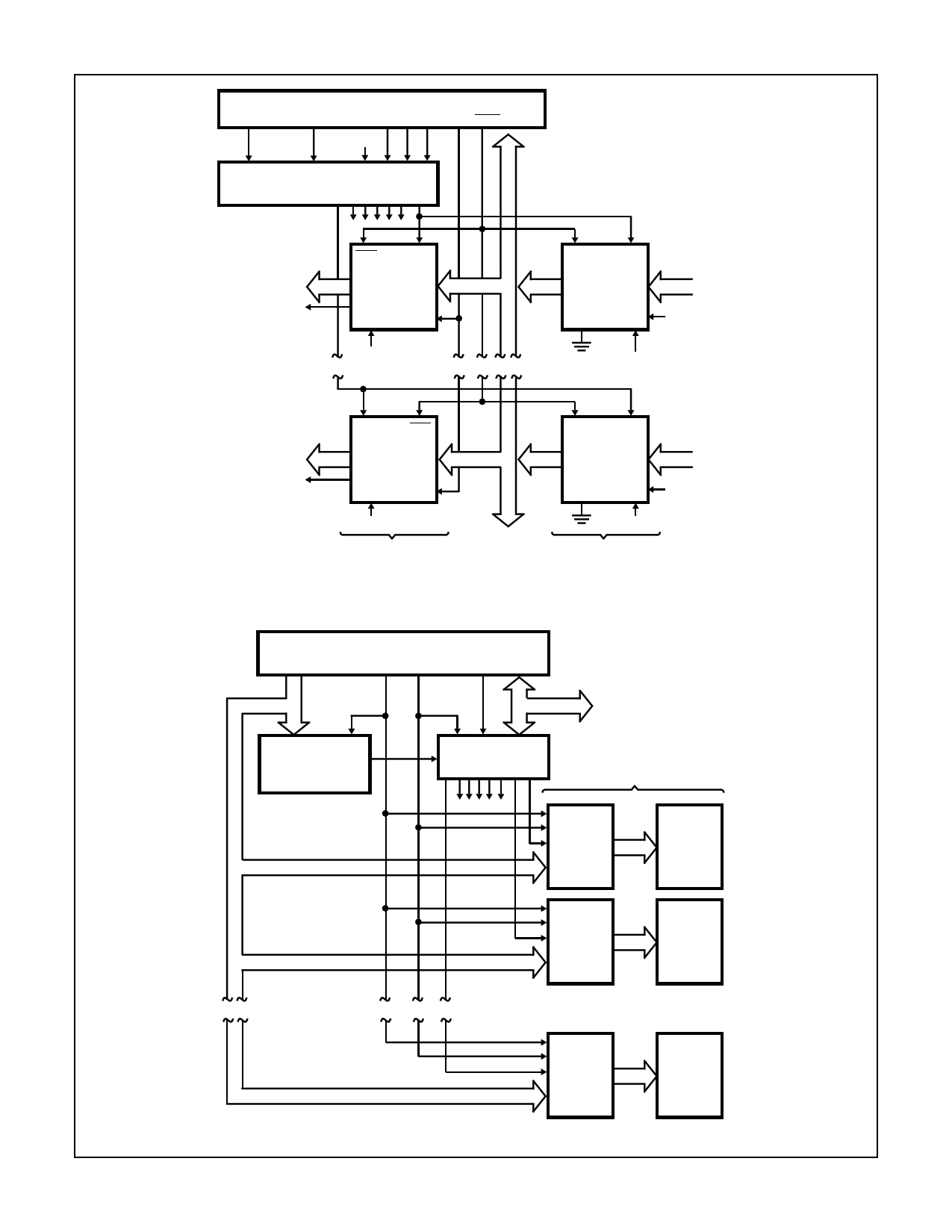

CDP1800 SERIES

TPA TPB

N0 N1 N2 TPB MRD

VDD

CLOCK A

CLOCK B CE N0 N1 N2

CDP1853

01

2-6

7

LOAD VIA 67

INSTRUCTION

DATA AVAILABLE

CS1

CS2

CDP1852

DATA

OUTPUT

PORT 7

SR

MODE TPB

VDD

5 CDP1852 INPUT AND OUTPUT PORTS

CS1

CS2

CDP1852

INPUT

PORT 7

MODE

READ VIA

6F INSTRUCTION

DATA

STROBE

CLOCK

LOAD VIA 61

INSTRUCTION

AVAILABLE

CS2

CS1

CDP1852

OUTPUT

PORT 1

SR

MODE TPB

CS1

CS2

CDP1852

INPUT

PORT 1

MODE

READ VIA

69 INSTRUCTION

DATA

STROBE

VDD CLOCK

7 OUTPUT PORTS

7 INPUT PORTS

FIGURE 5. N-BIT DECODER IN A ONE-LEVEL I/O SYSTEM

NO, N1, N2

CDP1800 SERIES

TPA TPB

MRD

BUS

NOTE: SYSTEM SHOWN WILL SELECT

UP TO 56 INPUT AND 48 OUTPUT

PORTS. WITH ADDITIONAL DECODING

THE TOTAL NUMBER OF INPUT

DATA BUS

AND OUTPUT PORTS CAN BE

FURTHER EXPANDED.

TPA

CDP1853 I

DECODED

“61” INSTRUCTION

CL CSI

CS2 CDP1852

INTERCONNECTED

AS IN FIGURE 4

NO, N1, N2

NO, N1, N2

CLOCK A

CLOCK B

CE

CDP1853

“62-6F”

INST

CLOCK A

CLOCK B

CE

CDP1853

“62-6F”

INST

I/O

7 INPUT

6 OUTPUT

PORTS

I/O

7 INPUT

6 OUTPUT

PORTS

SECTIONS 3-7

NO, N1, N2

CLOCK A

CLOCK B

CE

CDP1853

“62-6F”

INST

I/O

7 INPUT

6 OUTPUT

PORTS

FIGURE 6. TWO-LEVEL I/O USING CDP1853 AND CDP1852

4-39

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet CDP1853.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CDP1851 | CMOS Programmable I/O Interface | Intersil Corporation |

| CDP1851 | CMOS Programmable I/O Interface | GE |

| CDP1851C | CMOS Programmable I/O Interface | Intersil Corporation |

| CDP1851C | CMOS Programmable I/O Interface | GE |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |