|

|

PDF CDP1879C-1 Data sheet ( Hoja de datos )

| Número de pieza | CDP1879C-1 | |

| Descripción | CMOS Real-Time Clock | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CDP1879C-1 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

CDP1879,

CDP1879C-1

March 1997

CMOS Real-Time Clock

Features

• CPU Interface for Use with General-Purpose

Microprocessors

• Time Of Day/Calendar

• Reads Seconds, Minutes, Hours

• Reads Day of Month and Month

• Alarm Circuit With Seconds, Minutes or Hours

Operation

• Power Down Mode

• Separate Clock Output Selects 1 of 15 Square Wave

Signals

• Interrupt Output Activated By Clock Output and/or

Alarm Circuit

• Date Integrity Sampling for Clock Rollover Eliminated

• On-Board Oscillator:

- Crystal Operation CDP1879 at 10V . . . . . . . 4.19MHz,

2.09MHz or 1.048MHz

- Crystal Operation CDP1879C-1 at 5V . . . . . 4.19MHz,

2.09MHz or 1.048MHz or 32kHz

- External Clock Operation at 10V or 5V. . . . 4.19MHz,

2.09MHz, 1.048MHz or 32kHz

• Addressable in Memory Space or CDP1800 Series I/O

Mode

• Low Standby (Timekeeping) Voltage with External Clock

• Related Literature

- AN7275, Guide to the Use of CD1879 and

CDP1879C1 Real Time Clock

Pinout

CDP1879, CDP1879C-1 (PDIP, SBDIP)

TOP VIEW

INT 1

RESET 2

POWER DOWN 3

RD 4

IO/MEM 5

TPB/WR 6

TPA 7

CS 8

A2 9

A1 10

A0 11

VSS 12

24 VDD

23 XTAL

22 XTAL

21

CLK

OUT

20 DB7

19 DB6

18 DB5

17 DB4

16 DB3

15 DB2

14 DB1

13 DB0

Description

The CDP1879 real-time clock supplies time and calendar information

from seconds to months in BCD format. It consists of 5 separately

addressable and programmable counters that divide down an oscillator

input. The clock input can have any one of 4 possible frequencies,

allowing flexibility in the choice of crystal or external clock sources.

Using an external 32kHz clock source, timekeeping can be performed

down to 2.5V (see Standby (Timekeeping) Voltage Operation).

The device can be memory-mapped for use with any general-purpose

microprocessor and has the additional capability of operating in the

CDP1800 series input/output mode.

The real-time clock functions as a time-of-day/calendar with an alarm

capability that can be set for combinations of seconds, minutes or

hours. Alarm time is configured by loading alarm latches that activate

an interrupt output through a comparator when the counter and alarm

latch values are equal.

Fifteen selectable square-wave signals are available as a separate

clock output signal and can also activate the interrupt output. A status

register is available to indicate the interrupt source. The value in an 8 bit

control register determines the operational characteristics of the device,

by selecting the prescaler divisor and the clock output, and controls the

load and alarm functions.

A transparent “freeze” circuit preclude clock rollover during counter and

latch access times to assure stable and accurate values in the counters

and alarm latches.

The CDP1879 is functionally identical to the CDP1879C-1. The

CDP1879 has a recommended operating voltage range of 4V to 10.5V,

and the CDP1879C-1 has a recommended operating voltage range of

4V to 6.5V. The CDP1879 and the CDP1879C-1 are supplied in 24 lead

hermetic dual-in-line side-brazed ceramic packages (D suffix) and 24

lead dual-in-line plastic packages (E suffix).

Ordering Information

PACKAGE

PDIP

SBDIP

Burn-In

TEMP

RANGE

-40oC to

+85oC

-40oC to

+85oC

5V 10V

CDP1879CE1 CDP1879E

CDP1879CD1

CDP1879CD1X

-

-

PKG.

NO.

E24.6

D24.6

D24.6

CDP1879 Modes of Operation

OPERATION

FUNCTION

Read

1. Seconds, minutes, hours, date and month counters

2. Status register to identify interrupt source

Write

1. Control register to set device operation

2. Seconds, minutes, hours, date and month counters

3. Alarm latches for alarm time

Power Down

1. Three-state interrupt output with active alarm or

clock out circuitry for wake-up control

2. Data bus and address inputs are “DON’T CARE”

Interrupt

1. Clock out as source

2. Alarm time as source

3. Either interrupt can occur during normal or power

down mode

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

4-104

File Number 1360.2

1 page

CDP1879, CDP1879C-1

Static Electrical Specifications at TA -40oC to +85oC VDD ± 5%, Unless Otherwise Specified (Continued)

CONDITIONS

LIMITS

CDP1879

CDPl879C-1

PARAMETER

VO VIN VDD

(NOTE 1)

(NOTE 1)

(V) (V) (V) MIN TYP MAX MIN TYP MAX

Input Capacitance

Output Capacitance

Maximum Clock Rise

and Fall Times

CIN

COUT

tR, tF

-

-

-

-

- --

- --

- 5-

- 10 -

5 7.5 -

10 15 -

- 10 -

- 1-

5 7.5

10 15

- 10

--

NOTES:

1. Typical values are for TA = 25oC and nominal VDD.

2. IOL = IOH = 1µA.

3. Operating current measured with clockout = 488.2µs and no load.

4. See Table 3 and Figure 6 for oscillator circuit information.

UNITS

pF

µs

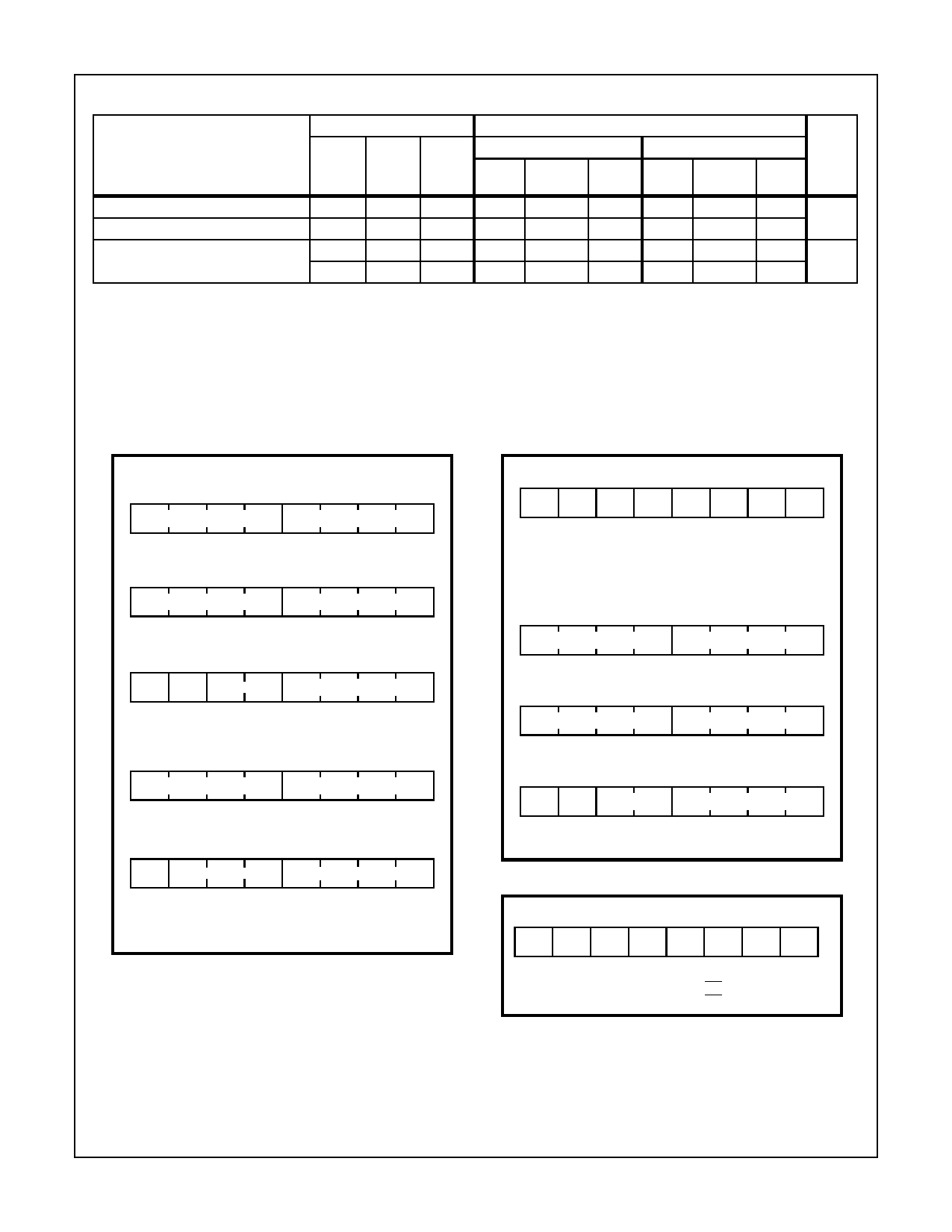

Programming Model

WRITE AND READ REGISTERS

WRITE ONLY REGISTERS

BCD FORMAT

DB7

TENS 0-5

SECONDS COUNTER (00-59)

DB7

TENS 0-5

MINUTES COUNTER (00-59)

UNITS 0-9

UNITS 0-9

DB7 DB6

X X TENS 0-2

UNITS 0-9

HOURS COUNTER (01 - 12 OR 00-23)

DB7 0=AM, 1=PM

DB6 0=24 HR, 1=12 HR

DB7

TENS 0-3

DAY OF MONTH COUNTER

(01-28, 29, 30, 31)

DB7

UNITS 0-9

X TENS 0 OR 1

MONTH COUNTER

(JAN=1 DEC=12)

DB7 0=NO LEAP YEAR

1=LEAP YEAR

UNITS 0-9

DB0

DB0

DB0

DB0

DB0

DB7

76 54 32 1

CONTROL REGISTER

DB0-DB1 - FREQUENCY SELECT

DB2 - START/STOP

DB3 - COUNTER/ALARM LATCH CONTROL

DB4-DB7 - CLOCK OUTPUT SELECT

DB7

TENS 0-5

UNITS 0-9

SECONDS ALARM LATCH (00-59)

DB7

TENS 0-5

UNITS 0-9

MINUTES ALARM LATCH (00-59)

DB7 DB6

X X TENS 0-2

UNITS 0-9

HOURS ALARM LATCH (01-12 OR 00-23

12 HR, DB7=0 AM, 1=PM

24 HR, DB7=X

DB0

0

DB0

DB0

DB0

READ ONLY REGISTER

DB7 DB6

DB0

XX 00 00 00

INTERRUPT STATUS REGISTER

DB7=1 ALARM CIRCUIT ACTIVATED INT.

DB6=1 CLOCK OUTPUT ACTIVATED INT.

4-108

5 Page

CDP1879, CDP1879C-1

250ms of the address “1” access. In memory mapping any

dummy write operation after selecting address “1” will set the

“freeze” circuit. If using the I/O mode, a 61 output instruction

will perform the same function. There is no time restriction

on subsequent accesses as long as the read or write opera-

tions are preceded by selecting address “1”.

Power Down

Power down operation is initiated with a low signal on the

"POWER DOWN” input pin. In conjunction with the interrupt

output, it is used to supply external control circuits with a 3

level control signal. The operating current is not appreciably

reduced during “POWER DOWN” operation. When power

down is initiated, any inputs on the address or data bus are

ignored. The clock output is set low. The interrupt output is

three-stated. If enabled previously, the alarm circuitry is

active and will set the interrupt output pin low when alarm

time occurs. The interrupt output will also go low if a clock

was selected and an internal high-to-low transition occurs

during power down. The clock output pin will remain low. If

power down is initiated in the middle of a read or write

sequence, it will not become activated until the read or write

cycle is completed.

Microprocessor Real-Time Clock

MRD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . RD

TPB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TPB/WR

TPA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TPA

N LINES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ADDRESS LINES

IO/MEM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VDD

CS - CHIP SELECT - Used to enable or disable the inputs

and outputs. TPA is used to strobe and latch a positive level

on this pin to enable the device.

XTAL AND XTAL - The frequency of the internal oscillator is

determined by the value of the crystal connected to these

pins. “XTAL” may be driven directly by an external frequency

source.

Clock Out - 1 of 15 square wave frequencies will appear at

this pin when selected. During power down, this pin will be

placed low, and will be high during normal operation when

the clock is deselected.

Power Down - Power Down Control - A low on this pin will

place the device in the power down mode.

Pin Functions

VDD, VSS - Power and ground for device.

DB0 - DB7 - DATA BUS - 8-bit bidirectional bus that trans-

fers BCD data to and from the counters, latches and regis-

ters.

INT - Interrupt Output - A low on this pin indicates an active

alarm time or high-to-low transition of the “clock out” signal.

RESET - A low on this pin clears the status register and

places the interrupt output pin high.

Frequency Input Requirements

A0, A1, A2 - Address inputs that select a counter, latch or

register to read from or write to.

TPA - Strobe input used to latch the value on the chip select

pin. CS is latched on the trailing edge of TPA. During mem-

ory mapping, it is used to latch the high order address bit

used for the chip select. When the real-time clock is used

with other microprocessors, or when the high order address

of the CDP1800 series microprocessor is externally latched,

it is connected to VDD. In the input/output mode, it is used to

gate the N lines.

IO/MEM - Tied low during memory mapping and high when

the input/output mode of the CDP1800 series microproces-

sor is used.

The Real-Time Clock operates with the following frequency

input sources:

1. An external crystal that is used with the on-board oscilla-

tor. The oscillator is biased by a large feedback resistor

and oscillates at the crystal frequency (see Figure 6,

Table 3).

2. An external frequency input that is supplied at the XTAL

input. XTAL is left open (see Figure 5). A typical external

oscillator circuit is shown in Figure 7 in section, “Standby

(Timekeeping) Voltage Operation”.

RD, TPB/WR - Direction Signals - Active signals that deter-

mine data direction flow. In the memory mapped mode, data

is placed on the bus from the counters or status register

when RD pin is active.

Data is transferred to a counter, latch or the control register

when RD is high and TPB/WR is active and latched on the

trailing edge (low to high) of the TPB/WR signal.

In the input/output mode, data is placed on the bus from a

counter or status register when RD is not active between the

trailing edges of TPA and TPB. Data on the bus is written to a

counter, latch, or the control register during TPB when RD is

active and latched on TPB's trailing edge. The following con-

nections are required between the microprocessor and real-

time clock in the CDP1800 series I/O mode.

4-114

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet CDP1879C-1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CDP1879C-1 | CMOS Real-Time Clock | Intersil Corporation |

| CDP1879C-1 | CMOS Real-Time Clock | GE |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |