|

|

PDF CBTL06DP212 Data sheet ( Hoja de datos )

| Número de pieza | CBTL06DP212 | |

| Descripción | High-performance DisplayPort Gen2 2 : 1 multiplexer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CBTL06DP212 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

CBTL06DP212

High-performance DisplayPort Gen2 2 : 1 multiplexer

Rev. 2 — 3 November 2011

Product data sheet

1. General description

CBTL06DP212 is a high performance multi-channel Generation 2 multiplexer meant for

DisplayPort (DP) v1.2, v1.1a or Embedded DisplayPort applications operating at data rate

of 1.62 Gbit/s, 2.7 Gbit/s or 5.4 Gbit/s. It is designed using NXP proprietary

high-bandwidth pass-gate technology and it can be used for 1 : 2 switching or 2 : 1

multiplexing of four high-speed differential AC-coupled DP channels. Further, it is capable

of switching/multiplexing of Hot Plug Detect (HPD) signal as well as Auxiliary (AUX) and

Display Data Channel (DDC) signals. In order to support GPUs/CPUs that have dedicated

AUX and DDC I/Os, CBTL06DP212 provides an additional level of multiplexing of AUX

and DDC signals delivering true flexibility and choice.

A typical application of CBTL06DP212 is on motherboards where one of two GPU

DisplayPort sources needs to be selected to connect to a DisplayPort sink device or

connector. A controller chip selects which path to use by setting a select signal HIGH or

LOW. Due to the bidirectional nature of the signal paths, CBTL06DP212 can also be used

in the reverse topology, e.g., to connect one display source device to one of two display

sink devices or connectors.

2. Features and benefits

1 : 2 switching or 2 : 1 multiplexing of DisplayPort (v1.2 - 5.4 Gbit/s) signals

4 high-speed differential channels with 2 : 1 multiplexing/switching for DisplayPort

main link signals

1 channel with 4 : 1 multiplexing/switching for AUX or DDC signals

1 channel with 2 : 1 multiplexing/switching for HPD signal

High-bandwidth: 5 GHz at 3 dB

Low insertion loss:

0.5 dB at 100 MHz

3 dB at 5 GHz

Low crosstalk: 35 dB at 3 GHz

Low off-state isolation: 30 dB at 3 GHz

Low return loss: 8 dB at 3 GHz

Very low intra-pair skew (5 ps typical)

Very low inter-pair skew (< 80 ps)

Switch/multiplexer position select CMOS input

DDC and AUX ports tolerant to being pulled to +5 V via 2.2 k resistor

Supports HDMI/DVI incorrect dongle connection

Single 3.3 V power supply

Operation current of 2 mA typical

1 page

NXP Semiconductors

7.2 Pin description

Table 3. Pin description

Symbol

Ball Type

GPU_SEL

A1 3.3 V CMOS

single-ended input

DDC_AUX_SEL C2

3.3 V CMOS

single-ended input

TST0

B7 3.3 V CMOS

single-ended input

IN1_0+

B4 differential I/O

IN1_0

A4 differential I/O

IN1_1+

B5 differential I/O

IN1_1

A5 differential I/O

IN1_2+

B6 differential I/O

IN1_2

A6 differential I/O

IN1_3+

A8 differential I/O

IN1_3

A9 differential I/O

IN2_0+

B8 differential I/O

IN2_0

B9 differential I/O

IN2_1+

D8 differential I/O

IN2_1

D9 differential I/O

IN2_2+

E8 differential I/O

IN2_2

E9 differential I/O

IN2_3+

F8 differential I/O

IN2_3

F9 differential I/O

OUT_0+

B2 differential I/O

OUT_0

B1 differential I/O

OUT_1+

D2 differential I/O

OUT_1

D1 differential I/O

OUT_2+

E2 differential I/O

OUT_2

E1 differential I/O

OUT_3+

F2 differential I/O

OUT_3

F1 differential I/O

AUX1+

H9 differential I/O

AUX1

J9 differential I/O

AUX2+

H6 differential I/O

AUX2

J6 differential I/O

DDC_CLK1 H8 differential I/O

DDC_DAT1

J8

differential I/O

CBTL06DP212

High-performance DisplayPort Gen2 2 : 1 multiplexer

Description

Selects between two multiplexer/switch paths. When HIGH, path 2

left-side is connected to its corresponding right-side I/O. When

LOW, path 1 left-side is connected to its corresponding right-side

I/O.

Selects between DDC and AUX paths. When HIGH, the CLK and

DAT I/Os are connected to their respective DDCOUT terminals.

When LOW, the AUX+ and AUX I/Os are connected to their

respective DDCOUT terminals.

Test pin for NXP use only. Should be tied to VDD in normal

operation.

Four high-speed differential pairs for DisplayPort or PCI Express

signals, path 1, left-side.

Four high-speed differential pairs for DisplayPort or PCI Express

signals, path 2, left-side.

Four high-speed differential pairs for DisplayPort or PCI Express

signals, right-side.

High-speed differential pair for AUX signals, path 1, left-side.

High-speed differential pair for AUX signals, path 2, left-side.

Pair of single-ended terminals for DDC clock and data signals,

path 1, left-side.

CBTL06DP212

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 3 November 2011

© NXP B.V. 2011. All rights reserved.

5 of 18

5 Page

NXP Semiconductors

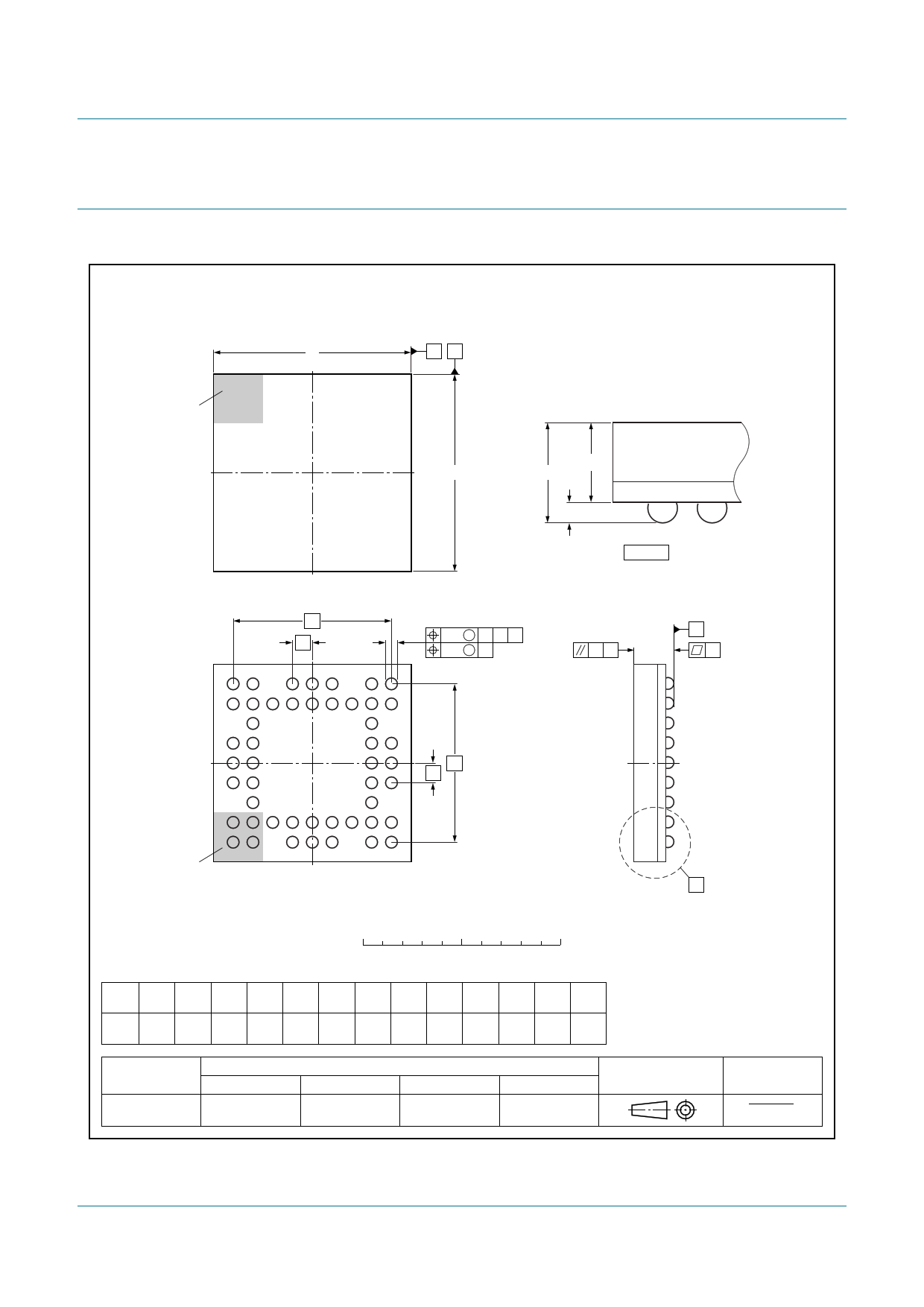

13. Package outline

CBTL06DP212

High-performance DisplayPort Gen2 2 : 1 multiplexer

TFBGA48: plastic thin fine-pitch ball grid array package; 48 balls; body 5 x 5 x 0.8 mm

SOT918-1

ball A1

index area

D

BA

A2

EA

A1

detail X

e1

eb

J

H

G

F

E

D

C

B

A

ball A1

index area

123456789

∅v M C A B

∅w M C

e2

e

y1 C

C

y

X

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT

A

max

A1

A2

b

D

E

e

e1 e2

v

w

y y1

mm

1.15

0.25

0.15

0.90

0.75

0.35

0.25

5.1

4.9

5.1

4.9

0.5

4

4 0.15 0.05 0.08 0.1

OUTLINE

VERSION

SOT918-1

IEC

---

REFERENCES

JEDEC

JEITA

MO-195

---

EUROPEAN

PROJECTION

ISSUE DATE

05-09-21

05-10-13

Fig 5. Package outline TFBGA48 (SOT918-1)

CBTL06DP212

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 3 November 2011

© NXP B.V. 2011. All rights reserved.

11 of 18

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CBTL06DP212.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CBTL06DP211 | DisplayPort Gen1 2 : 1 multiplexer | NXP Semiconductors |

| CBTL06DP212 | High-performance DisplayPort Gen2 2 : 1 multiplexer | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |