|

|

PDF S70GL02GS Data sheet ( Hoja de datos )

| Número de pieza | S70GL02GS | |

| Descripción | 2 Gbit (256 Mbyte) 3.0V Flash Memory | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S70GL02GS (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

S70GL02GS

2 Gbit (256 Mbyte)

3.0V Flash Memory

General Description

The Cypress S70GL02GS 2-Gigabit MirrorBit® Flash memory device is fabricated on 65 nm MirrorBit Eclipse process technology.

This device offers a fast page access time of 25 ns with a corresponding random access time of 110 ns. It features a Write Buffer

that allows a maximum of 256 words/512 bytes to be programmed in one operation, resulting in faster effective programming time

than standard single byte/word programming algorithms. This makes the device an ideal product for today’s embedded applications

that require higher density, better performance and lower power consumption.

This document contains information for the S70GL02GS device, which is a dual die stack of two S29GL01GS die. For detailed

specifications, please refer to the discrete die data sheet:

Document

S29GL01GS Data Sheet

Cypress Document Number

001-98285

Distinctive Characteristics

CMOS 3.0 Volt Core with Versatile I/O™

Two 1024 Megabit (S29GL01GS) in a single 64-ball

Fortified-BGA package (see S29GL01GS datasheet for full

specifications)

65 nm MirrorBit Eclipse™ process technology

Single supply (VCC) for read / program / erase (2.7V to 3.6V)

Versatile I/O Feature

– Wide I/O voltage (VIO): 1.65V to VCC

x16 data bus

16-word/32-byte page read buffer

512-byte Programming Buffer

– Programming in Page multiples, up to a maximum of 512

bytes

Sector Erase

– Uniform 128-kbyes sectors

– S70GL02GS: two thousand forty-eight sectors

Suspend and Resume commands for Program and Erase

operations

Performance Characteristics

Status Register, Data Polling, and Ready/Busy pin methods

to determine device status

Advanced Sector Protection (ASP)

– Volatile and non-volatile protection methods for each

sector

Separate 1024-bye One Time Program (OTP) array with two

lockable regions

– Available in each device Support for CFI (Common Flash

Interface)

WP# input

– Protects first or last sector, or first and last sectors of each

device, regardless of sector protection settings

Industrial temperature range (–40°C to +85°C)

100,000 erase cycles per sector typical

20-year data retention typical

Packaging Options

– 64-ball LSH Fortified BGA, 13 mm x 11 mm

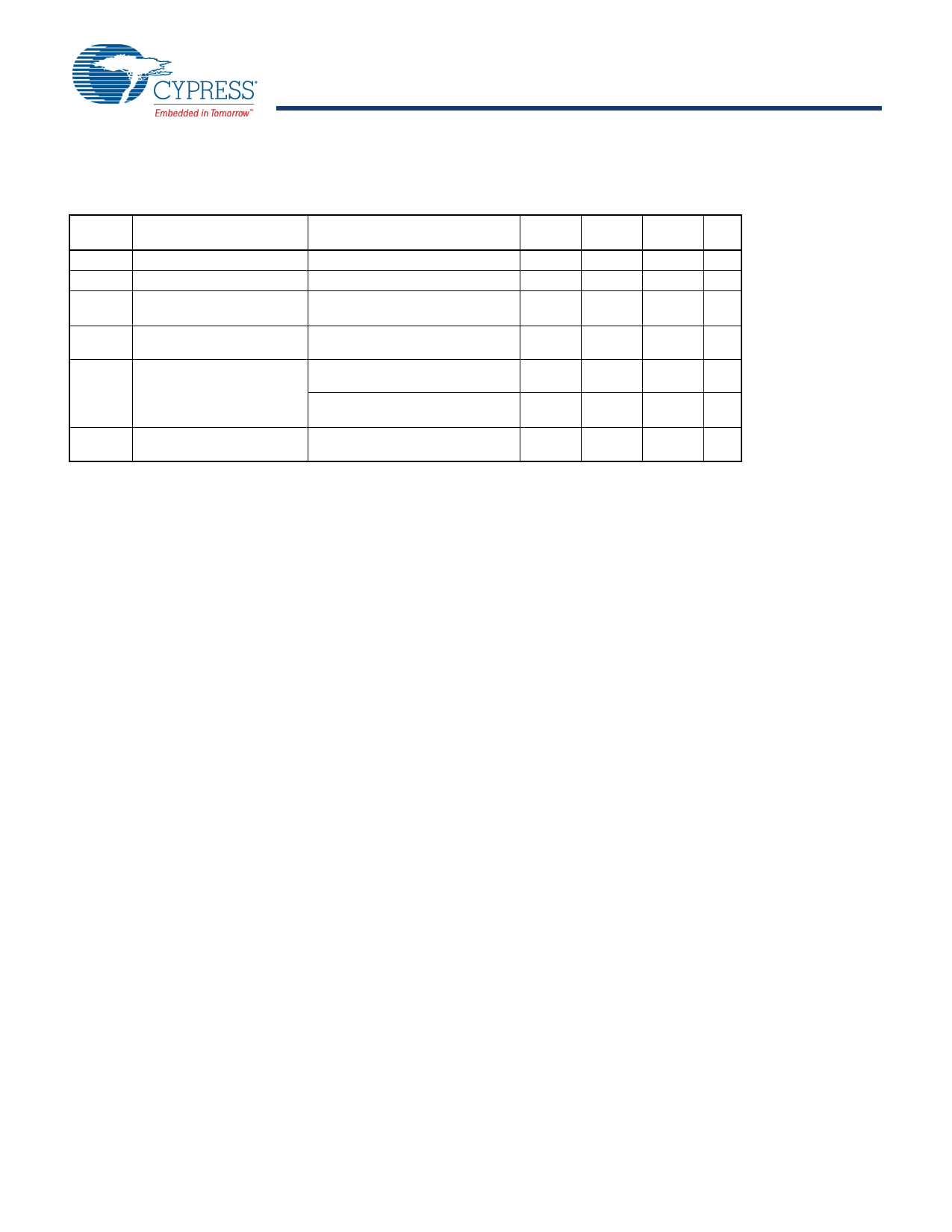

Max. Read Access Times (ns) (Note 1)

Parameter

2 Gb

Random Access Time (tACC)

Page Access Time (tPACC)

CE# Access Time (tCE)

OE# Access Time (tOE)

110

20

110

25

120

30

120

35

Notes

1. Access times are dependent on VIO operating ranges. See Ordering

Information on page 3 for further details.

2. Contact a sales representative for availability.

Typical Program and Erase Rates

Buffer Programming (512 bytes)

Sector Erase (128 kbytes)

1.5 MB/s

477 kB/s

Maximum Current Consumption

Active Read at 5 MHz, 30 pF

Program

Erase

Standby

60 mA

100 mA

100 mA

200 µA

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 001-98296 Rev. *G

• San Jose, CA 95134-1709 • 408-943-2600

Revised Friday, July 08, 2016

1 page

S70GL02GS

3. Block Diagrams

Figure 3.1 Block Diagram for 2 x GL01GS (Highest and Lowest Address Sectors Protected)

A26

A0 to A25

CE#

OE#

WE#

RESET#

WP#

AMAX+1 Ext

A0-A25

CE#

OE#

WE#

RESET#

WP#

1 Gb Flash

(Flash 1)

VCC

VCCQ

VSS

VSSQ

AMAX+1 Int

DQ0-15

RY/BY#

VCC

VIO

VSS

DQ0-15

RY/BY#

Amax+1 Ext

A0-A25

CE#

OE#

WE#

RESET#

WP#

1 Gb Flash

(Flash 2)

VCC

VCCQ

VSS

VSSQ

AMAX+1 Int

DQ0-15

RY/BY#

Document Number: 001-98296 Rev. *G

Page 5 of 19

5 Page

S70GL02GS

6. DC Characteristics

Table 6.1 DC Characteristics

Parameter

Description

Test Conditions

Min

Typ

Max

Unit

(Note 2)

ILI

ILO

ICC4

ICC5

ICC6

ICC7

Input Load Current

Output Leakage Current

VCC Standby Current

VCC Reset Current (Notes 2, 7)

Automatic Sleep Mode (Note 3)

VCC Current during power up

(Notes 2, 6)

VIN = VSS to VCC, VCC = VCC max

VOUT = VSS to VCC, VCC = VCC max

CE#, RESET#, OE# = VIH, VIH = VIO

VIL = VSS, VCC = VCC max

CE# = VIH, RESET# = VIL,

VCC = VCC max

VIH = VIO, VIL = VSS ,

VCC = VCC max, tACC + 30 ns

VIH = VIO, VIL = VSS,

VCC = VCC max, tASSB

RESET# = VIO, CE# = VIO, OE# = VIO,

VCC = VCC max,

+0.04

+0.04

140

20

6

200

106

±2.0

±2.0

200

µA

µA

µA

40 mA

12 mA

300 µA

160 mA

Notes

1. ICC active while Embedded Algorithm is in progress.

2. Not 100% tested.

3. Automatic sleep mode enables the lower power mode when addresses remain stable for a designated time.

4. VIO = 1.65V to VCC or 2.7V to VCC depending on the model.

5. VCC = 3V and VIO = 3V or 1.8V. When VIO is at 1.8V, I/O pins cannot operate at >1.8V.

6. During power-up there are spikes of current demand, the system needs to be able to supply this current to insure the part initializes correctly.

7. If an embedded operation is in progress at the start of reset, the current consumption will remain at the embedded operation specification until the embedded operation

is stopped by the reset. If no embedded operation is in progress when reset is started, or following the stopping of an embedded operation, ICC7 will be drawn during

the remainder of tRPH. After the end of tRPH the device will go to standby mode until the next read or write.

8. The recommended pull-up resistor for RY/BY# output is 5k to 10k Ohms.

9. For all other DC current values please refer to the S29GL-128S_01GS_00 data sheet.

Document Number: 001-98296 Rev. *G

Page 11 of 19

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet S70GL02GS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S70GL02GP | 2 Gbit / 3V Page Mode S70GL-P MirrorBit Flash | Cypress Semiconductor |

| S70GL02GP | 3.0 Volt-only Page Mode Flash Memory | SPANSION |

| S70GL02GS | 2 Gbit (256 Mbyte) 3.0V Flash Memory | Cypress Semiconductor |

| S70GL02GT | 2-Gbit (256-Mbyte) 3.0V Flash Memory | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |