|

|

PDF CAT504 Data sheet ( Hoja de datos )

| Número de pieza | CAT504 | |

| Descripción | 8-Bit Quad DACpot | |

| Fabricantes | Catalyst Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CAT504 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

CAT504

8-Bit Quad DACpot

FEATURES

s Output settings retained without power

s Output range includes both supply rails

s 4 independently addressable outputs

s 1 LSB Accuracy

s Serial µP interface

s Single supply operation: 2.7V-5.5V

s Setting read-back without effecting outputs

APPLICATIONS

s Automated product calibration.

s Remote control adjustment of equipment

s Offset, gain and zero adjustments in Self-

Calibrating and Adaptive Control systems.

s Tamper-proof calibrations.

DESCRIPTION

The CAT504 is a quad 8-Bit Memory DAC designed as

an electronic replacement for mechanical potentiom-

eters and trim pots. Intended for final calibration of

products such as camcorders, fax machines and cellular

telephones on automated high volume production lines,

it is also well suited for systems capable of self calibra-

tion, and applications where equipment which is either

difficult to access or in a hazardous environment, re-

quires periodic adjustment.

The 4 independently programmable DAC's have an

output range which includes both supply rails. Output

settings, stored in non-volatile EEPROM memory, are

not lost when the device is powered down and are

automatically reinstated when power is returned. Each

output can be dithered to test new output values without

effecting the stored settings and stored settings can be

read back without disturbing the DAC’s output.

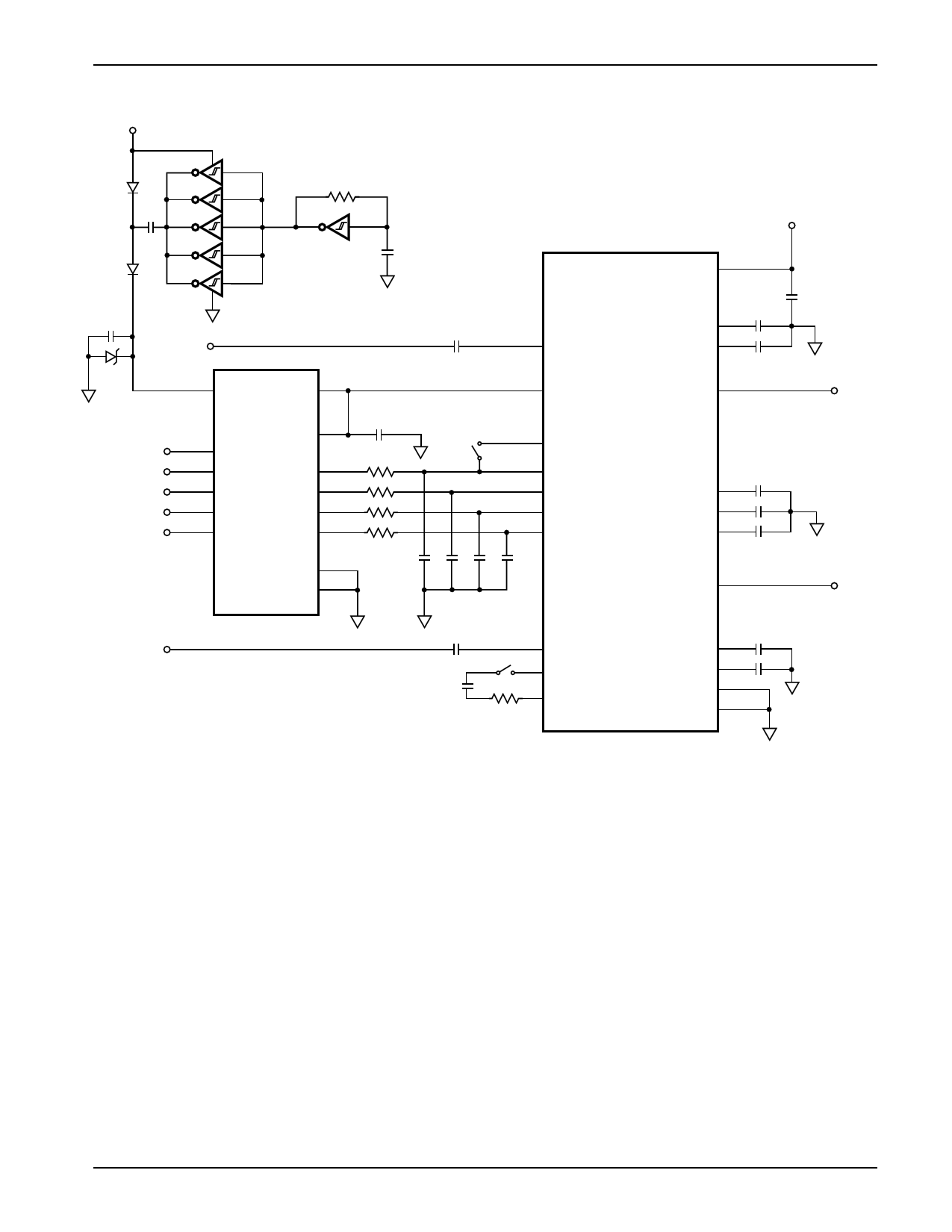

FUNCTIONAL DIAGRAM

VPP

VDD

VREFH

3 1 14

PROG

7

PROGRAM

CONTROL

DAC 1

13

VOUT 1

5

DI

CLK

2

4

CS

SERIAL

CONTROL

DATA

REGISTER

& EEPROM

DAC 2

DAC 3

12

VOUT 2

11

VOUT 3

Control of the CAT504 is accomplished with a simple 3

wire serial interface. A Chip Select pin allows several

CAT504s to share a common serial interface and com-

munication back to the host controller is via a single

serial data line thanks to the CAT504’s Tri-Stated Data

Output pin.

The CAT504 operates from a single 3–5 volt power

supply drawing just a few milliwatts of power. When

storing data in EEPROM memory an additional 20 volt

low current supply is required.

The CAT504 is available in the 0 to 70° C Commercial

and –40° C to + 85° C Industrial operating temperature

ranges and offered in 14-pin plastic DIP and Surface

mount packages.

PIN CONFIGURATION

DIP Package (P)

SOIC Package (J)

VDD

CLK

VPP

CS

DI

DO

PROG

1 14

2 13

3 12

4 CAT 11

504

5 10

69

78

VREFH VDD

VOUT1 CLK

VOUT2

VOUT3

VOUT4

VREFL

VPP

CS

DI

DO

GND PROG

1 14

2 13

3 12

4 CAT 11

5 504 10

69

78

VREFH

VOUT1

VOUT2

VOUT3

VOUT4

VREFL

GND

DAC 4

10

VOUT 4

CAT504

8

GND

SERIAL

DATA

OUTPUT

REGISTER

9

VREF L

6

DO

© 1998 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

1

Doc. No. 25048-0A 2/98 M-1

1 page

PIN DESCRIPTION

Pin Name Function

1 VDD Power supply positive.

2 CLK Clock input pin

3 VPP EEPROM Programming Voltage

4 CS Chip Select

5 DI Serial data input pin.

6 DO Serial data output pin.

7 PROG EEPROM Programming Enable

Input

8

GND

Power supply ground.

9

VREFL

Minimum DAC output voltage.

10

VOUT4

DAC output channel 4.

11

VOUT3

DAC output channel 3.

12

VOUT2

DAC output channel 2.

13

VOUT1

DAC output channel 1.

14

VREFH

Maximum DAC output voltage.

CAT504

DAC addressing is as follows:

DAC OUTPUT

VOUT1

VOUT2

VOUT3

VOUT4

A0 A1

00

10

01

11

DEVICE OPERATION

The CAT504 is a quad 8-bit Digital to Analog Converter

(DAC) whose outputs can be programmed to any one of

256 individual voltage steps. Once programmed, these

output settings are retained in non-volatile EEPROM

memory and will not be lost when power is removed from

the chip. Upon power up the DACs return to the settings

stored in EEPROM memory. Each DAC can be written

to and read from independently without effecting the

output voltage during the read or write cycle. Each

output can also be temporarily adjusted without chang-

ing the stored output setting, which is useful for testing

new output settings before storing them in memory.

DIGITAL INTERFACE

The CAT504 employs a standard 3 wire serial control

interface consisting of Clock (CLK), Chip Select (CS)

and Data In (DI) inputs. For all operations, address and

data are shifted in LSB first. In addition, all digital data

must be preceded by a logic “1” as a start bit. The DAC

address and data are clocked into the DI pin on the

clock’s rising edge. When sending multiple blocks of

information a minimum of two clock cycles is required

between the last block sent and the next start bit.

Multiple devices may share a common input data line by

selectively activating the CS control of the desired IC.

Data Outputs (DO) can also share a common line

because the DO pin is Tri-Stated and returns to a high

impedance when not in use.

CHIP SELECT

Chip Select (CS) enables and disables the CAT504’s

read and write operations. When CS is high data may be

read to or from the chip, and the Data Output (DO) pin is

active. Data loaded into the DAC control registers will

remain in effect until CS goes low. Bringing CS to a logic

low returns all DAC outputs to the settings stored in

EEPROM memory and switches DO to its high imped-

ance Tri-State mode.

Because CS functions like a reset the CS pin has been

equipped with a 30 ns to 90 ns filter circuit to prevent

noise spikes from causing unwanted resets and the loss

of volatile data.

CLOCK

The CAT504’s clock controls both data flow in and out of

the IC and EEPROM memory cell programming. Serial

data is shifted into the DI pin and out of the DO pin on the

clock’s rising edge. While it is not necessary for the clock

to be running between data transfers, the clock must be

operating in order to write to EEPROM memory, even

though the data being saved may already be resident in

the DAC control register.

No clock is necessary upon system power-up. The

CAT504’s internal power-on reset circuitry loads data

from EEPROM to the DACs without using the external

clock.

As data transfers are edge triggered clean clock transi-

tions are necessary to avoid falsely clocking data into the

control registers. Standard CMOS and TTL logic fami-

lies work well in this regard and it is recommended that

any mechanical switches used for breadboarding or

device evaluation purposes be debounced by a flip-flop

or other suitable debouncing circuit.

5 Doc. No. 25048-0A 2/98 M-1

5 Page

APPLICATION CIRCUITS (Cont.)

+12V

CAT504

1N914

1.0 µF

10K

+12V

1N914

74C14

.005 µF

VCC 13

2.5 µF

INPUT 1

20V

IN5250B

CHIP SELECT.

PROGRAM

DATA IN

DATA OUT

CLOCK

3

Vpp

1

VDD

OCPATT550044

4 CS

14

VREFH

7 PROG

5 DI

6

DO

2 CLK

VOUT 1 13

VOUT 2 12

11

VOUT 3

VOUT 4 10

9

VREFL

8

GND

1.0 µF

47K

47K

47K

47K

0.47 µF

2

IN 1

TREB CAP

BASS CAP

4

8

0.01 µF

0.39 µF

0.1 µF

19 VZ

10

OUTPUT 1

LM1040

9

LOUDNESS

14 VOLUME

11 BALANCE

5 TREBLE

16 BASS

0.22 0.22 0.22 0.22

µF µF µF µF

BYPASS

1

7

18

47 µF

10 µF

10 µF

OUT 1

15

OUTPUT 2

OUT 2

INPUT 2

0.47 µF

0.1 µF

4.7K

23 IN 2

3

STEREO

22 ENHANCE

0.39 µF

17

BASS CAP

21

TREB CAP

24 0.01 µF

GND

12

GND

Digital Stereo Control

11 Doc. No. 25048-0A 2/98 M-1

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet CAT504.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CAT504 | 8-Bit Quad DACpot | Catalyst Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |