|

|

PDF HMP8156EVAL1 Data sheet ( Hoja de datos )

| Número de pieza | HMP8156EVAL1 | |

| Descripción | NTSC/PAL Encoders | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HMP8156EVAL1 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

HMP8154, HMP8156A

October 1998

File Number 4343.3

NTSC/PAL Encoders

The HMP8154 and HMP8156A NTSC and PAL encoders

are designed for use in systems requiring the generation of

high-quality NTSC and PAL video from digital image data.

YCbCr or RGB digital video data drive the P0-P23 inputs.

Overlay inputs are processed and the data is 2x upsampled.

The Y data is optionally lowpass filtered to 6MHz and drives

the Y analog output. Cb and Cr are each lowpass filtered to

1.3MHz, quadrature modulated, and summed. The result

drives the C analog output. The digital Y and C data are also

added together and drive the two composite analog outputs.

The YCbCr data may also be converted to RGB data to drive

the DACs, allowing support for analog component RGB and

the European SCART connector.

The DACs can drive doubly-terminated (37.5Ω) lines, and

run at a 2x oversampling rate to simplify the analog output

filter requirements. Any unused DACs may be powered down

to reduce power consumption.

Ordering Information

TEMP.

PART NUMBER RANGE (oC) PACKAGE

PKG. NO.

HMP8154CN

0 to 70 64 Ld PQFP Q64.14x14

HMP8156ACN

0 to 70 64 Ld PQFP Q64.14x14

HMP8154EVAL1 Daughter/Stand-Alone Card Evaluation

HMP8156EVAL1 Platform (Note)

HMP8156EVAL2 Frame Grabber Evaluation Platform (Note)

NOTE: Described in the Applications Section

Features

• (M) NTSC and (B, D, G, H, I, M, N, CN) PAL Operation

• ITU-R BT.601 and Square Pixel Operation

• Digital Input Formats

- 4:2:2 YCbCr

- 8-Bit or 16-Bit

- 4:4:4 RGB

- 16-Bit (5, 6, 5) or 24-Bit (8, 8, 8)

- Linear or Gamma-Corrected

- 8-Bit BT.656

• Overlay Mixing

- 7 Colors

- Internal, External, or Hard Mixing Control

• Analog Output Formats

- Y/C + Two Composite

- RGB + Composite (SCART)

• Flexible Video Timing Control

- Timing Master or Slave

- Programmable Input Sync Timing

- Selectable Polarity on Each Control Signal

- Programmable Blank Output Timing

- Field Output

• Closed Caption Encoding for NTSC and PAL

• 2x Upscaling of SIF Video

• Three Line Vertical Flicker Filter

(HMP8154 only)

• Four 2x Oversampling, 10-Bit DACs with Power Down

• I2C Interface

• Verilog Models Available

Applications

• Multimedia PCs

• Video Conferencing

• Video Editing

• Related Products

- NTSC/PAL Encoders:

HMP8170-HMP8173

- HMP8190/91

- NTSC/PAL Decoders:

HMP8112A, HMP8115, HMP8116, HMP8130/31

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

1 page

HMP8154, HMP8156A

The last pixel output of the overlay uses 87.5% overlay color

plus 12.5% pixel color. The next output uses 12.5% overlay

color plus 87.5% pixel color. Additional outputs use 100%

pixel color.

When going from one overlay color to another, mixing

starts one pixel before the selection of the new overlay

color, and uses 12.5% new overlay color plus 87.5% old

overlay color. The next output is aligned with the selection

of the new overlay color and uses 87.5% new overlay color

plus 12.5% old overlay color. Additional outputs use 100%

new overlay color.

Overlay Mixing: No Mixing

With no overlay mixing selected, whenever the OL0-OL2

inputs are non-zero, the overlay color is displayed. The M0

and M1 inputs are ignored, and no internal mixing is done.

Essentially, this is a hard switch between overlay and pixel

data. In this mode, there is no minimum number of pixels an

overlay color or pixel color must be selected.

2X Upscaling Processing

Following overlay processing, 2X upscaling may optionally

be applied to the pixel data. In this mode, the

HMP8154/HMP8156A accepts NTSC (PAL) SIF resolution

video at 59.94 (50) frames per second and generates

standard interlaced video with 262.5 (312.5) lines per field at

59.94 (50) fields per second. This mode of operation allows

SIF video to be upscaled to full resolution and recorded on a

VCR or displayed on a TV. SIP upscaling may be used to

simplify PC to TV applications.

The input pixel data rate is reduced by half when 2X

upscaling is enabled. The color space conversion generates,

and the overlay mixer uses, 2:2:2 YCbCr data instead of

4:4:4 data. For rectangular pixel NTSC and PAL video, the

input rate is 6.75MHz during the active portion of each line

instead of 13.5MHz. Example SIF input resolutions and

resulting output resolutions are shown in Table 4.

TABLE 4. TYPICAL RESOLUTIONS FOR 2X UPSCALING

INPUT ACTIVE

RESOLUTION

OUTPUT ACTIVE

RESOLUTION

352 x 240

352 x 288

320 x 240

384 x 288

704 x 480

704 x 576

640 x 480

768 x 576

The HMP8154/HMP8156A performs horizontal 2X upscaling

by linear interpolation. The vertical scaling is done by line

duplication. For typical line duplication, the same frame of

SIF pixel input data is used for both the odd and even fields.

Note that a frame of SIF size input has about the same

number of lines as a field of full size input.

After 2X upscaling, the input is 4:4:4 YCbCr data ready for

video processing. Flicker filtering is not available when 2X

upscaling is enabled.

Flicker Filter Processing

Following overlay processing, vertical flicker filtering may

optionally be applied to the pixel data by the HMP8154. The

HMP8156A does not provide flicker filter capability. In flicker

filter mode, the HMP8154 accepts non-interlaced NTSC

(PAL) full resolution video with 525 (625) lines per frame at

59.94 (50) frames per second. It generates standard

interlaced video with 262.5 (312.5) lines per field at 59.94

(50) fields per second.

Each frame of non-interlaced video is vertically low pass

filtered and used to generate either an odd or even field of

video. This mode of operation reduces flickering caused by

image details that are less than two pixels high.

Since an entire frame of input is used to generate one field of

output, the input pixel data rate is doubled when the flicker

filter is enabled. The encoder must receive two lines of data

during each line time. For rectangular pixel NTSC and PAL

video, the input rate is 27.0MHz during the active portion of

each line instead of 13.5MHz. Because of the high input data

rate, 8-bit YCbCr and BT.656 input formats and 2X upscaling

of SIF input may not be used when the flicker filter is enabled.

The HMP8154 uses internal line stores and a 3 tap FIR filter

to reduce flickering. The filter coefficients are 0.25, 0.5, and

0.25. At the start and end of each field, the coefficients are

modified to compensate for the insufficient number of lines

available for processing.

When filtering is enabled, there is an additional two line time

delay through the encoder. After flicker filtering, the input is

4:4:4 YCbCr data ready for video processing. 2X upscaling

is not available when the flicker filter is enabled.

Pixel Input and Control Signal Timing

The pixel input timing and the video control signal

input/output timing of the HMP8154/HMP8156A depend on

the part’s operating mode. The periods when the encoder

samples its inputs and generates its outputs are

summarized in Table 5.

Figures 1-12 show the timing of CLK, CLK2, BLANK, and the

pixel and overlay input data with respect to each other.

BLANK may be an input or an output; the figures show both.

When it is an input, BLANK must arrive coincident with the

pixel and overlay input data; all are sampled at the same time.

When BLANK is an output, its timing with respect to the pixel

and overlay inputs depends on the blank timing select bit in the

timing_I/O_1 register. If the bit is cleared, the

HMP8154/HMP8156A deasserts BLANK one CLK cycle before

it samples the pixel and overlay inputs. As shown in the timing

figures, the encoder samples the inputs 1-7 CLK2 periods after

negating BLANK, depending on the operating mode.

If the bit is set, the encoder deasserts BLANK during the

same CLK cycle in which it samples the input data. In effect,

the input data must arrive one CLK cycle earlier than when

the bit is cleared. This mode is not shown in the figures.

5

5 Page

HMP8154, HMP8156A

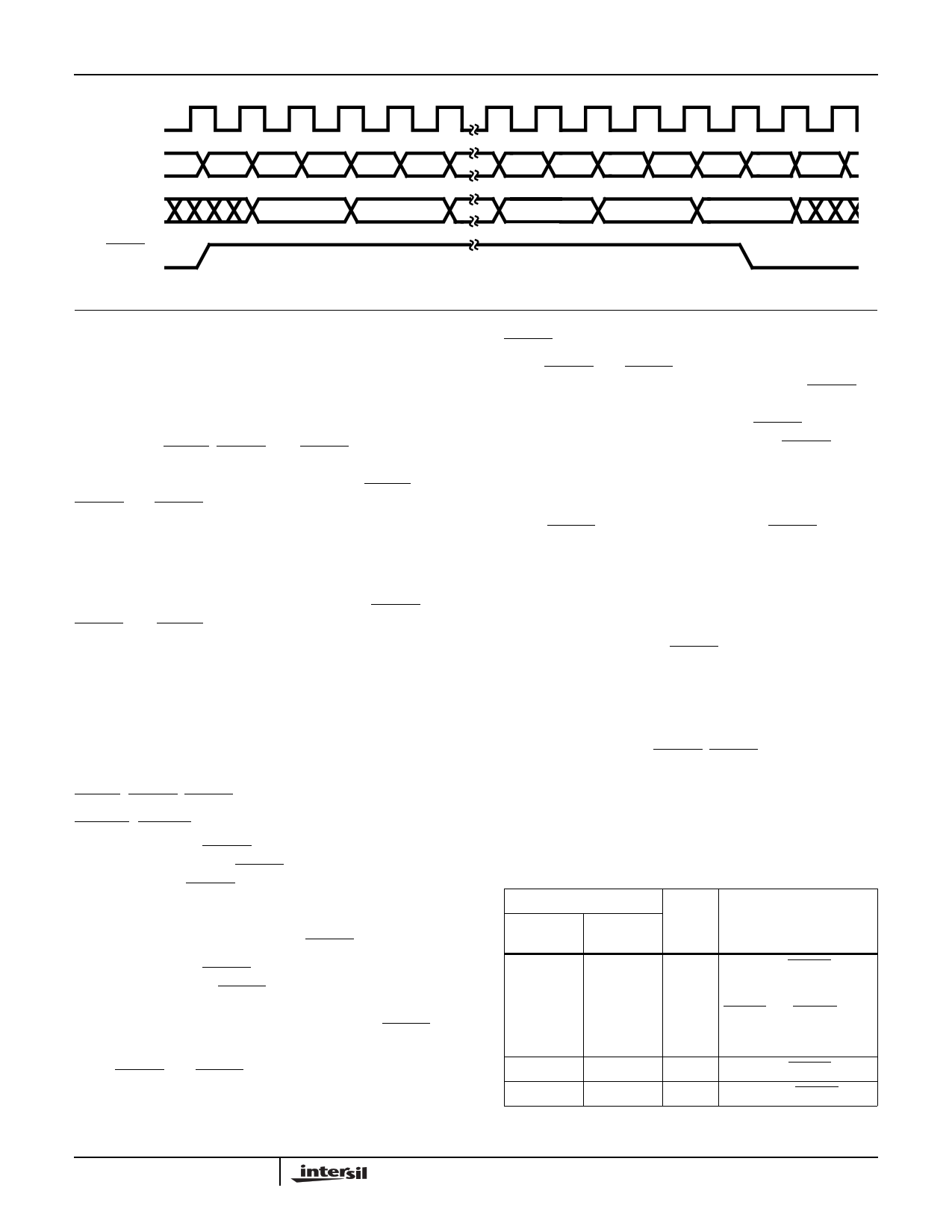

CLK2

P8-P15 Cb 2 Y 2 Cr 2 Y 3 Cb 4 Y 4

"FF" "00" "00" "XY" "10" "80" "10"

OL0-OL2,

M1, M0

PIXEL 0

PIXEL 1

PIXEL N-2

PIXEL N-1

PIXEL N

BLANK

(OUTPUT)

FIGURE 12. PIXEL AND OVERLAY INPUT TIMING - BT.656

8-Bit BT.656 Format

When BT.656 format is selected, data is latched on each

rising edge of CLK2. Overlay data is latched when the Y

input data is latched. However, the overlay data must arrive

three pixels after its corresponding Y data. The pixel and

overlay input timing is shown in Figure 12.

As inputs, the BLANK, HSYNC, and VSYNC pins are

ignored since all timing is derived from the EAV and SAV

sequences within the data stream. As outputs, BLANK,

HSYNC and VSYNC are output following the rising edge of

CLK2. If the CLK pin is configured as an input, it is ignored. If

configured as an output, it is one-half the CLK2 frequency.

Square pixel operation, overlay processing with internal

mixing, flicker filtering, and SIF mode 2X upsampling are not

supported for the BT.656 input format. Also, the HSYNC,

VSYNC, and BLANK signals must be configured as outputs.

Video Timing Control

Regardless of the input mode, the output video timing of the

HMP8154/HMP8156A is at 50 or 59.94 fields per second

(interlaced). For normal and 2X upscaling modes, the pixel

input timing is at 50 or 59.94 fields per second; with the

flicker filter enabled, the input timing rate is twice as fast. The

output video and pixel input timing is controlled by the

BLANK, HSYNC, VSYNC, FIELD, and CLK2 pins.

HSYNC, VSYNC, and Field Timing

The leading edge of HSYNC indicates the beginning of a

horizontal sync interval. If HSYNC is an output, it is asserted

for about 4.7µs. If HSYNC is an input, it must be active for at

least two CLK2 periods. The width of the horizontal

composite sync tip is determined from the video standard

and does not depend on the width of HSYNC.

The leading edge of VSYNC indicates the beginning of a

vertical sync interval. If VSYNC is an output, it is asserted for

3 scan lines in (M, NSM) NTSC and (M, N) PAL modes or

2.5 scan lines in (B, D, G, H, I, CN) PAL modes. If VSYNC is

an input, it must be asserted for at least two CLK2 periods.

When HSYNC and VSYNC are configured as outputs, their

leading edges will occur simultaneously at the start of an

odd field. At the start of an even field, the leading edge of

VSYNC occurs in the middle of the line.

When HSYNC and VSYNC are configured as inputs, the

HMP8154/HMP8156A provides a programmable HSYNC

window for determining FIELD. The window is specified with

respect to the leading or trailing edge of VSYNC. The edge

is selected in the field control register. When HSYNC is

found inside the window, then the encoder sets FIELD to the

value specified in the field control register.

The HMP8154/HMP8156A provides programmable timing

for the VSYNC input. At the active edge of VSYNC, the

encoder resets its vertical half-line counter to the value

specified by the field control register. This allows the input

and output syncs to be offset, although the data must still be

aligned.

The FIELD signal is always an output and changes state

near each leading edge of VSYNC. The delay between the

syncs and FIELD depends on the encoder’s operating mode

as summarized in Table 6. In modes in which the encoder

uses CLK to gate its inputs and outputs, the FIELD signal

may be delayed 0-12 additional CLK2 periods.

Figure 13 illustrates the HSYNC, VSYNC, and FIELD

general timing for (M, NSM) NTSC and (M, N) PAL. Figure

14 illustrates the general timing for (B, D, G, H, I, CN) PAL. In

the figures, all the signals are shown active low (their reset

state), and FIELD is low during odd fields.

TABLE 6. FIELD OUTPUT TIMING

OPERATING MODE

SYNC I/O BLANK I/O CLK2

DIRECTION DIRECTION DELAY

COMMENTS

Input

Input

148 FIELD lags VSYNC switch-

ing from odd to even.

FIELD lags the earlier of

VSYNC and HSYNC when

syncs are aligned when

switching from even to odd.

Input

Output

138 FIELD lags VSYNC.

Output Don’t Care 32 FIELD leads VSYNC.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HMP8156EVAL1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HMP8156EVAL1 | NTSC/PAL Encoders | Intersil Corporation |

| HMP8156EVAL1 | NTSC/PAL Encoder | Intersil Corporation |

| HMP8156EVAL2 | NTSC/PAL Encoders | Intersil Corporation |

| HMP8156EVAL2 | NTSC/PAL Encoder | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |