|

|

PDF HM658512ALTT-7 Data sheet ( Hoja de datos )

| Número de pieza | HM658512ALTT-7 | |

| Descripción | 4 M PSRAM (512-kword x 8-bit) 2 k Refresh | |

| Fabricantes | Hitachi Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HM658512ALTT-7 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

HM658512A Series

4 M PSRAM (512-kword × 8-bit)

2 k Refresh

ADE-203-218C(Z)

Rev. 3.0

Nov. 1997

Description

The Hitachi HM658512A is a CMOS pseudo static RAM organized 512-kword × 8-bit. It realizes higher

density, higher performance and low power consumption by employing 0.8 µm Hi-CMOS process

technology.

It offers low power data retention by self refresh mode. It also offers easy non multiplexed address

interface and easy refresh functions. HM658512A is suitable for handy systems which work with battery

back-up systems.

The device is packaged in a small 525-mil SOP (460-mil body SOP) or a 8 × 20 mm TSOP with thickness

of 1.2 mm, or a 600-mil plastic DIP. High density custom cards made of Tape Carrier Packages are also

available.

Features

• Single 5 V (±10%)

• High speed

Access time

CE access time: 70/80/100 ns (max)

Cycle time

Random read/write cycle time:

115/130/160 ns (min)

• Low power

Active: 250 mW (typ)

Standby: 200 µW (typ)

• Directly TTL compatible

All inputs and outputs

• Simple address configuration

Non multiplexed address

• Refresh cycle

2048 refresh cycles: 32 ms

1 page

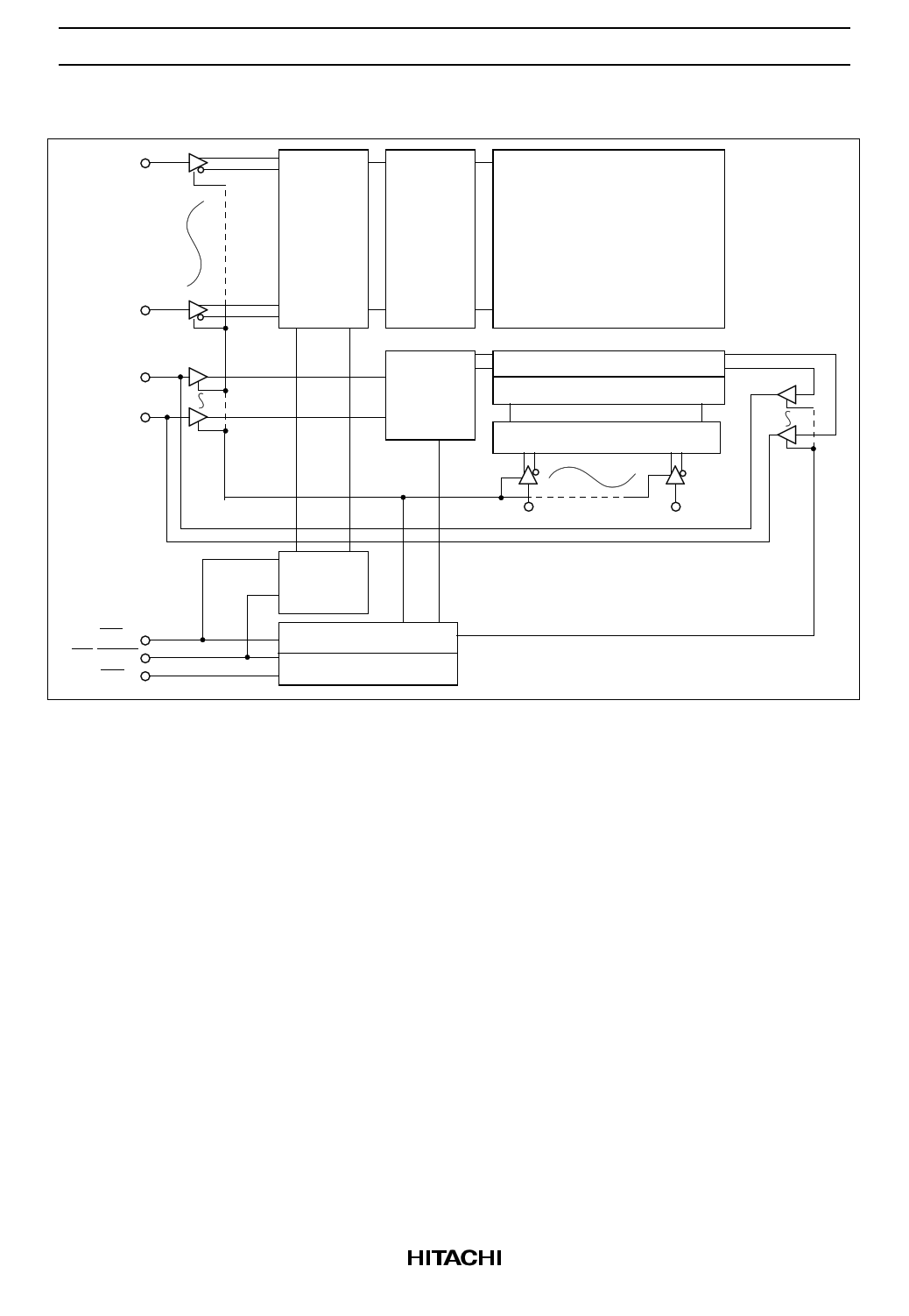

Block Diagram

A0

A10

I/O 0

I/O 7

CE

OE/RFSH

WE

HM658512A Series

Address

Latch

Control

Row

Decoder

Memory Matrix

(2048 × 256) × 8

Input

Data

Control

Column I/O

Column Decoder

Address Latch Control

Refresh

Control

Timing Pulse Gen.

Read Write Control

A11

A18

5

5 Page

HM658512A Series

AC Characteristics (Ta = 0 to +70°C, VCC = 5 V ± 10%, unless otherwise noted.) (cont.)

HM658512A

-7 -8 -10

Parameter

Symbol Min Max Min Max Min Max Unit Notes

Data in to end of write

Data in hold time for write

Output active from end of write

Write to output in high-Z

Transition time (rise and fall)

Refresh command delay time

Refresh precharge time

Refresh command pulse width for

automatic refresh

t DW

t DH

t OW

t WHZ

tT

t RFD

t FP

t FAP

20 —

20 —

25 —

ns

0 — 0 — 0 — ns

5 — 5 — 5 — ns 2

— 20

— 20

— 25

ns 1, 2

3 50 3 50 3 50 ns 6

35 —

40 —

50 —

ns

35 —

40 —

40 —

ns

70 n 8 µ 80 n 8 µ 80 n 8 µ s

Automatic refresh cycle time

Refresh command pulse width for

self refresh

t FC

t FAS

115 —

8—

130 —

8—

160 —

8—

ns

µs

Refresh reset time from self refresh tRFS

Refresh period

t REF

600 —

— 32

600 —

— 32

600 —

— 32

ns 9

ms 2048

cycle

Notes: 1. tCHZ, tOHZ, tWHZ are defined as the time at which the output achieves the open circuit condition.

2. tCHZ, tCLZ, tOHZ, tOLZ, tWHZ and tOW are sampled under the condition of tT = 5 ns and not 100% tested.

3. A write occurs during the overlap of low CE and low WE. Write end is defined at the earlier of

WE going high or CE going high.

4. If the CE low transition occurs simultaneously with or from the WE low transition, the output

buffers remain in high impedance state.

5. In write cycle, OE or WE must disable output buffers prior to applying data to the device and at

the end of write cycle data inputs must be floated prior to OE or WE turning on output buffers.

During this period, I/O pins are in the output state, therefore the input signals of opposite phase

to the outputs must not be applied.

6. Transition time tT is measured between VIH (min) and VIL (max). VIH (min) and VIL (max) are

reference levels for measuring timing of input signals.

7. After power-up, pause for more than 100 µs and execute at least 8 initialization cycles.

8. 2048 cycles of burst refresh or the first cycle of distributed automatic refresh must be executed

within 15 µs after self refresh, in order to meet the refresh specification of 32 ms and 2048

cycles.

9. At the end of self refresh, refresh reset time (tRFS) is required to reset the internal self refresh

operation of the RAM. During tRFS, CE and OE/RFSH must be kept high. If automatic refresh

follows self refresh, low transition of OE/RFSH at the beginning of automatic refresh must not

occur during tRFS period.

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet HM658512ALTT-7.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HM658512ALTT-10 | 4 M PSRAM (512-kword x 8-bit) 2 k Refresh | Hitachi Semiconductor |

| HM658512ALTT-10V | 4 M PSRAM (512-kword x 8-bit) 2 k Refresh | Hitachi Semiconductor |

| HM658512ALTT-7 | 4 M PSRAM (512-kword x 8-bit) 2 k Refresh | Hitachi Semiconductor |

| HM658512ALTT-7V | 4 M PSRAM (512-kword x 8-bit) 2 k Refresh | Hitachi Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |