|

|

PDF 74ACT652SC Data sheet ( Hoja de datos )

| Número de pieza | 74ACT652SC | |

| Descripción | Transceiver/Register | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74ACT652SC (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

August 1999

Revised September 2000

74ACT652

Transceiver/Register

General Description

The ACT652 consists of bus transceiver circuits with D-

type flip-flops, and control circuitry arranged for multiplexed

transmission of data directly from the input bus or from

internal registers. Data on the A or B bus will be clocked

into the registers as the appropriate clock pin goes to the

HIGH logic level. Output Enable pins (OEAB, OEBA) are

provided to control the transceiver function.

Features

s Independent registers for A and B buses

s Multiplexed real-time and stored data

s Outputs source/sink 24 mA

s TTL-compatible inputs

Ordering Code:

Order Number Package Number

Package Description

74ACT652SC

M24B

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74ACT652MTC

MTC24

24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74ACT652SPC

N24C

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

Logic Symbols

Connection Diagram

IEEE/IEC

Pin Descriptions

Pin Names

A0–A7, B0–B7

CPAB, CPBA

SAB, SBA

OEAB, OEBA

Description

A and B Inputs/3-STATE Outputs

Clock Inputs

Select Inputs

Output Enable Inputs

FACT is a trademark of Fairchild Semiconductor Corporation.

© 2000 Fairchild Semiconductor Corporation DS500310

www.fairchildsemi.com

1 page

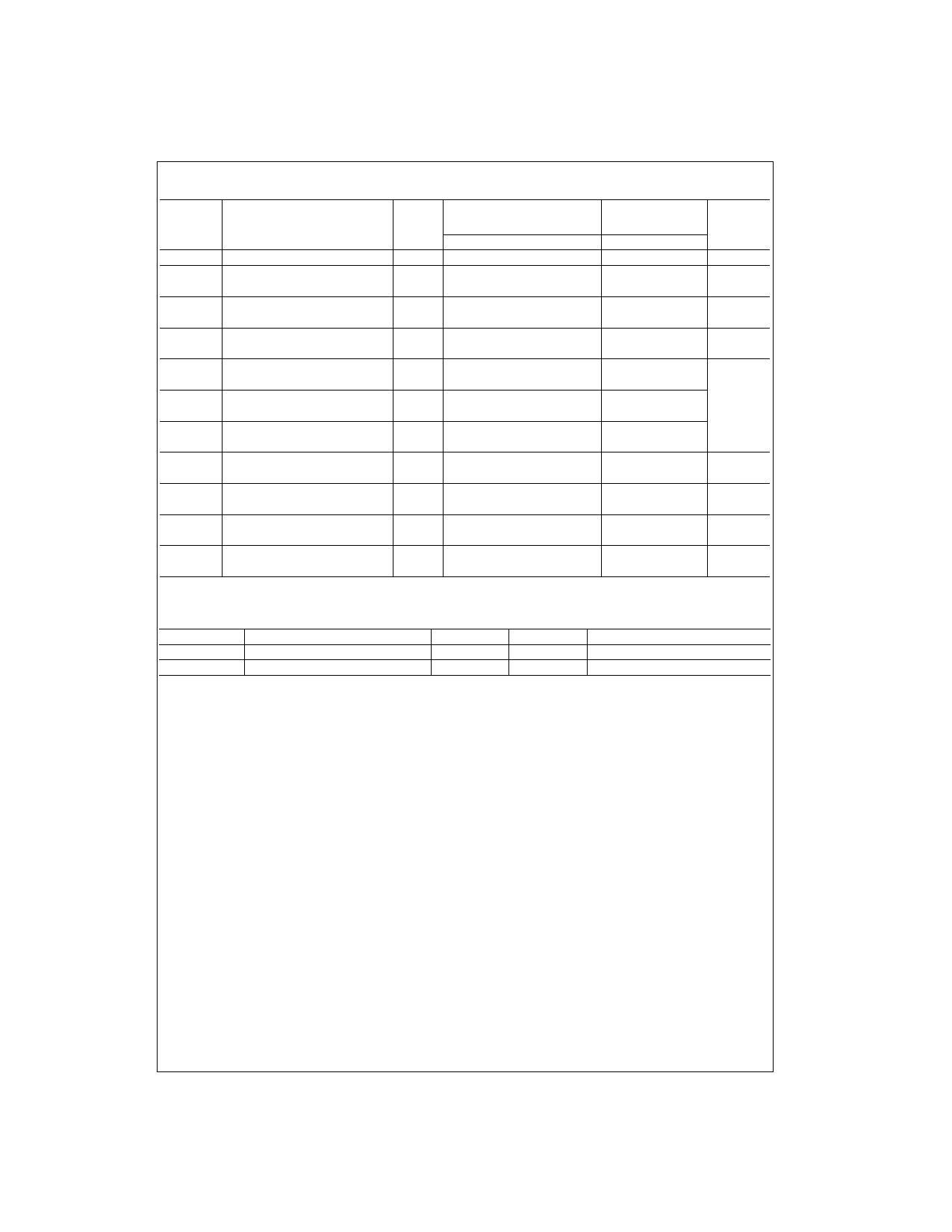

AC Electrical Characteristics

Symbol

Parameter

fMAX

Max. Clock Frequency

tPLH Propagation Delay

tPHL Clock to Bus

tPLH Propagation Delay

tPHL Bus to Bus

tPLH Propagation Delay

tPHL SBA or SAB to A or B

tPZH

Enable Time

tPZL OEBA to A (Note 5)

tPHZ Disable Time

tPLZ OEBA to A (Note 5)

tPZH

Enable Time

tPZL OEAB to B

tPHZ Disable Time

tPLZ OEAB to B

ts(H)

Setup Time, HIGH or

ts(L) LOW, Bus to Clock

th(H)

Hold Time, HIGH or

th(L)

LOW, Bus to Clock

tw(H)

Clock Pulse Width

tw(L)

HIGH or LOW

Note 5: Voltage Range 5.0 is 5.0V ± 0.5V.

VCC

(V)

(Note 5)

5.0

5.0

5.0

5.0

5.0

5.0

5.0

5.0

5.0

5.0

5.0

Capacitance

Symbol

CIN

CPD

Parameter

Input Capacitance

Power Dissipation Capacitance

TA = +25°C

CL = 50 pF

Min Typ Max

TA = −40°C to +85°C

CL = 50 pF

Min Max

2.0 7.0 9.5 2.0 10.0

2.0 6.5 9.0 2.0 9.5

2.5 6.5 10.0 2.5 10.5

2.0 7.0 10.5 2.0 11.0

1.0 5.0 8.0 1.0 8.5

2.0 7.0 10.5 2.0 11.0

1.0 5.0 8.0 1.0 8.5

3.0 3.0

1.5 1.5

4.0 4.0

Units

MHz

ns

ns

ns

ns

ns

ns

ns

ns

Typ Units

Conditions

4.5 pF VCC = 5.0V

54 pF VCC = 5.0V

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet 74ACT652SC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74ACT652SC | Transceiver/Register | Fairchild Semiconductor |

| 74ACT652SPC | Transceiver/Register | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |