|

|

PDF S3FB018 Data sheet ( Hoja de datos )

| Número de pieza | S3FB018 | |

| Descripción | The S3CB018/FB018 single-chip CMOS microcontroller | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S3FB018 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S3CB018/FB018

PRODUCT OVERVIEW

1 PRODUCT OVERVIEW

CALMRISC OVERVIEW

The S3CB018/FB018 single-chip CMOS microcontroller is designed for high performance using Samsung’ s

newest 8-bit CPU core, CalmRISC.

CalmRISC is an 8-bit low power RISC microcontroller. Its basic architecture follows Harvard style, that is, it has

separate program memory and data memory. Both instruction and data can be fetched simultaneously without

causing a stall, using separate paths for memory access. Represented below is the top block diagram of the

CalmRISC microcontroller.

1-1

1 page

S3CB018/FB018

PRODUCT OVERVIEW

/ 1 IF ID/MEM EXE/WB

/ 2 IF ID/MEM EXE/WB

/ 3 IF ID/MEM EXE/WB

/ 4 IF

IF ID/MEM EXE/WB

/ 5 IF ID/MEM EXE/WB

/ 6 IF ID/MEM EXE/WB

Figure 1-3. CalmRISC Pipeline Stream Diagram

Most CalmRISC instructions are 1-word instructions, while same branch instructions such as “LCALL” and “LJT”

instructions are 2-word instructions. In Figure 1-3, the instruction, I4, is a long branch instruction and it takes two

clock cycles to fetch the instruction. As indicated in the pipeline stream, the number of clocks per instruction (CPI)

is 1 except for long branches, which take 2 clock cycles per instruction.

1-5

5 Page

S3CB018/FB018

PRODUCT OVERVIEW

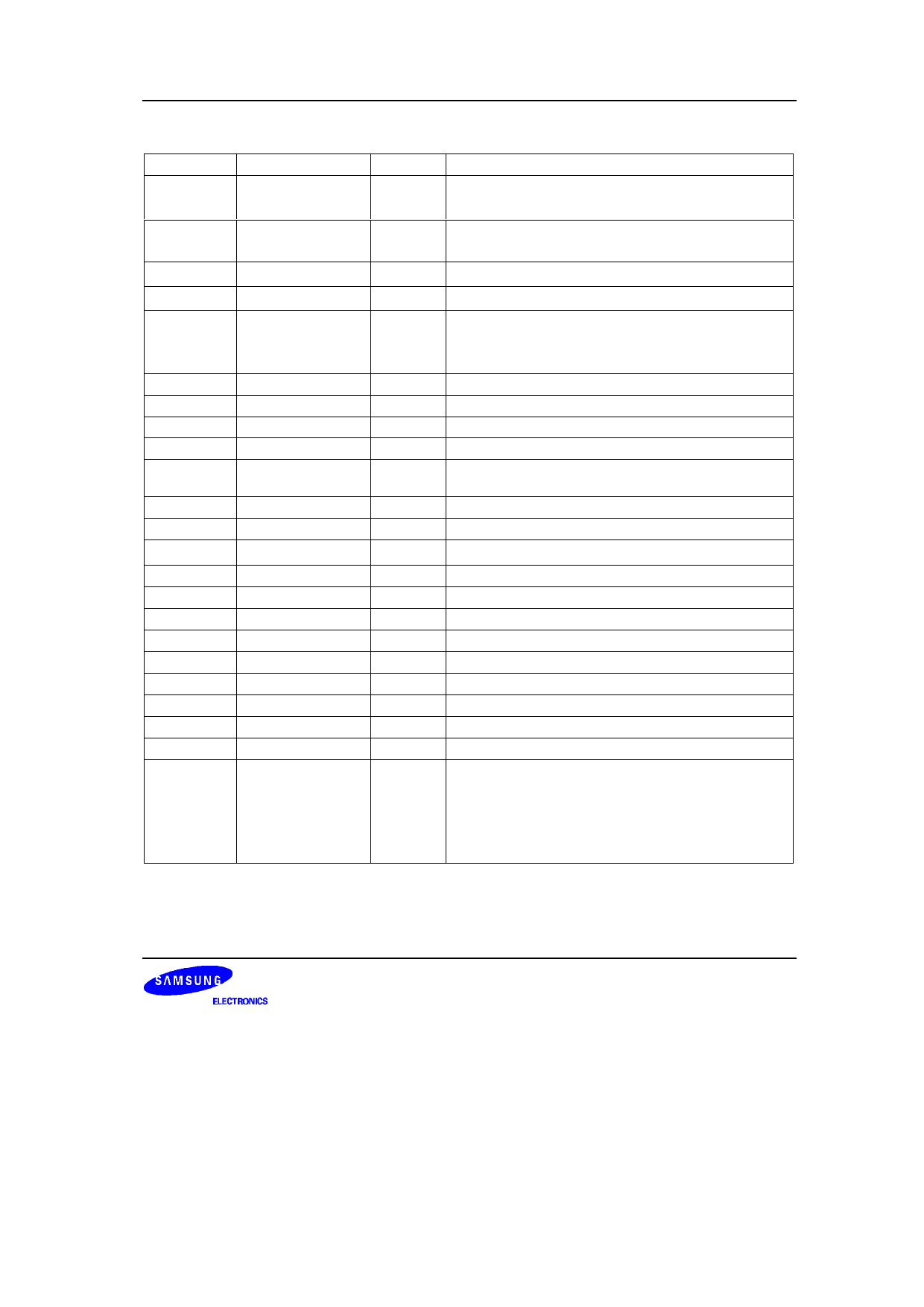

No.

1-3

5-9

12-15

17-20

22

23

25-27

29, 30

32, 34

36, 37

39

40

41

42

44

45

46

47

49

50

51

52

54

55

56

57

59, 60

62-64

66-68

70-73

75-78

Table 1-4. Evaluation Chip Pin Descriptions

Pin Name

P0.0-P0.2

P0.3-P0.7

Pin Type

I/O Port 0

Description

P1.0-P1.3

P1.4-P1.7

XIN

XOUT

P2.0-P2.2

P2.3, P2.4

P2.5-P2.7

P3.0, P3.1

TMODE

PIN_RESB

JTAGSEL

PNTRST_STSTEINI

T

PTCK_MCLK

PTMS

PTDI_RXD

O Port 1

I Clock In

O Clock Out

I/O Port 2

I/O Port 3

I Test Mode pin; 1: skip warm-up time, 0: normal mode

I Asynchronous reset, active low

I JTAG mode select; 1: parallel, 0: serial

I JTAG/UART pin

I JTAG/UART pin

I JTAG/UART pin

I JTAG/UART pin

PTDO_TXD

NPMWE

NPMOE

NPMCS

RUNST

OUTDIS

DOCNTX

XDOCNTX

NPM64KW

PD15-PD14

PD13-PD11

PD10-PD8

PD7-PD4

PD3-PD0

O JTAG/UART pin

O Program Memory Write Enable, active low

O Program Memory Output Enable, active low

O Program Memory Chip Select, active low

O Run Status Indicator

I I/O PAD Disable for debugger

I Data Bus Output Control

I External X-Memory Data Bus Output Control

I Up to 64KW Program Memory, active low

I/O Program Memory Data Bus

1-11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S3FB018.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S3FB018 | The S3CB018/FB018 single-chip CMOS microcontroller | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |