|

|

PDF S5T8808A Data sheet ( Hoja de datos )

| Número de pieza | S5T8808A | |

| Descripción | PLL FREQUENCY SHNTHESIZER FOR PAGER | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S5T8808A (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

PLL FREQUENCY SHNTHESIZER FOR PAGER

S5T8808A

INTRODUCTION

S5T8808A is a superior low-power-programmable PLL frequency

synthesizer which can be used in a high performance Wide Area

Pager system.

S5T8808A consists of 2 kinds of divider block including a 17bit Shift

register, 16-bit Latch, 14/16-bits Counter, Prescaler, and a phase

detector block including a Phase detector, Lock detector and a

Charge pump.

16−TSSOP−0044

FEATURES

( Magnification = 1 : 4 )

• Maximum operating frequency:

120MHz @ 500mVP-P, VDD1 = 0.95V, VDD2 = 3.0V

165MHz @ 500mVP-P, VDD1 = 1.0V, VDD2 = 3.0V

• On-chip reference oscillator supports external crystal which oscillates up to 18MHz

• Superior supply current:

FFIN = 90MHz, IDD1 = 0.6mA (Typ.) @ VDD1 = 1.0V, VDD2 = 3.0V

FFIN = 150MHz, IDD1 = 0.9mA (Typ.) @ VDD1 = 1.0V, VDD2 = 3.0V

• Operating voltage: VDD1 = 0.95 ~ 2.0V and VDD2 = 2.0 ~ 3.3V

• Reference frequency counter divider range: 1 / 28 ~ 1 / 65532 (Multiple 4)

But, the Divider range with FRC_High state: 1 / 7 ~ 1 / 16383

• RX frequency counter divider range: 1 / 28 ~ 1 / 65535

• Package type: 16−TSSOP (0.65mm)

ORDERING INFORMATION

Device

+S5T8808A01-R0B0

+: New Product

Package

16−TSSOP−0044

Operating Temperature

−25°C to +75°C

1

1 page

PLL FREQUENCY SHNTHESIZER FOR PAGER

S5T8808A

ABSOLUTE MAXIMUM RATINGS

Characteristic

Supply Voltage

Input Voltage

Power Dissipation

Operating Temperature

Storage Temperature

Symbol

VDD ~ VDD2

VI

PD

TOPR

TSTG

Value

−0.3 ~ +4.0

VSS − 0.3 ~ VDD + 0.3

350

−25 ~ +75

−40 ~ +125

Unit

V

V

mW

°C

°C

ELECTRICAL CHARACTERISTICS

(Ta = 25°C, VDD1 = 1.0V, VDD2 = 3.0V, unless otherwise specified)

Characteristic

Operating voltage

Operating current

Standby current

Input Voltage

(DATA, CLK, EN, BS)

Input current

(Fin, Xin)

Input frequency

Output current

(PDA, PDP)

Output current

(Fr, Fn, LDT)

Setup-time

(DATA-CLK, CLK-EN)

Hold time

Symbol

Test Conditions

VDD1

VDD2

IDD1

IDD2

ISB

VIL

VIH

VIH

VIL

FFIN

FOSCI

IOH1

IOL1

IOH2

IOL2

ts

−

−

FOSCI = 12.8MHz

@ 0.3VP-P

VDD1 = 1.0V

VDD2 = 1.0V

FFIN = 90MHz

FFIN = 150MHz

VDD1 = 0V, VDD2 = 3.0V

−

−

VIH = VDD1

VIL = 0V

FFIN = 0.5VP-P

VDD1 = 0.95V

VDD1 = 1.0V

VOSCI = 0.5VP-P

VOH = 0.4V

VOL = VDD1 - 0.4V

VOH = 0.4V

VOL = VDD1 - 0.4V

−

tH −

Min.

0.95

2.0

−

−

Typ.

1.0

3.0

0.6

0.9

Max.

2.0

3.3

−

−

Unit

V

mA

−

−

VDD3-0.3

−

−

−

−

7

1.0

1.0

0.1

0.1

2

−

−

−

−

−

−

−

−

−

−

−

−

−

2−

10 µA

0.3 V

−

20 µA

20

120 MHz

165

18

− mA

−

− mA

−

− µS

− µS

5

5 Page

PLL FREQUENCY SHNTHESIZER FOR PAGER

S5T8808A

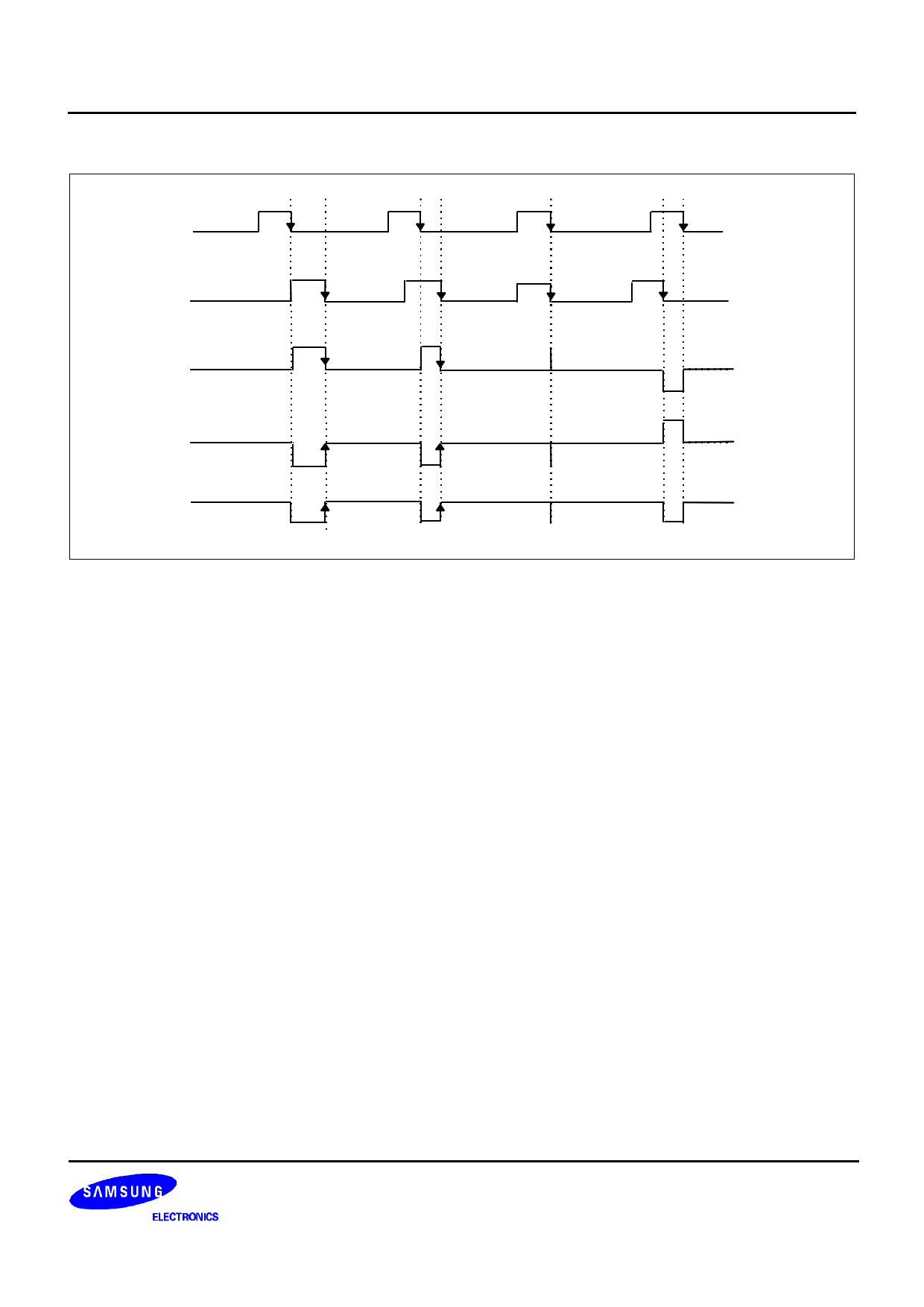

Fr

Fn

PDP

PDA

LD

GND

VDD1

Figure 6. Phase Detector / Lock Detector Output Waveforms

NOTES:

1. Phase detector always compares the Phase difference of N-counter with R-counter, and set to High or Low state as

much as the phase difference.

2. The LD output set to Low level same as Phase detector error width.

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet S5T8808A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S5T8808 | PLL FREQUENCY SHNTHESIZER FOR PAGER | Samsung semiconductor |

| S5T8808A | PLL FREQUENCY SHNTHESIZER FOR PAGER | Samsung semiconductor |

| S5T8808A01-R0B0 | PLL FREQUENCY SHNTHESIZER FOR PAGER | Samsung semiconductor |

| S5T8808X01-V0B0 | PLL FREQUENCY SHNTHESIZER FOR PAGER | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |