|

|

PDF SAA7186 Data sheet ( Hoja de datos )

| Número de pieza | SAA7186 | |

| Descripción | Digital video scaler | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SAA7186 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA7186

Digital video scaler

Preliminary specification

File under Integrated Circuits, IC22

May 1993

1 page

Philips Semiconductors

Digital video scaler

Preliminary specification

SAA7186

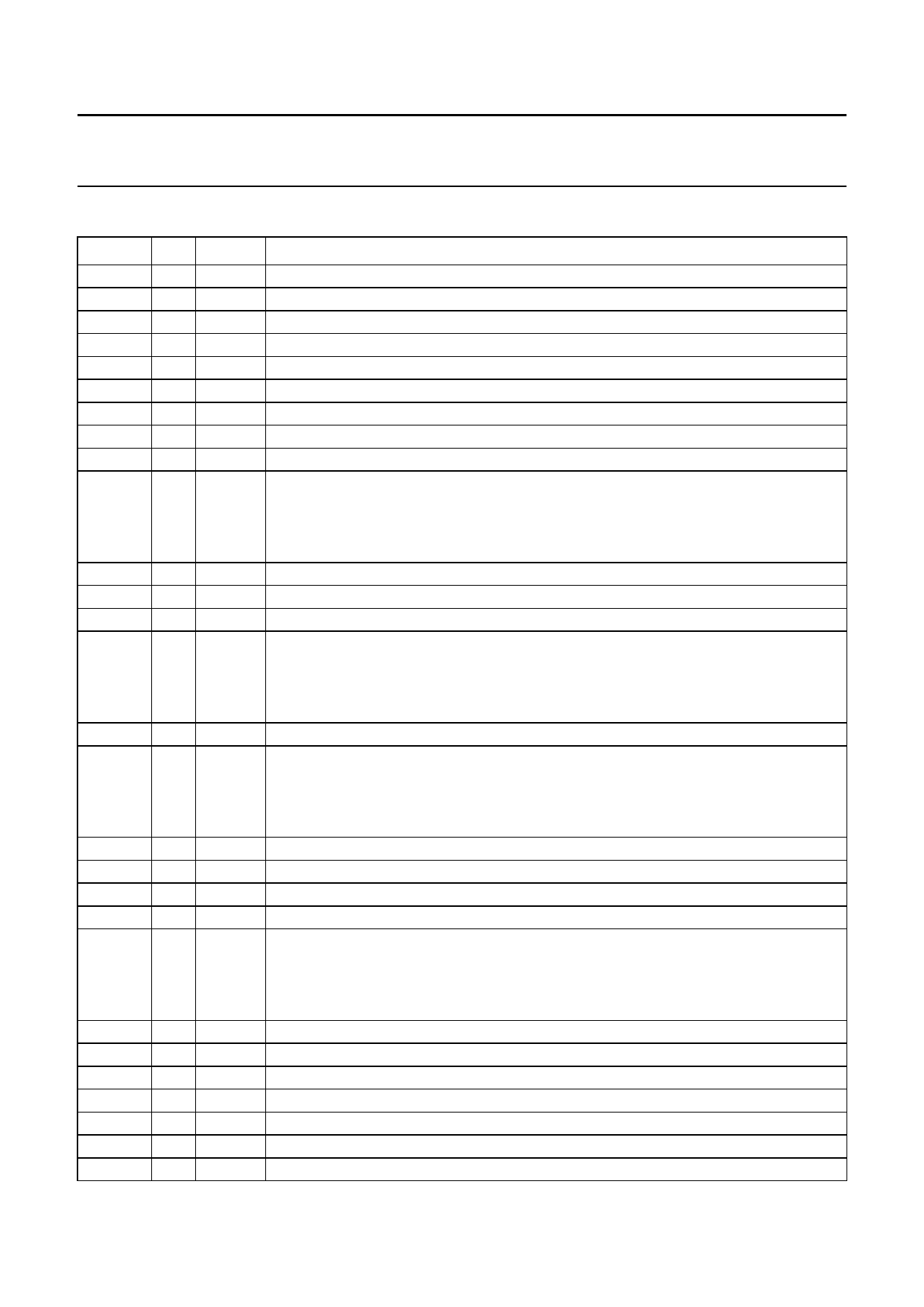

6 PINNING

SYMBOL PIN STATUS

DESCRIPTION

LNQ

1O

line qualifier signal; active polarity defined by QPL-bit in “10” (VCLK strobed)

HREFD 2 O

delay-compensated HREF output signal (VCLK strobed)

VSS1

i.c.

VDD1

i.c.

3−

4−

5−

6−

GND1 (0 V)

internally connected

+5 V supply voltage 1

internally connected

SP 7 I

connected to ground (shift pin for testing)

AP 8 I

connected to ground (action pin for testing)

n.c. 9 −

not connected

UVIN0 10 I

UVIN1

UVIN2

11 I

12 I

time-multiplexed colour-difference input data (bits 0 to 3)

UVIN3

VDD2

n.c.

VSS2

UVIN4

13 I

14 −

15 −

16 −

17 I

+5 V supply voltage 2

not connected

GND2 (0 V)

UVIN5

UVIN6

18 I

19 I

time-multiplexed colour-difference input data (bits 4 to 7)

UVIN7 20 I

n.c. 21 −

not connected

YIN0

22 I

YIN1

YIN2

23 I

24 I

luminance input data (bits 0 to 3)

YIN3

VDD3

n.c.

VSS3

n.c.

25 I

26 −

27 −

28 −

29 −

+5 V supply voltage 3

not connected

GND3 (0 V)

not connected

YIN4

30 I

YIN5

YIN6

31 I

32 I

luminance input data (bits 4 to 7)

YIN7

33 I

n.c.

CREF

34 −

35 I

not connected

clock reference, external sync signal

LLC 36 I

line-locked system clock input signal (twice of pixel rate)

HREF 37 I

horizontal reference, pixel data clock signal (also present during vertical blanking)

VS 38 I

vertical sync input signal (approximately 6 lines long)

n.c.

VDD4

39 −

40 −

not connected

+5 V supply voltage 4

May 1993

5

5 Page

Philips Semiconductors

Digital video scaler

Preliminary specification

SAA7186

shorter than XS, processing is aborted when the falling

edge of HREF is detected.

Vertical regions in Fig.4:

• the two regions can be programmed via I2C-bus,

whereby regions should not overlap (active region

overrides the bypass region).

• the start of a normal active picture depends on video

standard and has to be programmed to the correct

value.

• the offsets XO and YO have to be set according to the

internal processing delays to ensure the complete

number of destination pixels and lines (Table 6).

• the scaling parameters can be used to perform a

panning function over the video frame/field.

handbook, full pagewidth

LLC

CREF

HREF

Byte numbers for pixles:

Y signal

U and V signal

start of

active line

01 2 3 4 5 6 7

U0 V0 U2 V2 U4 V4 U6 V6

MEH411

handbook, full pagewidth

LLC

CREF

HREF

Byte number for pixels:

Y signal

n–5

U and V signal

Un-5

n–4

Vn-5

n–3

Un-3

n–2

Vn-3

end of

active line

n–1

n

Un-1

Vn-1

May 1993

Fig.3 Horizontal and data multiplex timing.

11

MEH410

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SAA7186.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA7182 | Digital Video Encoder EURO-DENC | NXP Semiconductors |

| SAA7182A | Digital Video Encoder EURO-DENC2 | NXP Semiconductors |

| SAA7182AWP | Digital Video Encoder EURO-DENC2 | NXP Semiconductors |

| SAA7182AWP | Digital Video Encoder EURO-DENC2 | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |