|

|

PDF W133 Data sheet ( Hoja de datos )

| Número de pieza | W133 | |

| Descripción | Spread Spectrum System Frequency Synthesizer | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de W133 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

PRELIMINARY

W133

Spread Spectrum System Frequency Synthesizer

Features

• Maximized EMI suppression using Cypress’s spread

spectrum technology

• Intel CK98 Specification compliant

• 0.5% downspread outputs deliver up to 10 dB lower EMI

• Four skew-controlled copies of CPU output

• Eight copies of PCI output (synchronous w/CPU output)

• Four copies of 66-MHz fixed frequency 3.3V clock

• Two copies of CPU/2 outputs for synchronous memory

reference

• Three copies of 16.67-MHz IOAPIC clock, synchronous

to CPU clock

• One copy of 48-MHz USB output

• Two copies of 14.31818-MHz reference clock

• Programmable to 133- or 100-MHz operation

• Power management control pins for clock stop and shut

down

• Available in 56-pin SSOP

Key Specifications

Supply Voltages: ...................................... VDDQ3 = 3.3V±5%

VDDQ2 = 2.5V±5%

Block Diagram

CPU Output Jitter: ...................................................... 250 ps

CPUdiv2 Output Jitter:.................................................250 ps

48 MHz, 3V66, PCI, IOAPIC Output Jitter: .................. 500 ps

CPU0:3, CPUdiv2_ 0:1 Output Skew: ......................... 175 ps

PCI_F, PCI1:7 Output Skew: .......................................500 ps

3V66_0:3, IOAPIC0:2 Output Skew; ...........................250 ps

CPU to 3V66 Output Offset: ............. 0.0–1.5 ns (CPU leads)

3V66 to PCI Output Offset:.............. 1.5–4.0 ns (3V66 leads)

CPU to IOAPIC Output Offset: ......... 1.5–4.0 ns (CPU leads)

Logic inputs, except SEL133/100#, have 250-kΩ pull-up

resistors.

Table 1. Pin Selectable Frequency[1]

SEL133/100#

CPU0:3 (MHz)

PCI

1

133 MHz

33.3 MHz

0

100 MHz

33.3 MHz

Note:

1. See Table 2 for complete mode selection details.

Pin Configuration

X1

X2

CPU_STOP#

SPREAD#

SEL0

SEL1

SEL133/100#

PWRDWN#

PCI_STOP#

XTAL

OSC

2

REF0:1

PLL 1

Power

Down

Logic

STOP

Clock

Logic

÷2

÷2/÷1.5

STOP

Clock

Logic

STOP

÷2 Clock

Logic

÷2

4

CPU0:3

2

CPUdiv2_0:1

4

3V66_0:3

1

PCI_F

7

PCI1:7

3

IOAPIC0:2

GND

REF0

REF1

VDDQ3

X1

X2

GND

PCI_F

PCI1

VDDQ3

PCI2

PCI3

GND

PCI4

PCI5

VDDQ3

PCI6

PCI7

GND

GND

3V66_0

3V66_1

VDDQ3

GND

3V66_2

3V66_3

VDDQ3

SEL133/100#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56 VDDQ2

55 IOAPIC2

54 IOAPIC1

53 IOAPIC0

52 GND

51 VDDQ2

50 CPUdiv2_1

49 CPUdiv2_0

48 GND

47 VDDQ2

46 CPU3

45 CPU2

44 GND

43 VDDQ2

42 CPU1

41 CPU0

40 GND

39 VDDQ3

38 GND

37 PCI_STOP#

36 CPU_STOP#

35 PWRDWN#

34 SPREAD#

33 SEL1

32 SEL0

31 VDDQ3

30 48MHz

29 GND

Three-state

Logic

PLL2

1

48MHz

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

October 13, 1999, rev. **

1 page

PRELIMINARY

W133

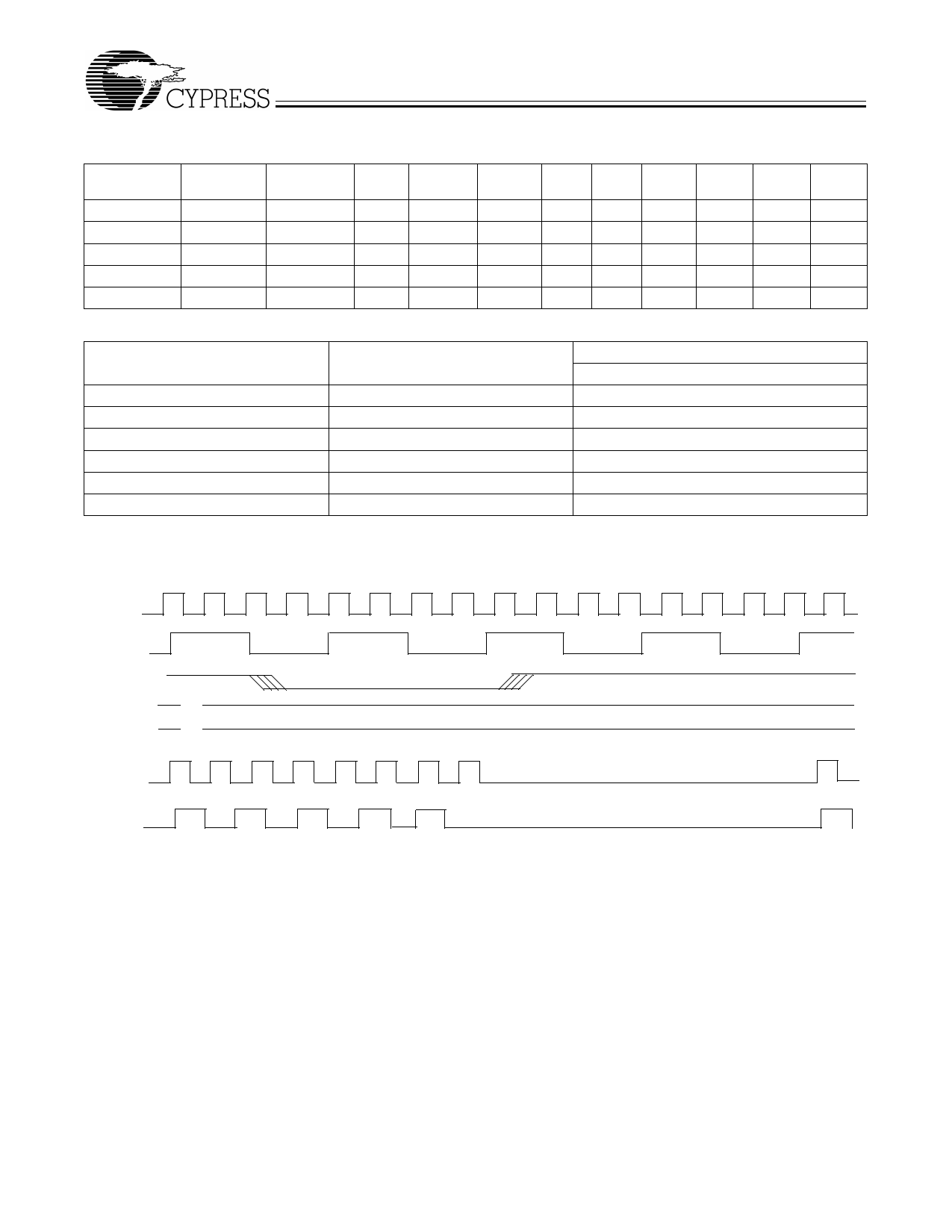

Table 5. Clock Enable Configuration[9, 10, 11, 12, 13, 14]

CPU_STOP# PWRDWN# PCI_STOP# CPU CPUdiv2 IOAPIC

X

0

X

LOW LOW

LOW

0

1

0

LOW

ON

ON

0

1

1

LOW

ON

ON

1

1

0

ON ON

ON

1

1

1

ON ON

ON

Table 6. Power Management State Transition[15, 16]

3V66

LOW

LOW

LOW

ON

ON

PCI

LOW

LOW

ON

LOW

ON

PCI_F

LOW

ON

ON

ON

ON

REF,

48MHz

LOW

ON

ON

ON

ON

OSC.

OFF

ON

ON

ON

ON

VCOs

OFF

ON

ON

ON

ON

Signal

CPU_STOP#

PCI_STOP#

PWRDWN#

Signal State

0 (disabled)

1 (enabled)

0 (disabled)

1 (enabled)

1 (normal operation)

0 (power down)

Latency

No. of rising edges of PCI Clock

1

1

1

1

3 ms

2 max.

Timing Diagrams

CPU_STOP# Timing Diagram[17, 18, 19, 20, 21, 22]

CPU

(internal)

PCI

CPU_STOP#

PCI_STOP#

PWRDWN#

HI

HI

CPU

(external)

3V66

Notes:

9. LOW means outputs held static LOW as per latency requirement below.

10. ON means active.

11. PWRDWN# pulled LOW, impacts all outputs including REF and 48-MHz outputs.

12. All 3V66 as well as all CPU clocks stop cleanly when CPU_STOP# is pulled LOW.

13. CPUdiv2, IOAPIC, REF, 48MHz signals are not controlled by the CPU_STOP# functionality and are enabled in all conditions except PWRDWN#=LOW.

14. An “x” indicates a “don’t care” condition.

15. Clock on/off latency is defined in the number of rising edges of the free-running PCI clock between when the clock disable goes LOW/HIGH to when the first

valid clock comes out of the device.

16. Power up latency is from when PWRDWN# goes inactive (HIGH) to when the first valid clocks are driven from the device.

17. All internal timing is referenced to the CPU clock.

18. The internal label means inside the chip and is a reference only. This in fact may not be the way that the control is designed.

19. CPU_STOP# signal is an input signal that must be made synchronous to free-running PCI_F.

20. 3V66 clocks also stop/start before.

21. PWRDWN# and PCI_STOP# are shown in a HIGH state.

22. Diagrams shown with respect to 133 MHz. Similar operation when CPU clock is 100 MHz.

5

5 Page

PRELIMINARY

W133

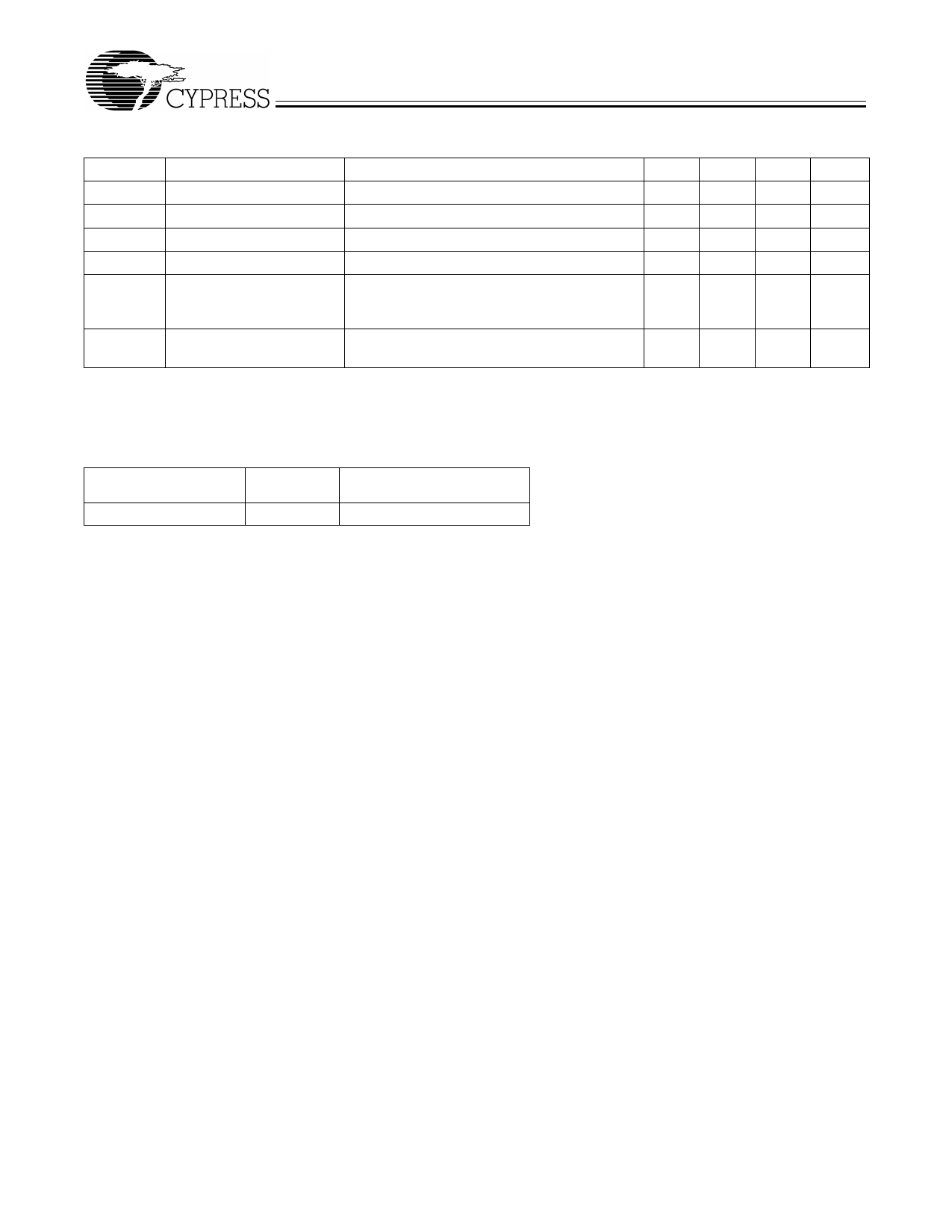

IOAPIC Clock Outputs, IOAPIC0:2 (Lump Capacitance Test Load = 20 pF)

Parameter

Description

Test Condition/Comments

f Frequency

Note 38

tR Output Rise Edge Rate Measured from 0.4V to 2.0V

tF

Output Fall Edge Rate

Measured from 2.0V to 0.4V

tD Duty Cycle

Measured on rising and falling edge at 1.25V

fST Frequency Stabilization Assumes full supply voltage reached within

from Power-up (cold start) 1 ms from power-up. Short cycles exist prior to

frequency stabilization.

Zo

AC Output Impedance

Average value during switching transition. Used

for determining series termination value.

Note:

38. IOAPIC clock is CPU/8 for CPU = 133 MHz and CPU/6 for CPU = 100 MHz.

Min

1

1

45

Typ

16.67

20

Max

4

4

55

3

Unit

MHz

V/ns

V/ns

%

ms

Ω

Ordering Information

Ordering Code

Package

Name

W133

H

Package Type

56-pin SSOP (300 mils)

Intel is a registered trademark of Intel Corporation.

Document #: 38-00823

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet W133.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W130 | Spread Spectrum Desktop/Notebook System Clock | Cypress Semiconductor |

| W13009 | STW13009 | STMicroelectronics |

| W130L | Sensick | Sick |

| W132 | Spread Aware/ Ten/Eleven Output Zero Delay Buffer | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |