|

|

PDF W83194BR-730 Data sheet ( Hoja de datos )

| Número de pieza | W83194BR-730 | |

| Descripción | 166MHZ CLOCK FOR SIS CHIPSET | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W83194BR-730 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

W83194BR-730

166MHZ CLOCK FOR SIS CHIPSET

1.0 GENERAL DESCRIPTION

The W83194BR-730 is a Clock Synthesizer which provides all clocks required for high-speed RISC or

CISC microprocessor such as AMD K7. W83194BR-730 provides 64 CPU/PCI frequencies which are

selectable with smooth transitions by hardware or software. W83194BR-730 also provides 13 SDRAM

clocks.

The W83194BR-730 provides step-less frequency programming by controlling the VCO freq. and the

programmable PCI clock output divisor ratio. A watch dog timer is quipped and when time out, the

RESET# pin will output 4ms pulse signal.

The W83194BR-730 accepts a 14.318 MHz reference crystal as its input. Spread spectrum built in at

0~-0.5% or ±0.25% to reduce EMI. Programmable stopping individual clock outputs and frequency

selection through I2C interface. The device meets the Pentium power-up stabilization, which requires

CPU and PCI clocks be stable within 2 ms after power-up. Using dual function pin for the slots(ISA, PCI,

CPU, DIMM) is not recommend.

2.0 PRODUCT FEATURES

• Supports AMD CPU with I2C.

• 3 CPU clocks (one free-running CPU clock)

• 13 SDRAM clocks for 3 DIMMs

• 6 PCI synchronous clocks

• 2 AGP clocks

• 2 REF clocks as 14.318MHz outputs

• < 250ps skew among CPU and SDRAM clocks

• < 250ps skew among PCI clocks

• Skew from CPU(earlier) to PCI clock 1 to 4ns, center 2.6ns.

• Smooth frequency switch with selections from 66 MHz to 200 MHz CPU

• Stepless frequency programming by controlling the VCO freq. and the clock output divisor ratio

• Programmable skew for CPU to SDRAM and CPU to AGP clock outputs

• I2C 2-Wire serial interface and I2C read back

• ±0.25% or 0~-0.5% spread spectrum function to reduce EMI

• Programmable registers to enable/stop each output and select modes

• MODE pin for power Management and RESET# out when system hang

• One 48 MHz for USB & one 24_48 MHz for super I/O

• 48-pin SSOP package

Publication Release Date: Oct. 2000

- 1 - Revision 0.60

1 page

W83194BR-730

PRELIMINARY

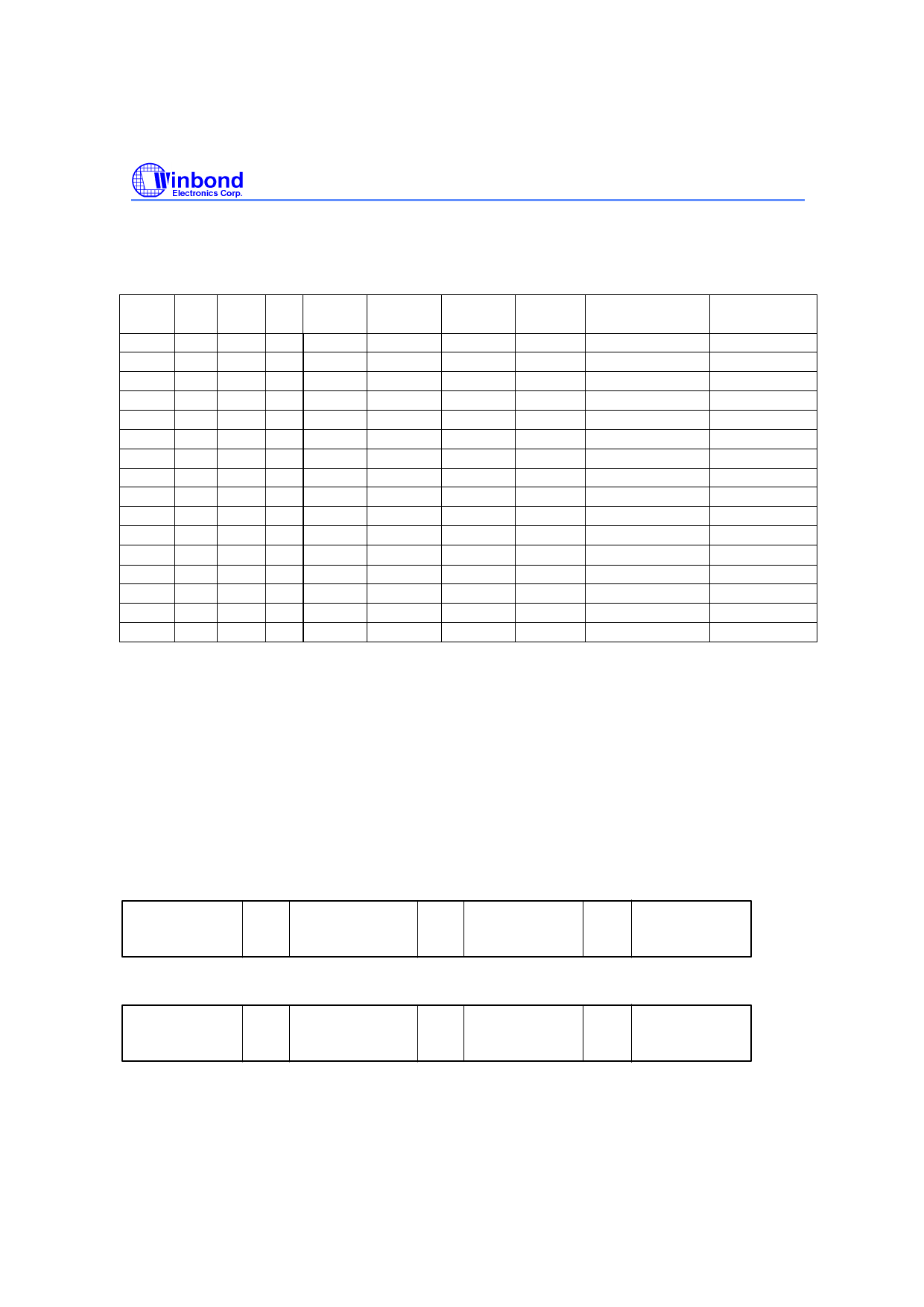

5.0 FREQUENCY SELECTION BY HARDWARE

VCO

FS3 FS2 FS1 FS0 (MHz)

0 0 0 0 400

0 0 0 1 400

0 0 1 0 300

0 0 1 1 400

0 1 0 0 336

0 1 0 1 500

0 1 1 0 372

0 1 1 1 400

1 0 0 0 400

1 0 0 1 300

1 0 1 0 333

1 0 1 1 330

1 1 0 0 332

1 1 0 1 360

1 1 1 0 192

1 1 1 1 192

CPU

(MHz)

100

100

100

100

112

125

124

133

133

150

111

110

166

90

48

45

SDRAM

(MHz)

100

133

150

66.6

112

100

124

100

133

150

166

165

166

90

48

60

PCI

(MHz)

33.3

33.3

30.0

33.3

33.6

31.3

31

33.3

33.3

30

33.3

33.0

33.3

30

32

30

AGPSEL=0

(MHz)

66.6

66.6

60

66.6

67.2

62.5

62

66.6

66.6

60

66.6

66

66.6

60

64

60

AGPSEL=1

(MHz)

50

50

50

50

56

50

46.5

50

50

50

55.6

55

55.6

45

48

45

6.0 SERIAL CONTROL REGISTERS

The Pin column lists the affected pin number and the @PowerUp column gives the default state at true

power up. "Command Code" byte and "Byte Count" byte must be sent following the acknowledge of

the Address Byte. Although the data (bits) in these two bytes are considered "don't care", they must be

sent and will be acknowledge. After that, the sequence described below (Register 0, Register 1,

Register 2, ....) will be valid and acknowledged.

Bytes sequence order for I2C controller :

Clock Address

A(6:0) & R/W

Ack

8 bits dummy

Command code

Ack

8 bits dummy

Byte count

Ack

Byte0,1,2...

until Stop

Set R/W to 1 when Read back”, the data sequence is as follows :

Clock Address

A(6:0) & R/W

Ack

Byte 0

Ack Byte 1

Ack

Byte2, 3, 4...

until Stop

Publication Release Date:Oct. 2000

- 5 - Revision 0.60

5 Page

W83194BR-730

5.10 Register 9: Spread Spectrum Register

Bit @PowerUp Pin

Description

7 0 - Spread spectrum up count 3

6 0 - Spread spectrum up count 2

5 0 - Spread spectrum up count 1

4 0 - Spread spectrum up count 0

3 0 - Spread spectrum down count 3

2 0 - Spread spectrum down count 2

1 0 - Spread spectrum down count 1

0 0 - Spread spectrum down count 0

PRELIMINARY

5.11 Register 10: Divisor Register

Bit @PowerUp Pin

Description

7 0 - 0: use frequency table

1: use M/N register to program frequency

The equation is VCO freq. = 14.318MHz * (N+4)/ M

6 X - Ratio SEL3 (See ratio selection table)

5 X - Ratio SEL2 (See ratio selection table)

4 X - Ratio SEL1 (See ratio selection table)

3 X - Ratio SEL0 (See ratio selection table)

2 X - AGP Ratio SEL2 (See ratio selection table1)

1 X - AGP Ratio SEL1 (See ratio selection table1)

0 X - AGP Ratio SEL0 (See ratio selection table1)

5.12 Register 11: Winbond Chip ID Register (Read Only)

Bit @PowerUp Pin

7 0 - Winbond Chip ID

6 0 - Winbond Chip ID

5 0 - Winbond Chip ID

4 0 - Winbond Chip ID

3 0 - Winbond Chip ID

2 1 - Winbond Chip ID

1 0 - Winbond Chip ID

0 1 - Winbond Chip ID

Description

- 11 -

Publication Release Date:Oct. 2000

Revision 0.60

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet W83194BR-730.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W83194BR-730 | 166MHZ CLOCK FOR SIS CHIPSET | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |