|

|

PDF 74LVC4066 Data sheet ( Hoja de datos )

| Número de pieza | 74LVC4066 | |

| Descripción | Quad bilateral switches | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LVC4066 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

74LVC4066

Quad bilateral switch

Rev. 5 — 23 November 2011

Product data sheet

1. General description

The 74LVC4066 is a high-speed Si-gate CMOS device.

The 74LVC4066 provides four single pole, single-throw analog switch functions. Each

switch has two input/output terminals (nY and nZ) and an active HIGH enable input (nE).

When nE is LOW, the analog switch is turned off.

Schmitt-trigger action at the enable inputs makes the circuit tolerant of slower input rise

and fall times across the entire VCC range from 1.65 V to 5.5 V.

2. Features and benefits

Wide supply voltage range from 1.65 V to 5.5 V

Very low ON resistance:

7.5 (typical) at VCC = 2.7 V

6.5 (typical) at VCC = 3.3 V

6 (typical) at VCC = 5 V

Switch current capability of 32 mA

High noise immunity

CMOS low-power consumption

Direct interface TTL-levels

Latch-up performance exceeds 250 mA

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-A exceeds 200 V

Enable inputs accept voltages up to 5 V

Multiple package options

Specified from 40 C to +85 C and 40 C to +125 C

1 page

NXP Semiconductors

74LVC4066

Quad bilateral switch

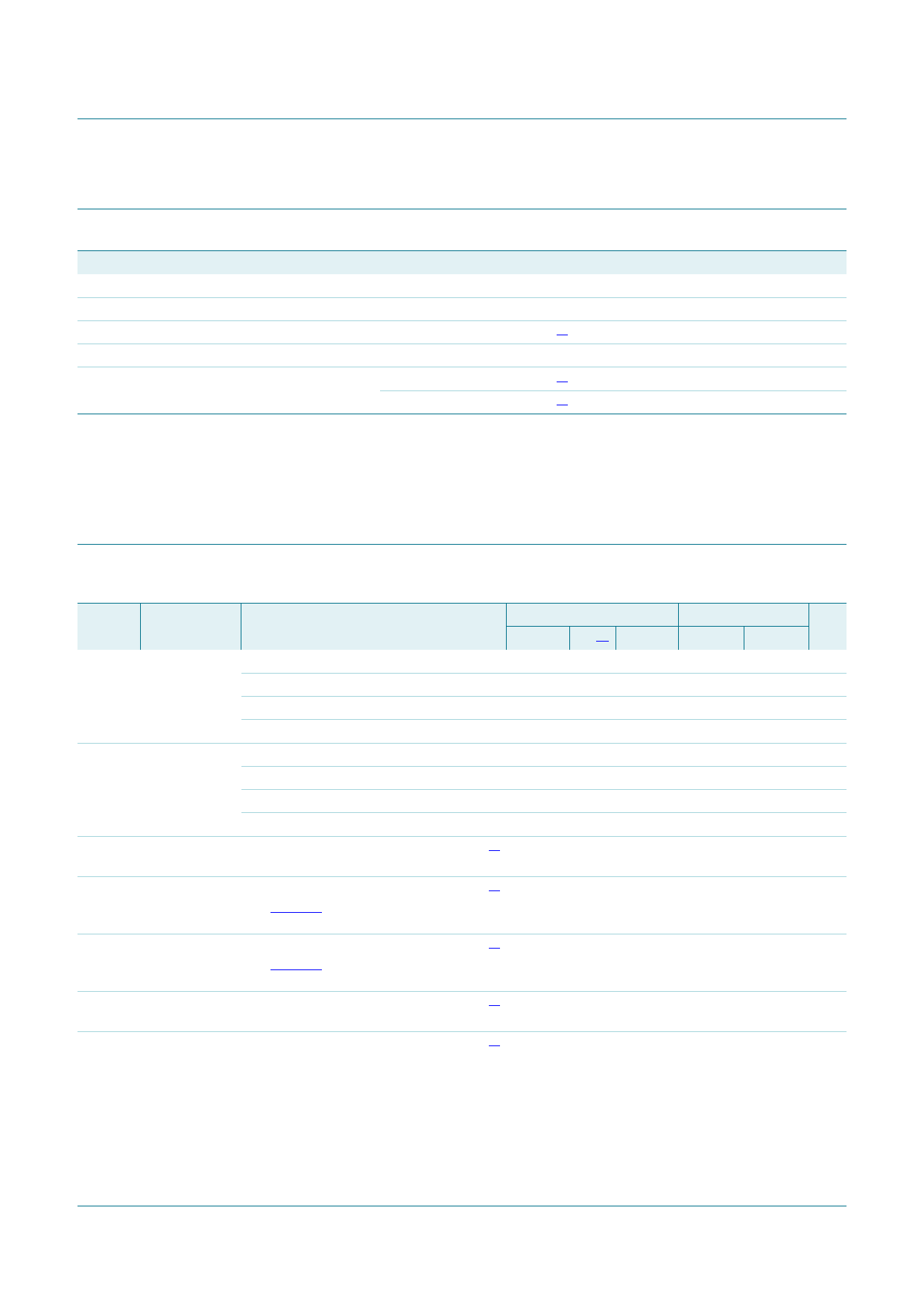

8. Recommended operating conditions

Table 5.

Symbol

VCC

VI

VSW

Tamb

t/V

Recommended operating conditions

Parameter

Conditions

supply voltage

input voltage

switch voltage

ambient temperature

input transition rise and fall rate VCC = 1.65 V to 2.7 V

VCC = 2.7 V to 5.5 V

Min

1.65

0

[1] 0

40

[2] -

[2] -

Typ

-

-

-

-

-

-

Max

5.5

5.5

VCC

+125

20

10

Unit

V

V

V

C

ns/V

ns/V

[1] To avoid sinking GND current from terminal nZ when switch current flows in terminal nY, the voltage drop across the bidirectional switch

must not exceed 0.4 V. If the switch current flows into terminal nZ, no GND current will flow from terminal nY. In this case, there is no

limit for the voltage drop across the switch.

[2] Applies to control signal levels.

9. Static characteristics

Table 6. Static characteristics

At recommended operating conditions voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions

40 C to +85 C

40 C to +125 C Unit

Min Typ[1] Max Min Max

VIH

VIL

II

IS(OFF)

HIGH-level

input voltage

LOW-level

input voltage

input leakage

current

OFF-state

leakage

current

VCC = 1.65 V to 1.95 V

VCC = 2.3 V to 2.7 V

VCC = 2.7 V to 3.6 V

VCC = 4.5 V to 5.5 V

VCC = 1.65 V to 1.95 V

VCC = 2.3 V to 2.7 V

VCC = 2.7 V to 3.6 V

VCC = 4.5 V to 5.5 V

pin nE; VCC = 5.5 V;

VI = 5.5 V or GND

VSW = VCC GND; VCC = 5.5 V;

see Figure 6

0.65VCC

1.7

-

-

- 0.65VCC - V

- 1.7 - V

2.0 -

-

2.0

-V

0.7VCC

-

-

- - 0.7VCC - V

- 0.35VCC - 0.35VCC V

- 0.7 - 0.7 V

- - 0.8 - 0.8 V

- - 0.3VCC - 0.3VCC V

[2] -

0.1 5

-

20 A

[2] -

0.1 5

-

20 A

IS(ON) ON-state

VSW = VCC GND; VCC = 5.5 V;

[2] -

0.1 5

- 20 A

leakage

see Figure 7

current

ICC

ICC

supply current

additional

supply current

VI = VCC or GND; VSW = GND or

VCC; VCC = 5.5 V

pin nE; VI = VCC 0.6 V; VCC = 5.5 V;

VSW = GND or VCC

[2]

[2]

-

-

0.1 10

5 500

- 40 A

- 5000 A

74LVC4066

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 5 — 23 November 2011

© NXP B.V. 2011. All rights reserved.

5 of 23

5 Page

NXP Semiconductors

74LVC4066

Quad bilateral switch

10.1 Waveforms and test circuit

nY or nZ

input

VI

GND

nZ or nY

output

VOH

VOL

VM

t PLH

VM

VM

t PHL

VM

001aaa541

Measurement points are given in Table 9.

Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 15. Input (nY or nZ) to output (nZ or nY) propagation delays

nE input

VI

GND

nY or nZ

output

VCC

LOW-to-OFF

OFF-to-LOW

VOL

nY or nZ

output

VOH

HIGH-to-OFF

OFF-to-HIGH

GND

VM

t PLZ

t PZL

t PHZ

VX

VY

switch

enabled

VM

t PZH

switch

disabled

VM

switch

enabled

001aaa542

Measurement points are given in Table 9.

Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 16. Enable and disable times

Table 9. Measurement points

Supply voltage

Input

VCC

1.65 V to 1.95 V

2.3 V to 2.7 V

2.7 V

VM

0.5VCC

0.5VCC

1.5 V

3.0 V to 3.6 V

1.5 V

4.5 V to 5.5 V

0.5VCC

Output

VM

0.5 VCC

0.5VCC

1.5 V

1.5 V

0.5VCC

VX

VOL + 0.15 V

VOL + 0.15 V

VOL + 0.3 V

VOL + 0.3 V

VOL + 0.3 V

VY

VOH 0.15 V

VOH 0.15 V

VOH 0.3 V

VOH 0.3 V

VOH 0.3 V

74LVC4066

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 5 — 23 November 2011

© NXP B.V. 2011. All rights reserved.

11 of 23

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet 74LVC4066.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LVC4066 | Quad bilateral switches | NXP Semiconductors |

| 74LVC4066 | Quad bilateral switches | Philips |

| 74LVC4066BQ | Quad bilateral switches | NXP Semiconductors |

| 74LVC4066D | Quad bilateral switches | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |