|

|

PDF OR4E2 Data sheet ( Hoja de datos )

| Número de pieza | OR4E2 | |

| Descripción | Field-Programmable Gate Arrays | |

| Fabricantes | Agere Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de OR4E2 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Preliminary Data Sheet

December 2000

ORCA® Series 4

Field-Programmable Gate Arrays

Programmable Features

s High-performance platform design.

— 0.13 µm seven-level metal technology.

— Internal performance of >250 MHz

(four logic levels).

— I/O performance of >416 MHz for all user I/Os.

— Over 1.5 million usable system gates.

— Meets multiple I/O interface standards.

— 1.5 V operation (30% less power than 1.8 V oper-

ation) translates to greater performance.

— Embedded block RAM (EBR) for onboard stor-

age and buffer needs.

— Built-in system components including an internal

system bus, eight PLLs, and microprocessor

interface.

s Traditional I/O selections.

— LVTTL and LVCMOS (3.3 V, 2.5 V, and 1.8 V)

I/Os.

— Per pin-selectable I/O clamping diodes provide

3.3 V PCI compliance.

— Individually programmable drive capability.

24 mA sink/12 mA source, 12 mA sink/6 mA

source, or 6 mA sink/3 mA source.

— Two slew rates supported (fast and slew-limited).

— Fast-capture input latch and input flip-flop (FF)/

latch for reduced input setup time and zero hold

time.

— Fast open-drain drive capability.

— Capability to register 3-state enable signal.

— Off-chip clock drive capability.

— Two-input function generator in output path.

s New programmable high-speed I/O.

— Single-ended: GTL, GTL+, PECL, SSTL3/2

(class I & II), HSTL (Class I, III, IV), zero-bus

turn-around (ZBT*), and double data rate (DDR).

— Double-ended: LDVS, bused-LVDS, LVPECL.

— Customer defined: Ability to substitute arbitrary

standard-cell I/O to meet fast moving standards.

s New capability to (de)multiplex I/O signals.

— New DDR on both input and output at rates up to

311 MHz (622 MHz effective rate).

— Used to implement emerging RapidIO† back-

plane interface specification.

— New 2x and 4x downlink and uplink capability per

I/O (i.e., 104 MHz internal to 416 MHz I/O).

s Enhanced twin-quad programmable function unit

(PFU).

— Eight 16-bit look-up tables (LUTs) per PFU.

— Nine user registers per PFU, one following each

LUT and organized to allow two nibbles to act

independently, plus one extra for arithmetic

carry/borrow operations.

* ZBT is a trademark of Integrated Device Technologies Inc.

† RapidIO is a trademark of Motorola, Inc.

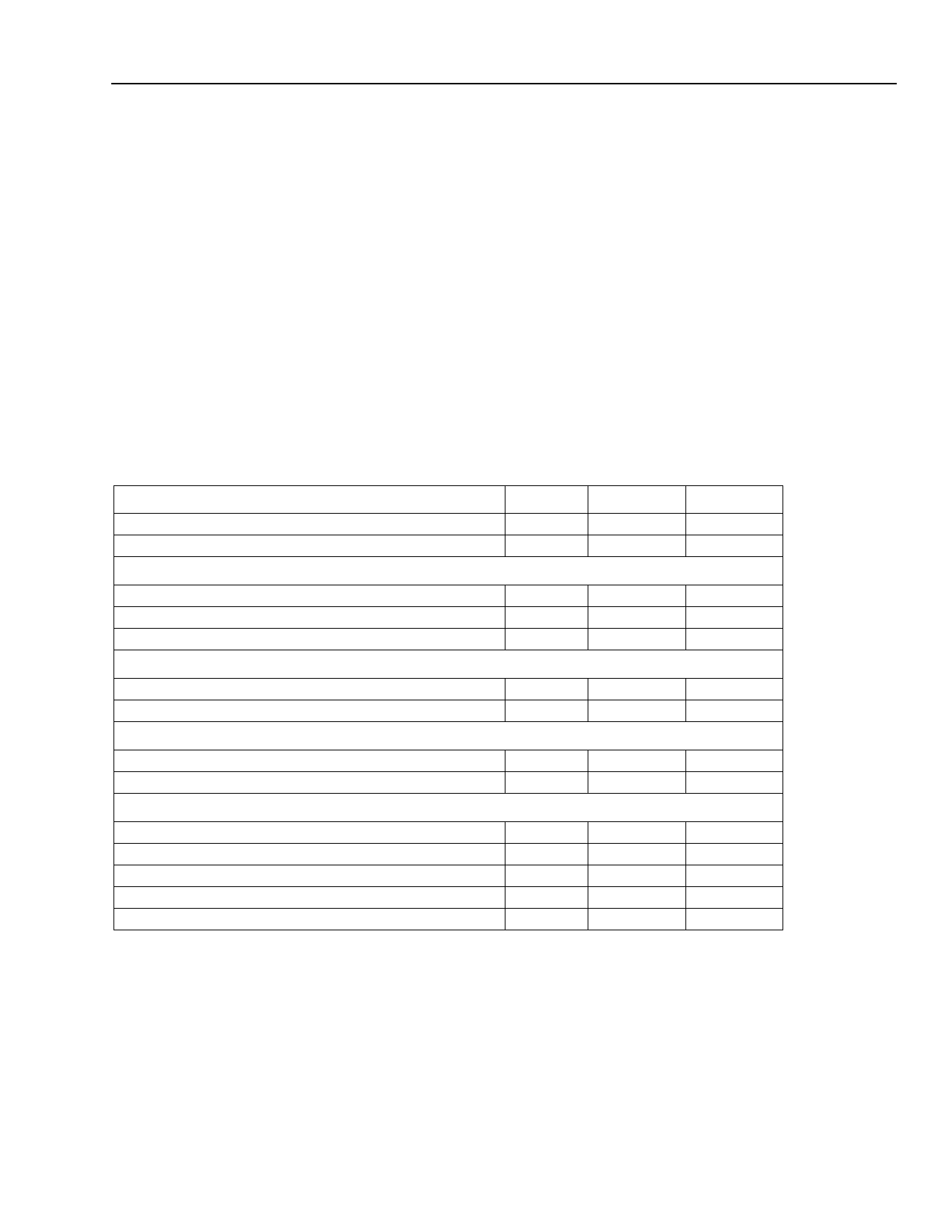

Table 1. ORCA Series 4—Available FPGA Logic

Device Columns Rows

OR4E2

OR4E4

OR4E6

OR4E10

OR4E14

26

36

46

60

70

24

36

44

56

66

PFUs

624

1296

2024

3360

4620

User I/O

400

576

720

928

1088

LUTs

4992

10368

16,192

26,880

36,960

EBR

Blocks

8

12

16

20

24

EBR Bits (k)

Usable†

Gates (k)

74 260—470

111 400—720

148 530—970

185 740—1350

222 930—1700

† The usable gate counts range from a logic-only gate count to a gate count assuming 20% of the PFUs/SLICs being used as RAMs. The

logic-only gate count includes each PFU/SLIC (counted as 108 gates/PFU), including 12 gates per LUT/FF pair (eight per PFU), and

12 gates per SLIC/FF pair (one per PFU). Each of the four PIO groups are counted as 16 gates (three FFs, fast-capture latch, output logic,

CLK, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32 x 4 RAM (or

512 gates) per PFU. Embedded block RAM (EBR) is counted as four gates per bit plus each block has an additional 25k gates. 7k gates

are used for each PLL and 50k gates for the embedded system bus and microprocessor interface logic. Both the EBR and PLLs are con-

servatively utilized in the gate count calculations.

Note: Devices are not pinout compatible with ORCA Series 2/3.

1 page

Preliminary Data Sheet

December 2000

ORCA Series 4 FPGAs

System Features (continued)

s Variable-size bused readback of configuration data capability with the built-in MPI and system bus.

s Internal, 3-state, bidirectional buses with simple control provided by the SLIC.

s Meets universal test and operations PHY interface for ATM (UTOPIA) Levels 1, 2, and 3. Also meets proposed

specifications for UTOPIA Level 4 for 10 Gbits/s interfaces.

s New clock routing structures for global and local clocking significantly increases speed and reduces skew

(<200 ps for OR4E4).

s New local clock routing structures allow creation of localized clock trees anywhere on the device.

s New DDR, QDR, and ZBT memory interfaces support the latest high-speed memory interfaces.

s New 2x/4x uplink and downlink I/O shift registers capabilities interface high-speed external I/Os to reduced inter-

nal logic speed.

s ORCA Foundry 2000 development system software. Supported by industry-standard CAE tools for design entry,

synthesis, simulation, and timing analysis.

Table 2. System Performance

Function

16-bit loadable up/down counter

16-bit accumulator

8 x 8 Parallel Multiplier

Multiplier mode, unpipelined 1

ROM mode, unpipelined 2

Multiplier mode, pipelined 3

32 x 16 RAM (synchronous)

Single port, 3-state bus 4

Dual-port 5

128 x 8 RAM (synchronous)

Single port, 3-state bus 4

Dual-port, 3-state bus 5

Address Decode

8-bit internal, LUT-based

8-bit internal, SLIC-based 6

32-bit internal, LUT-based

32-bit internal, SLIC-based 7

36-bit Parity Check (internal)

No. PFUs

2

2

2

282

282

11.5 72

8 175

15 197

4 264

4 340

8 264

8 264

0.25 1.37

0 0.73

2 4.68

0 2.08

2 4.68

Unit

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

ns

ns

ns

ns

ns

1. Implemented using 8 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

2. Implemented using two 32 x 4 RAMs and one 12-bit adder, one 8-bit input, one fixed operand, one 16-bit output.

3. Implemented using 8 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (seven of 15 PFUs

contain only pipelining registers).

4. Implemented using 32 x 4 RAM mode with read data on 3-state buffer to bidirectional read/write bus.

5. Implemented using 32 x 4 dual-port RAM mode.

6. Implemented in one partially occupied SLIC, with decoded output setup to CE in the same PLC.

7. Implemented in five partially occupied SLICs.

Lucent Technologies Inc.

5

5 Page

Preliminary Data Sheet

December 2000

ORCA Series 4 FPGAs

Programmable Logic Cells (continued)

Look-Up Table Operating Modes

The operating mode affects the functionality of the PFU input and output ports and internal PFU routing. For exam-

ple, in some operating modes, the DIN[7:0] inputs are direct data inputs to the PFU latches/FFs. In memory mode,

the same DIN[7:0] inputs are used as a 4-bit write data input bus and a 4-bit write address input bus

into LUT memory.

Table 3 lists the basic operating modes of the LUT. Figure 4—Figure 7 show block diagrams of the LUT operating

modes. The accompanying descriptions demonstrate each mode’s use for generating logic.

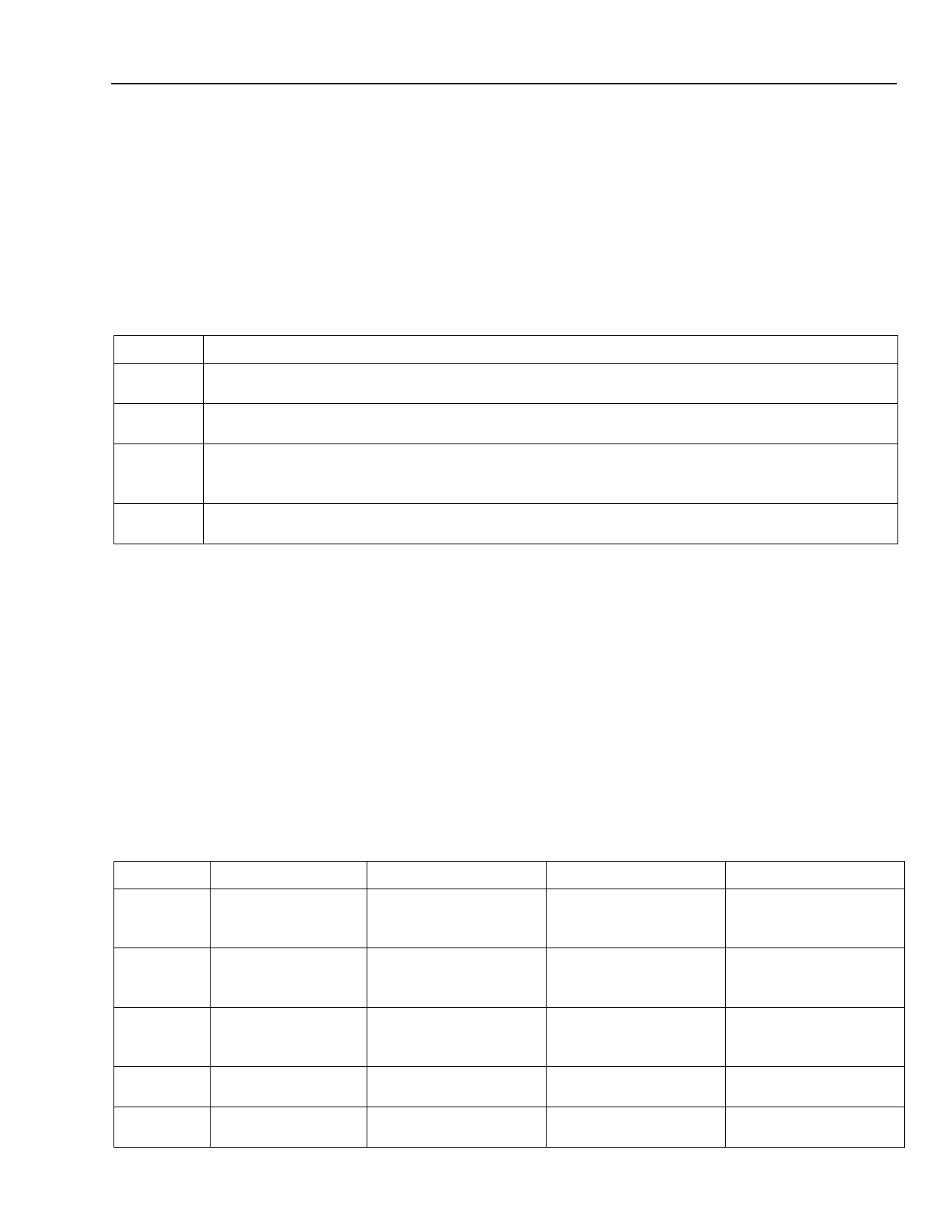

Table 3. Look-Up Table Operating Modes

Mode

Function

Logic

4-, 5-, and 6-input LUTs; softwired LUTs; latches/FFs with direct input or LUT input; CIN as direct

input to ninth FF or as pass through to COUT.

Half Logic/ Upper four LUTs and latches/FFs in logic mode; lower four LUTs and latches/FFs in ripple mode;

Half Ripple CIN and ninth FF for logic or ripple functions.

Ripple

All LUTs combined to perform ripple-through data functions. Eight LUT registers available for

direct-in use or to register ripple output. Ninth FF dedicated to ripple out, if used. The submodes of

ripple mode are adder/subtractor, counter, multiplier, and comparator.

Memory All LUTs and latches/FFs used to create a 32x4 synchronous dual-port RAM. Can be used as

single-port or as ROM.

PFU Control Inputs

Each PFU has eight routable control inputs and an active-low, asynchronous global set/reset (GSRN) signal that

affects all latches and FFs in the device. The eight control inputs are CLK[1:0], LSR[1:0], CE[1:0], and SEL[1:0],

and their functionality for each logic mode of the PFU is shown in Table 4. The clock signal to the PFU is CLK, CE

stands for clock enable, which is its primary function. LSR is the local set/reset signal that can be configured as syn-

chronous or asynchronous. The selection of set or reset is made for each latch/FF and is not a function of the signal

itself. SEL is used to dynamically select between direct PFU input and LUT output data as the input to

the latches/FFs.

All of the control signals can be disabled and/or inverted via the configuration logic. A disabled clock enable

indicates that the clock is always enabled. A disabled LSR indicates that the latch/FF never sets/resets (except from

GSRN). A disabled SEL input indicates that DIN[7:0] PFU inputs or the LUT outputs are always input to the latches/

FFs.

Table 4. Control Input Functionality

Mode

CLK[1:0]

LSR[1:0]

Logic

CLK to all latches/

FFs

LSR to all latches/FFs,

enabled per nibble and

for ninth FF

Half Logic/ CLK to all latches/

Half Ripple FFs

LSR to all latches/FF,

enabled per nibble and

for ninth FF

Ripple

CLK to all latches/

FFs

LSR to all latches/FFs,

enabled per nibble and

for ninth FF

Memory CLK to RAM

(RAM)

LSR0 port enable 2

Memory Optional for

Not used

(ROM) synchronous outputs

CE[1:0]

CE to all latches/FFs,

selectable per nibble

and for ninth FF

CE to all latches/FFs,

selectable per nibble

and for ninth FF

CE to all latches/FFs,

selectable per nibble

and for ninth FF

CE1 RAM write enable

CE0 Port enable 1

Not used

SEL[1:0]

Select between LUT

input and direct input for

eight latches/FFs

Select between LUT

input and direct input for

eight latches/FFs

Select between LUT

input and direct input for

eight latches/FFs

Not used

Not used

Lucent Technologies Inc.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet OR4E2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| OR4E10 | Field-Programmable Gate Arrays | Agere Systems |

| OR4E2 | Field-Programmable Gate Arrays | Agere Systems |

| OR4E4 | Field-Programmable Gate Arrays | Agere Systems |

| OR4E6 | Field-Programmable Gate Arrays | Agere Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |