|

|

PDF 74HC164 Data sheet ( Hoja de datos )

| Número de pieza | 74HC164 | |

| Descripción | 8-bit serial-in/parallel-out shift register | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74HC164 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

74HC164; 74HCT164

8-bit serial-in, parallel-out shift register

Rev. 03 — 4 April 2005

Product data sheet

1. General description

The 74HC164; 74HCT164 are high-speed Si-gate CMOS devices and are pin compatible

with Low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC164; 74HCT164 are 8-bit edge-triggered shift registers with serial data entry

and an output from each of the eight stages. Data is entered serially through one of two

inputs (DSA or DSB); either input can be used as an active HIGH enable for data entry

through the other input. Both inputs must be connected together or an unused input must

be tied HIGH.

Data shifts one place to the right on each LOW-to-HIGH transition of the clock (CP) input

and enters into Q0, which is the logical AND of the two data inputs (DSA and DSB) that

existed one set-up time prior to the rising clock edge.

A LOW level on the master reset (MR) input overrides all other inputs and clears the

register asynchronously, forcing all outputs LOW.

2. Features

s Gated serial data inputs

s Asynchronous master reset

s Complies with JEDEC standard no. 7A

s ESD protection:

x HBM EIA/JESD22-A114-B exceeds 2000 V

x MM EIA/JESD22-A115-A exceeds 200 V.

s Multiple package options

s Specified from −40 °C to +85 °C and −40 °C to +125 °C.

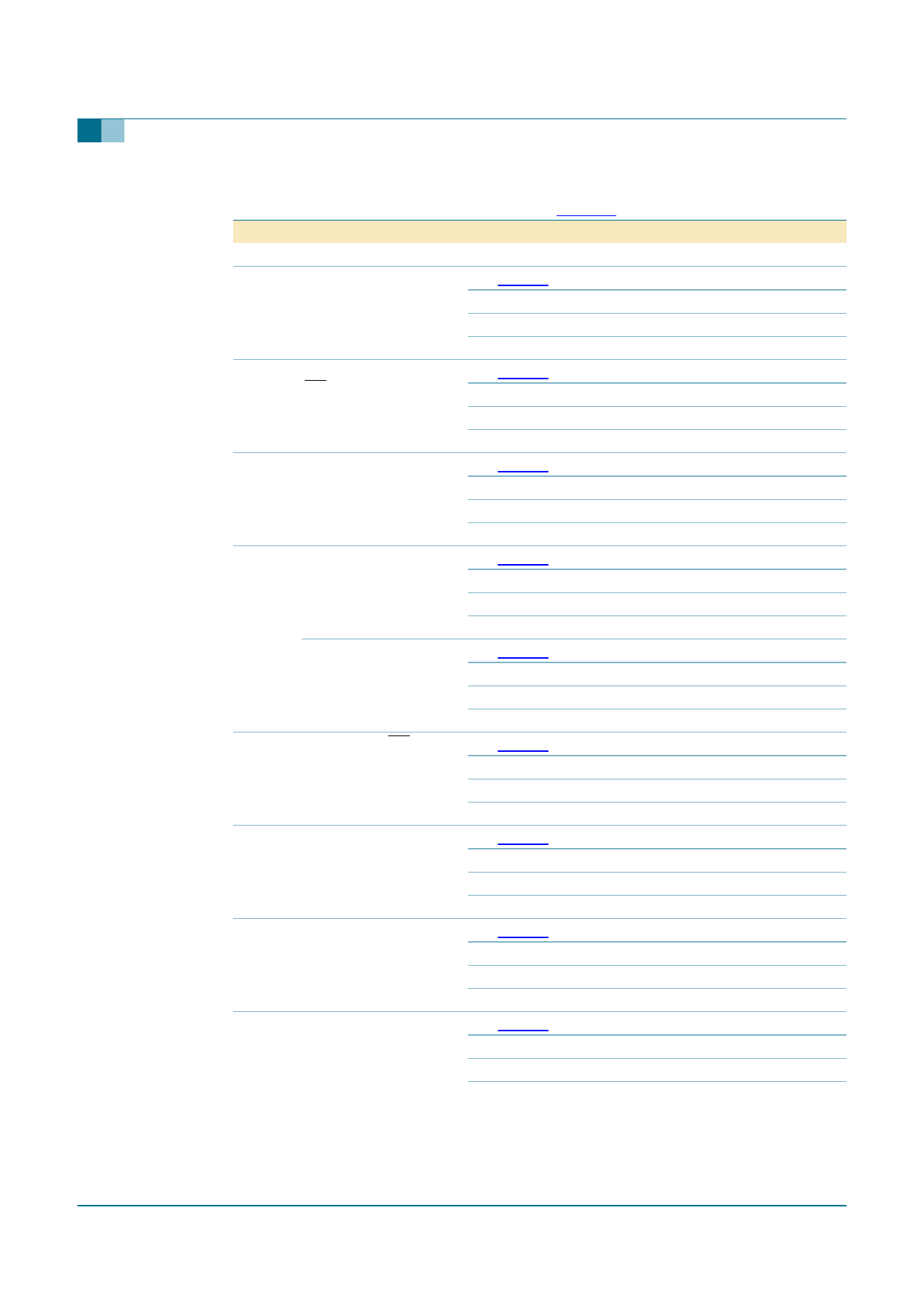

3. Quick reference data

Table 1: Quick reference data

GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns.

Symbol

Parameter

Type 74HC164

tPHL, tPLH

propagation delay

CP to Qn

MR to Qn

Conditions

Min Typ Max Unit

CL = 15 pF;

VCC = 5 V

CL = 15 pF;

VCC = 5 V

- 12 - ns

- 11 - ns

1 page

Philips Semiconductors

74HC164; 74HCT164

8-bit serial-in, parallel-out shift register

Table 3:

Symbol

GND

CP

MR

Q4

Q5

Q6

Q7

VCC

Pin description …continued

Pin Description

7 ground (0 V)

8 clock input (LOW-to-HIGH, edge-triggered)

9 master reset input (active LOW)

10 output

11 output

12 output

13 output

14 positive supply voltage

7. Functional description

7.1 Function selection

Table 4: Function table [1]

Operating

modes

Input

MR

CP

Reset (clear) L

X

Shift H ↑

H↑

H↑

H↑

DSA

X

l

l

h

h

DSB

X

l

h

l

h

Output

Q0

L

L

L

L

H

Q1 to Q7

L to L

q0 to q6

q0 to q6

q0 to q6

q0 to q6

[1] H = HIGH voltage level

h = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition

L = LOW voltage level

I = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition

q = lower case letters indicate the state of the referenced input one set-up time prior to the LOW-to-HIGH

clock transition

↑ = LOW-to-HIGH clock transition

8. Limiting values

Table 5: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to

GND (ground = 0 V).

Symbol Parameter

Conditions

Min Max Unit

VCC

IIK

IOK

IO

ICC, IGND

Tstg

supply voltage

input diode current

output diode current

output source or sink current

VCC or GND current

storage temperature

VI < −0.5 V or

VI > VCC + 0.5 V

VO < −0.5 V or

VO > VCC + 0.5 V

VO = −0.5 V to VCC + 0.5 V

−0.5 +7

- ±20

V

mA

- ±20 mA

- ±25 mA

- ±50 mA

−65 +150 °C

9397 750 14693

Product data sheet

Rev. 03 — 4 April 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

5 of 24

5 Page

Philips Semiconductors

74HC164; 74HCT164

8-bit serial-in, parallel-out shift register

Table 9: Dynamic characteristics for 74HC164 …continued

GND = 0 V; tr = tf = 6 ns; CL = 50 pF; test circuit see Figure 10; unless otherwise specified

Symbol Parameter

Conditions

Min Typ Max Unit

Tamb = −40 °C to +85 °C

tPHL, tPLH propagation delay

CP to Qn

see Figure 7

VCC = 2.0 V

- - 215 ns

VCC = 4.5 V

- - 43 ns

VCC = 6.0 V

- - 37 ns

tPHL propagation delay

MR to Qn

see Figure 8

VCC = 2.0 V

- - 175 ns

VCC = 4.5 V

VCC = 6.0 V

- - 35 ns

- - 30 ns

tTHL, tTLH output transition time

see Figure 7

VCC = 2.0 V

- - 95 ns

VCC = 4.5 V

- - 19 ns

VCC = 6.0 V

- - 16 ns

tW clock pulse width;

HIGH or LOW

see Figure 7

VCC = 2.0 V

100 - - ns

VCC = 4.5 V

20 - - ns

master reset pulse width;

LOW

VCC = 6.0 V

see Figure 8

VCC = 2.0 V

17 - - ns

75 - - ns

VCC = 4.5 V

15 - - ns

VCC = 6.0 V

13 - - ns

trem removal time MR to CP see Figure 8

VCC = 2.0 V

75 - - ns

VCC = 4.5 V

15 - - ns

VCC = 6.0 V

13 - - ns

tsu set-up time

see Figure 9

DSA and DSB to CP

VCC = 2.0 V

75 - - ns

VCC = 4.5 V

15 - - ns

VCC = 6.0 V

13 - - ns

th hold time DSA and DSB see Figure 9

-

to CP

VCC = 2.0 V

4 - - ns

VCC = 4.5 V

4 - - ns

VCC = 6.0 V

4 - - ns

fmax maximum clock pulse see Figure 7

frequency

VCC = 2.0 V

VCC = 4.5 V

5 - - MHz

24 - - MHz

VCC = 6.0 V

28 - - MHz

9397 750 14693

Product data sheet

Rev. 03 — 4 April 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

11 of 24

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet 74HC164.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74HC160 | Presettable synchronous BCD decade counter asynchronous reset | Philips |

| 74HC161 | Presettable synchronous 4-bit binary counter asynchronous reset | Philips |

| 74HC162 | Presettable synchronous BCD decade counter synchronous reset | Philips |

| 74HC163 | Presettable synchronous 4-bit binary counter synchronous reset | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |