|

|

PDF 68HC11K4 Data sheet ( Hoja de datos )

| Número de pieza | 68HC11K4 | |

| Descripción | MC68HC11K4 | |

| Fabricantes | Motorola Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 68HC11K4 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

MOTOROLAwww.DataSheet4U.com

SEMICONDUCTOR

TECHNICAL DATA

Technical Summary

8-Bit Microcontroller

Order this document

by MC68HC11KTS/D

M68HC11 K Series

The M68HC11 K-series microcontroller units (MCUs) are high-performance derivatives of the

MC68HC11F1 and have several additional features. The MC68HC11K0, MC68HC11K1,

MC68HC11K3, MC68HC11K4 and MC68HC711K4 comprise the series. These MCUs, with a nonmul-

tiplexed expanded bus, are characterized by high speed and low power consumption. Their fully static

design allows operation at frequencies from 4 MHz to dc.

This document contains information concerning standard, custom-ROM, and extended-voltage devic-

es. Standard devices include those with disabled ROM (MC68HC11K1), disabled EEPROM

(MC68HC11K3), disabled ROM and EEPROM (MC68HC11K0), or EPROM replacing ROM

(MC68HC711K4). Custom-ROM devices have a ROM array that is programmed at the factory to cus-

tomer specifications. Extended-voltage devices are guaranteed to operate over a much greater voltage

range (3.0 Vdc to 5.5 Vdc) at lower frequencies than the standard devices. Refer to the device ordering

information tables for details concerning these differences.

1 Features

• M68HC11 CPU

• Power Saving STOP and WAIT Modes

• 768 Bytes RAM (All Saved During Standby)

• 24 Kbytes ROM or EPROM

• 640 Bytes Electrically Erasable Programmable Read Only Memory (EEPROM)

• Optional Security Feature Protects Memory Contents

• On-Chip Memory Mapping Logic Allows Expansion to Over 1 Mbyte of Address Space

• PROG Mode Allows Use of Standard EPROM Programmer (27C256 Footprint)

• Nonmultiplexed Address and Data Buses

• Four Programmable Chip Selects with Clock Stretching (Expanded Modes)

• Enhanced 16-Bit Timer with Four-Stage Programmable Prescaler

— Three Input Capture (IC) Channels

— Four Output Compare (OC) Channels

— One Additional Channel, Selectable as Fourth IC or Fifth OC

• 8-Bit Pulse Accumulator

• Four 8-Bit or Two 16-Bit Pulse Width Modulation (PWM) Timer Channels

• Real-Time Interrupt Circuit

• Computer Operating Properly (COP) Watchdog

• Clock Monitor

• Enhanced Asynchronous Nonreturn to Zero (NRZ) Serial Communications Interface (SCI)

• Enhanced Synchronous Serial Peripheral Interface (SPI)

• Eight-Channel 8-Bit Analog-to-Digital (A/D) Converter

• Seven Bidirectional Input/Output (I/O) Ports (54 Pins)

• One Fixed Input-Only Port (8 Pins)

• Available in 84-Pin Plastic Leaded Chip Carrier (PLCC), 84-Pin Windowed Ceramic Leaded Chip

Carrier (CLCC), and 80-Pin Quad Flat Pack (QFP)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© MOTOROLA INC., 1997

1 page

www.DataSheet4U.com

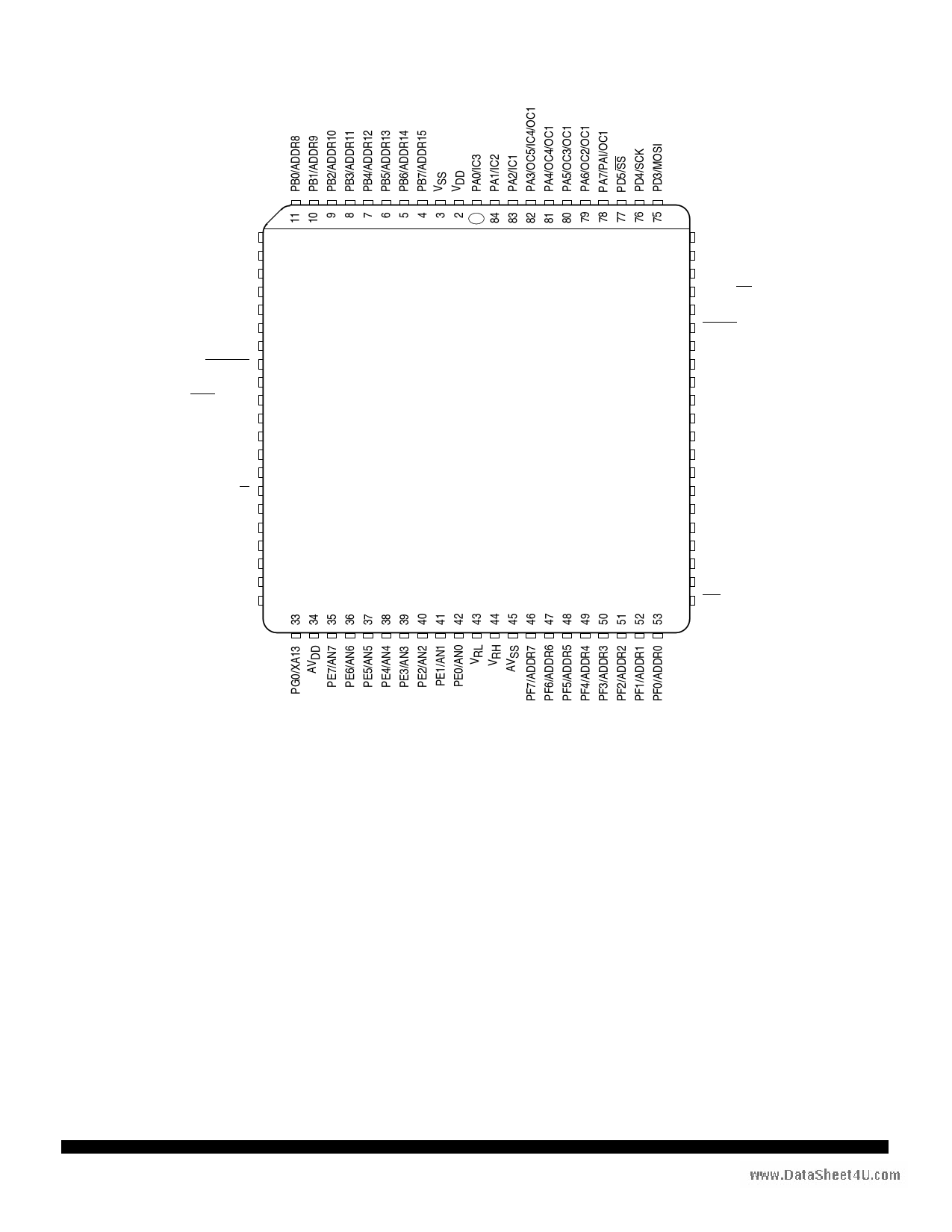

PH0/PW1

PH1/PW2

PH2/PW3

PH3/PW4

PH4/CSIO

PH5/CSGP1

PH6/CSGP2

PH7/CSPROG

TEST161

XIRQ/VPPE2

TEST151

VDD

VSS

TEST141

PG7/R/W

PG6

PG5/XA18

PG4/XA17

PG3/XA16

PG2/XA15

PG1/XA14

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

1

MC68HC11K SERIES

74 PD2/MISO

73 PD1/TxD

72 PD0/RxD

71 MODA/LIR

70 MODB/VSTBY

69 RESET

68 XTAL

67 EXTAL

66 XOUT

65 E

64 VDD

63 VSS

62 PC7/DATA7

61 PC6/DATA6

60 PC5/DATA5

59 PC4/DATA4

58 PC3/DATA3

57 PC2/DATA2

56 PC1/DATA1

55 PC0/DATA0

54 IRQ

1. Pins 20, 22, and 25 are used only during factory testing and should not be connected to external circuitry.

2. VPPE applies only to devices with EPROM.

Figure 1 Pin Assignments for 84-Pin PLCC/CLCC

M68HC11 K Series

MC68HC11KTS/D

MOTOROLA

5

5 Page

www.DataSheet4U.com

2 Operating Modes

The M68HC11 K-series MCUs have four modes of operation that directly affect the address space.

These modes are described as follows.

2.1 Single-Chip Operating Mode

In single-chip operating mode, the M68HC11 K-series MCUs are stand-alone microcontrollers with no

external address or data bus. Addressing range is 64 Kbytes and is limited to on-chip resources. Refer

to the memory map diagram.

2.2 Expanded Operating Mode

In expanded operating mode, the MCU has a 64 Kbyte address range and, using the expansion bus,

can access external resources within the 64 Kbyte space. This space includes the same on-chip mem-

ory addresses used for single-chip mode, in addition to addressing capabilities for external peripheral

and memory devices. Addressing beyond 64 Kbytes is available only in expanded mode using the on-

chip, register-based memory mapping logic. The additional address lines for memory expansion

(XA[18:13]) are implemented as alternate functions of port G. The expansion bus (external address and

data buses) is made up of ports B, C, and F, and the R/W signal. In expanded operating mode, high

order address bits are output on the port B pins, low order address bits on the port F pins, and the data

bus on port C. Refer to the memory map diagram.

2.3 Bootstrap Mode

Bootstrap mode allows special-purpose programs to be loaded into internal RAM. The MCU contains

448 bytes of bootstrap ROM which is enabled and present in the memory map only when the device is

in bootstrap mode. The bootstrap ROM contains a program which initializes the SCI and allows the user

to download up to 768 bytes of code into on-chip RAM. After a four-character delay, or after receiving

the character for address $037F, control passes to the loaded program at $0080. Refer to the memory

map diagram. Refer also to Application Note M68HC11 Bootstrap Mode (AN1060/D).

2.4 Special Test Mode

Special test mode is used primarily for factory testing. In this operating mode, ROM/EPROM is removed

from the address space and interrupt vectors are accessed externally at $BFC0–$BFFF.

2.5 Mode Selection

Operating modes are selected by a combination of logic levels applied to two input pins (MODA and

MODB) during reset. The logic level present (at the rising edge of reset) on these inputs is reflected in

bits in the HPRIO register. After reset, the operating mode may be changed according to the table con-

tained in the description of the HPRIO register.

The functions of two features that are enabled by bits in OPT2 register are dependent upon the operat-

ing mode. LIR driven is enabled with the LIRDV bit. Internal read visibility/not E is enabled with the

IRVNE bit. Refer to the OPT2 register description that follows HPRIO.

HPRIO —Highest Priority I-Bit Interrupt and Miscellaneous

$003C

Bit 7

6

5

4

3

2 1 Bit 0

RBOOT* SMOD* MDA* PSEL4 PSEL3 PSEL2 PSEL1 PSEL0

RESET:

0

0

0

0

0

1 1 0 Single Chip

0 0 1 0 0 1 1 0 Expanded

1 1 0 0 0 1 1 0 Bootstrap

0 1 1 0 0 1 1 0 Special Test

*The reset values of RBOOT, SMOD, and MDA depend on the mode selected at power up.

M68HC11 K Series

MC68HC11KTS/D

MOTOROLA

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 68HC11K4.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 68HC11K4 | MC68HC11K4 | Motorola Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |