|

|

PDF CLA80000 Data sheet ( Hoja de datos )

| Número de pieza | CLA80000 | |

| Descripción | High Density CMOS Gate Arrays | |

| Fabricantes | Zarlink Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CLA80000 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

( DataSheet : www.DataSheet4U.com )

CLA80000 Series

High Density CMOS Gate Arrays

INTRODUCTION

The CLA80k gate array series from Zarlink Semiconductor

offers advantages in speed and density over previous array

series. Improvements in design combined with advances in

simulation accuracy allow the implementation of complex

systems in excess of 260,000 gates.

FEATURES

I 0.7µ (0.8µ drawn) process

I Typical gate delay 210ps

I Accurate simulation delay (multi platform support)

I Support for industry standard workstations

I Comprehensive cell library

I 3V option for low power operation

I Split rail operation (optional 5V I/O, 3V core logic)

I Low skew clock distribution strategy

I Power and ground distribution grids

I Extensive range of package options

OVERVIEW

The gate array has a comprehensive cell library including

RAM generators as well as JTAG circuits. CLA80k is Zarlink

Semiconductor’s seventh generation CMOS gate array

product. The family consists of 22 arrays implemented on a

proven 0.7µm (0.8µm drawn) process which offers two or

three layer metal.

Zarlink Semiconductor’s Design Centres offer support on a

variety of design routes customized to individual

requirements.

Zarlink supplies design kits for the major industry standard

ASIC design tools and all kits support advanced nonlinear

delay calculations essential for accurate simulation.

Standard Density Pad Arrays are targeted for use in

ceramic packaging and for those applications which require

assembly in conformance with MIL STD 883.

DS3820

ISSUE 2.1

July 1997

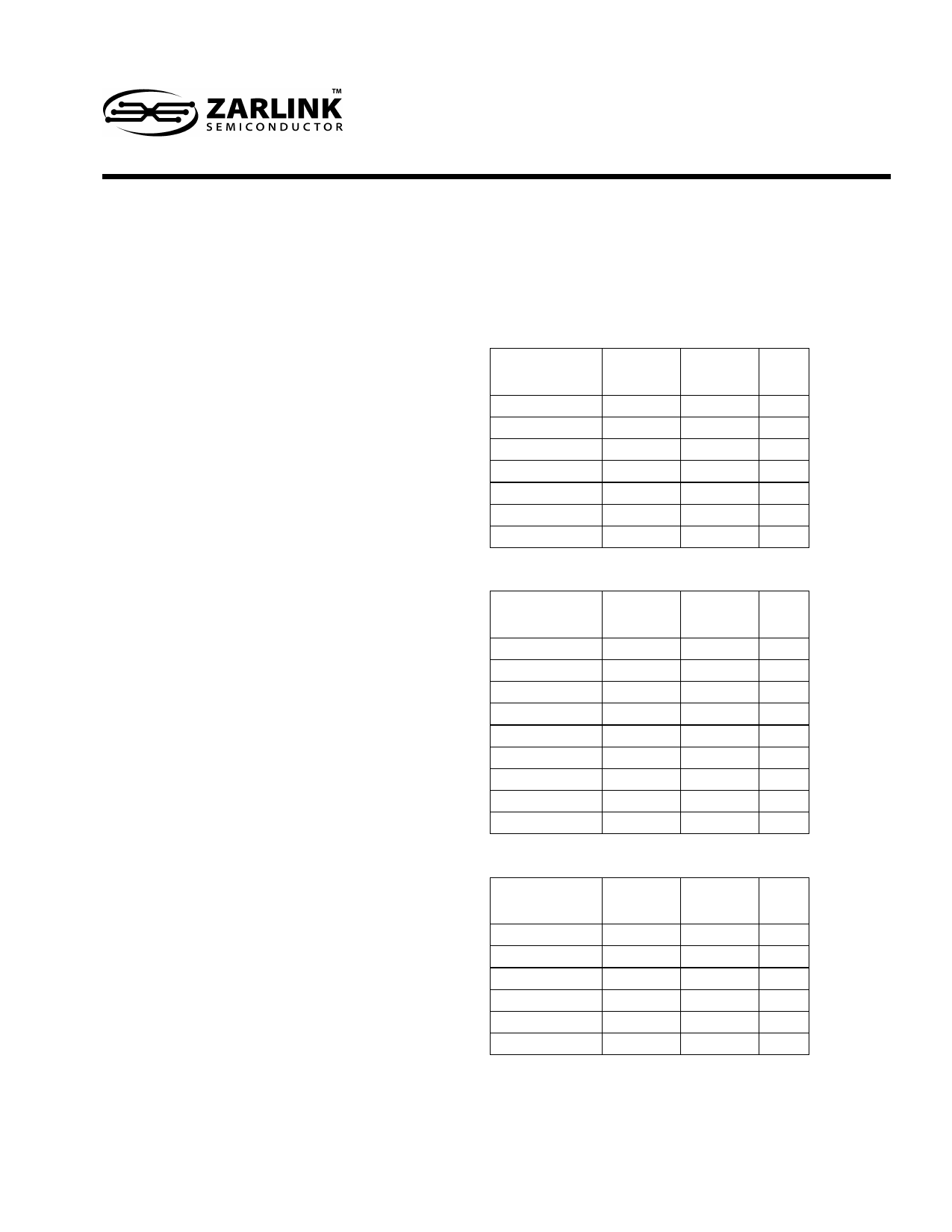

ARRAY SIZES

The CLA80k series comprises 9 base arrays and 22

variants ranging from 2816 to 513,136 array elements. The

optimum array for your requirement may be selected from

the tables below.

Double Layer Metal Arrays (High Density Pads)

Array type

CLA81XXX

CLA82XXX

CLA83XXX

CLA84XXX

CLA85XXX

CLA86XXX

CLA87XXX

Array

Usable

elements gates

Total

Pads

2816

1400 64

8736

4260 88

17920

8400 112

30784

13600 136

54720

22000 168

100048

30000 216

157872

48000 264

Triple Layer Metal Arrays (High Density Pads)

Array type

CLT81XXX

CLT82XXX

CLT83XXX

CLT84XXX

CLT85XXX

CLT86XXX

CLT87XXX

CLT88XXX

CLT89XXX

Array

Usable

elements gates

Total

pads

2816

1680 64

8736

5200 88

17920

10700 112

30784

18000 136

54720

32500 168

100048

58000 216

157872

90000 264

307568 170000 360

513136 260000 456

Standard Density Pad Arrays

Array type

MLA85XXX

MLT85XXX

MLA87XXX

MLT87XXX

MLT88XXX

MLT89XXX

Array

Usable

elements gates

Total

pads

54720

22000 144

54720

32500 144

157872

48000 232

157872

90000 232

307568 170000 312

513136 260000 384

www.DataSheet4U.com

www.DataSheet4U.com

1 page

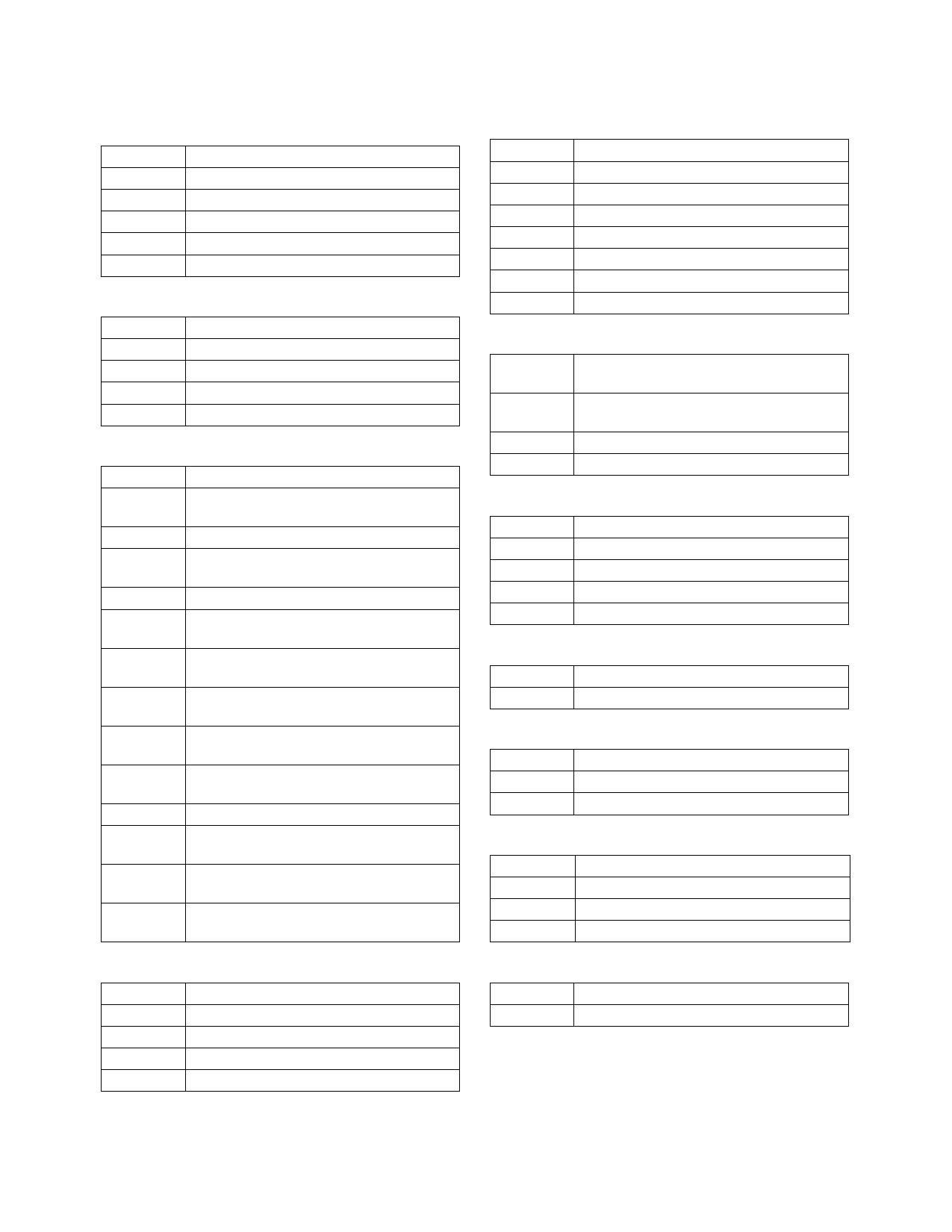

Clock Grid Drivers

CLKB84

CLKB85

CLKB86

CLKB87

CLKB88

CLKB89

Clock Grid Driver for CLT84000

Clock Grid Driver for CLT85000, MLT85000

Clock Grid Driver for CLT86000

Clock Grid Driver for CLT87000, MLT87000

Clock Grid Driver for CLT88000, MLT88000

Clock Grid Driver for CLT89000, MLT89000

Latches

SRLATCH

DL

DLR

BDL

BDLR

Set-Reset latch

Data latch

Data latch with reset

Buffered data latch

Buffered data latch with reset

Registers

DF

DFRS

MDF

MDFRS

SDF

SDFR

SDFRS

SDFS

SMDF

SMDFRS

BDF

BDFRS

BMDF

BMDFRS

Master-slave D-type flip-flop

Master-slave D-type flip-flop with set and

reset

Multiplexed master-slave D-type flip-flop

Multiplexed master-slave D-type flip-flop

with set and reset

Buffered clock master-slave D-type flip-flop

Buffered clock master-slave D-type flip-flop

with reset

Buffered clock master-slave D-type flip-flop

with set and reset

Buffered clock master-slave D-type flip-flop

with set

Buffered clock multiplexed master-slave D-

type Flip-Flop

Buffered clock multiplexed master-slave D-

type flip-flop with set and reset

Buffered master-slave D-type flip-flop

Buffered master-slave D-type flip-flop with

set and reset

Buffered multiplexed master-slave D-type

flip-flop

Buffered multiplexed master-slave D-type

flip-flop with set and reset

Input Cells

IPNR

IPR2P

IPR4P

IPR2M

IPR4M

Input with no pullup/pulldown resistor

Input with 2KOhms pullup resistor

Input with 100KOhms pullup resistor

Input with 2KOhms pulldown resistor

Input with 100KOhms pulldown resistor

Level Shifter Cells

DRV6

IBST1

IBST2

IBST3

IBTTL1

IBTTL2

IBCMOS1

IBLEVELS

Multiple output driver cell

CMOS schmitt trigger, 5 volt supply

TTL schmitt trigger, 5 volt supply

CMOS & TLL schmitt trigger, 3 volt supply

TTL input: 5 volt supply

TTL input: 3 volt supply

CMOS input: 5 volt supply

3 volt to 5 volt signal interface

Output Driver Controllers

IBCOP

IBCOP3

IBTRID

IBTRID3

Controller for push-pull, open source, and

open drain output driver

Controller for push-pull, open source, and

open drain output driver

Controller for tristate output driver

Controller for tristate output driver

Output Driver Cells

OPT1

OPT2

OPT3

OPT6

OPT12

Small output driver

Small output driver

Small output driver

Standard output driver

Large output driver

CLA8PARA LIBRARY

SPRAM

DPRAM

Single port RAM register file

Dual port RAM register file

CLA8JTAG LIBRARY

GGJTAP

GGIDREG

GGJTREG

JTAG Interface Controller

JTAG identification register

JTAG boundary scan register

Oscillator Cells

OSC32K 32kHz Crystal Oscillator

OSCHIGH 10 to 16MHz Crystal Oscillator

OSCMID 1 to 10MHz Crystal Oscillator

OSCVHIGH 15 to 25MHz Crystal Oscillator

DSP Macrocell Library

BMA8X8 Mixed Mode multiplier (8 by 8 bits)

BMA16X16 Mixed Mode multiplier (16 by 16 bits)

5

5 Page

AC ELECTRICAL CHARACTERISTICS

GATES

INVX1

NAND2X2

NOR2x2

DF

tpLH

tpHL

tpLH

tpHL

tpLH

tpHL

tpLH

tpHL

3V

2 load units

590 ps

283 ps

528 ps

291 ps

752 ps

249 ps

1068 ps

970 ps

4 load units

889 ps

391 ps

683 ps

398 ps

1065 ps

303 ps

1412 ps

1117 ps

4.5V

2 load units

421 ps

197 ps

392 ps

200 ps

476 ps

162 ps

689 ps

584 ps

4 load units

613 ps

272 ps

490 ps

269 ps

664 ps

205 ps

910 ps

685 ps

INPUTS

TTL I/P

CMOS I/P

CMOS

SCHMITT

tpLH

tpHL

tpLH

tpHL

tpLH

tpHL

3V

2 load units

767 ps

704 ps

791 ps

629 ps

1413 ps

1703 ps

4 load units

922 ps

761 ps

872 ps

659 ps

1592 ps

1778 ps

4.5V

2 load units

708 ps

114 ps

547 ps

433 ps

1114 ps

786 ps

4 load units

810 ps

1168 ps

599 ps

454 ps

1223 ps

831 ps

OUTPUT

3V

6mA BISTATE

12mA BISTATE

24mA OPEN

DRAIN

tpLH

tpHL

tpLH

tpHL

tpLH

tpHL

2 pF

3615 ps

2472 ps

4672 ps

3814 ps

5500 ps

5011 ps

4 pF

8811 ps

4549 ps

7286 ps

5106 ps

6917 ps

6463 ps

2 pF

2320 ps

1538 ps

2842 ps

2315 ps

3306 ps

2915 ps

Notes: Assumes worst case process, temperature = 70°C, input edge = 0.5 nS

4.5V

4 pF

5700 ps

2886 ps

4552 ps

3073 ps

4321 ps

3860 ps

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet CLA80000.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CLA80000 | High Density CMOS Gate Arrays | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |