|

|

PDF NCP1571 Data sheet ( Hoja de datos )

| Número de pieza | NCP1571 | |

| Descripción | Low Voltage Synchronous Buck Controller | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NCP1571 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

NCP1571

Low Voltage Synchronous

Buck Controller

The NCP1571 is a low voltage buck controller. It provides the

control for a DC−DC power solution producing an output voltage as

low as 0.980 V over a wide current range. The NCP1571−based

solution is powered from 12 V with the output derived from a 2−7 V

supply. It contains all required circuitry for a synchronous NFET buck

regulator using the V2t control method to achieve the fastest possible

transient response and best overall regulation. NCP1571 operates at a

fixed internal 200 kHz frequency and is packaged in an SOIC−8.

This device provides undervoltage lockout protection, Soft−Start,

Power Good with delay, and built−in adaptive non−overlap. During

undervoltage lockout, the NCP1571 controller allows the power

supply output to drift down, allowing the load time to shut off. This

operation distinguishes the NCP1571 from other parts in its family.

Features

• Pb−Free Package is Available

• 0.980 V ± 1.0% Reference Voltage

• V2 Control Topology

• 200 ns Transient Response

• Programmable Soft−Start

• Power Good

• Programmable Power Good Delay

• 40 ns Gate Rise and Fall Times (3.3 nF Load)

• Adaptive FET Non−Overlap Time

• Fixed 200 kHz Oscillator Frequency

• Undervoltage Lockout Holds Both Gate Outputs Low

• On/Off Control Through Use of the COMP Pin

• Overvoltage Protection through Synchronous MOSFETs

• Synchronous N−Channel Buck Design

• Dual Supply, 12 V Control, 2−7 V Power Source

http://onsemi.com

MARKING

DIAGRAM

8

1

SOIC−8

D SUFFIX

CASE 751

8

1571

ALYW

1

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

PIN CONNECTIONS

1

VCC

PWRGD

PGDELAY

COMP

8

GND

VFB

GATE(L)

GATE(H)

ORDERING INFORMATION

Device

Package

Shipping†

NCP1571D

SOIC−8

98 Units/Rail

NCP1571DR2

SOIC−8 2500 Tape & Reel

NCP1571DR2G SOIC−8 2500 Tape & Reel

(Pb−Free)

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2004

October, 2004 − Rev. 4

1

Publication Order Number

NCP1571/D

1 page

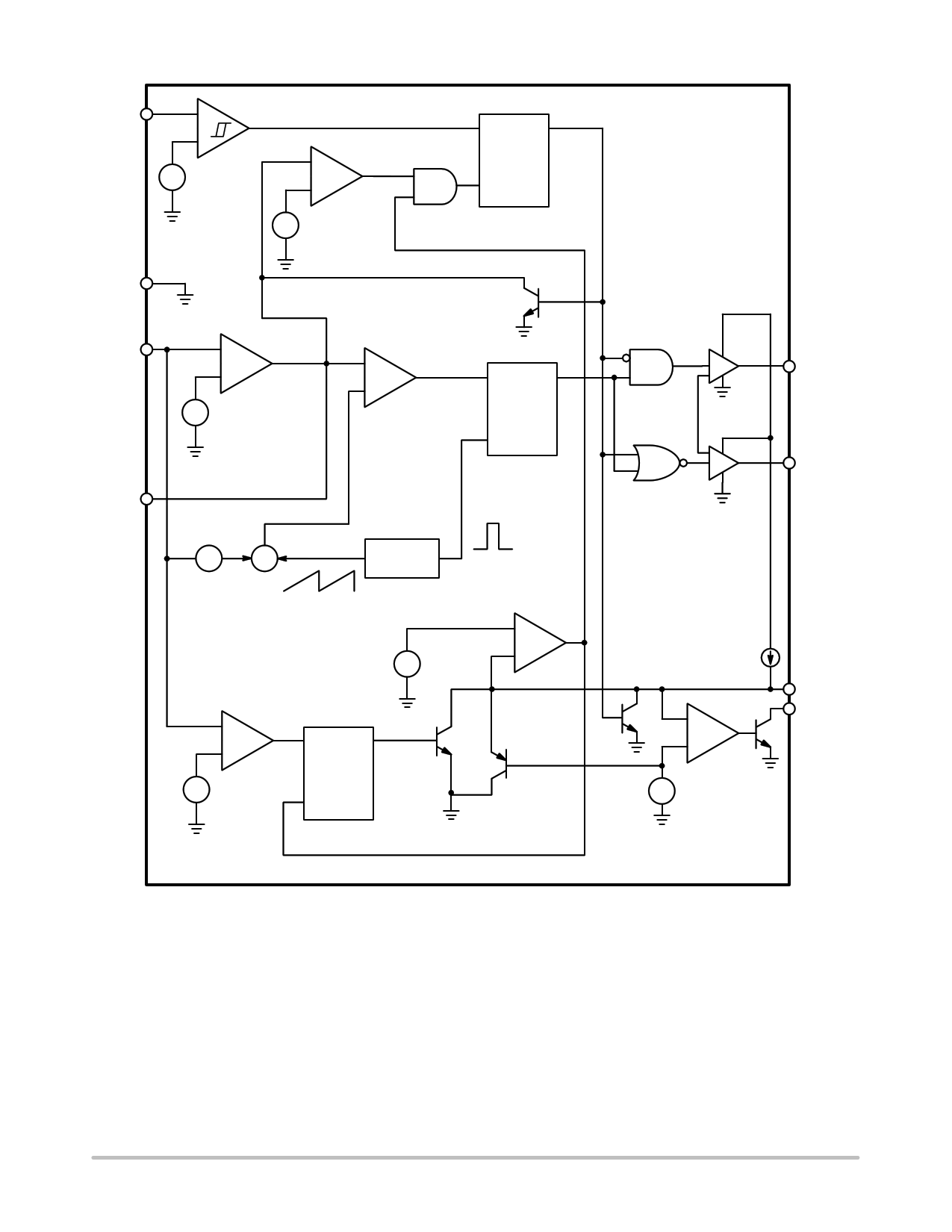

VCC − UVLO COMP

+

+

−

8.5 V/7.5 V

−

+

+

−

0.25 V

GND

NCP1571

Fault Latch

SQ

R

Set Dominant

VFB

COMP

− Error Amp

+

+

−

0.980 V

− PWM COMP

+

PWM Latch

RQ

S

Reset Dominant

0.525 V

−+

Σ

OSC

Art Ramp

80%, 200 kHz

0.25 V

+

−

− PGDELAY Latch

SQ

+

+

−

0.88 V/0.69 V

R

Set Dominant

+

−

Figure 2. Block Diagram

VCC

Non

Overlap

GATE(H)

GATE(L)

12 mA

−

+

+

−

3.3 V

PGDELAY

PWRGD

http://onsemi.com

5

5 Page

NCP1571

can not change with the required slew rate. The output

capacitors must therefore have a very low ESL and ESR.

The voltage change during the load current transient is:

ǒ ǓDVOUT + DIOUT

ESL

Dt

)

ESR

)

tTR

COUT

where:

DIOUT / Dt = load current slew rate;

DIOUT = load transient;

Dt = load transient duration time;

ESL = Maximum allowable ESL including capacitors,

circuit traces, and vias;

ESR = Maximum allowable ESR including capacitors

and circuit traces;

tTR = output voltage transient response time.

The designer has to independently assign values for the

change in output voltage due to ESR, ESL, and output

capacitor discharging or charging. Empirical data indicates

that most of the output voltage change (droop or spike

depending on the load current transition) results from the

total output capacitor ESR.

The maximum allowable ESR can then be determined

according to the formula:

ESRMAX

+

DVESR

DIOUT

where:

DVESR = change in output voltage due to ESR (assigned

by the designer)

Once the maximum allowable ESR is determined, the

number of output capacitors can be found by using the

formula:

Number

of

capacitors

+

ESRCAP

ESRMAX

where:

ESRCAP = maximum ESR per capacitor (specified in

manufacturer’s data sheet).

ESRMAX = maximum allowable ESR.

The actual output voltage deviation due to ESR can then

be verified and compared to the value assigned by the

designer:

DVESR + DIOUT ESRMAX

Similarly, the maximum allowable ESL is calculated from

the following formula:

ESLMAX

+

DVESL

DI

Dt

Selection of the Input Inductor

A common requirement is that the buck controller must

not disturb the input voltage. One method of achieving this

is by using an input inductor and a bypass capacitor. The

input inductor isolates the supply from the noise generated

in the switching portion of the buck regulator and also limits

the inrush current into the input capacitors upon power up.

The inductor’s limiting effect on the input current slew rate

becomes increasingly beneficial during load transients. The

worst case is when the load changes from no load to full load

(load step), a condition under which the highest voltage

change across the input capacitors is also seen by the input

inductor. The inductor successfully blocks the ripple current

while placing the transient current requirements on the input

bypass capacitor bank, which has to initially support the

sudden load change.

The minimum inductance value for the input inductor is

therefore:

LIN

+

DV

(dIńdt)MAX

where:

LIN = input inductor value;

DV = voltage seen by the input inductor during a full load

swing;

(dI/dt)MAX = maximum allowable input current slew rate.

The designer must select the LC filter pole frequency so

that at least 40 dB attenuation is obtained at the regulator

switching frequency. The LC filter is a double−pole network

with a slope of −2.0, a roll−off rate of −40 dB/dec, and a

corner frequency:

fC +

2p

1

ǸLC

where:

L = input inductor;

C = input capacitor(s).

Selection of the Output Inductor

There are many factors to consider when choosing the

output inductor. Maximum load current, core and winding

losses, ripple current, short circuit current, saturation

characteristics, component height and cost are all variables

that the designer should consider. However, the most

important consideration may be the effect inductor value has

on transient response.

The amount of overshoot or undershoot exhibited during

a current transient is defined as the product of the current

step and the output filter capacitor ESR. Choosing the

inductor value appropriately can minimize the amount of

energy that must be transferred from the inductor to the

capacitor or vice−versa. In the subsequent paragraphs, we

will determine the minimum value of inductance required

for our system and consider the trade−off of ripple current

vs. transient response.

In order to choose the minimum value of inductance, input

voltage, output voltage and output current must be known.

Most computer applications use reasonably well regulated

bulk power supplies so that, while the equations below

specify VIN(MAX) or VIN(MIN), it is possible to use the

nominal value of VIN in these calculations with little error.

http://onsemi.com

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet NCP1571.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NCP1570 | Low Voltage Synchronous Buck Controller | ON Semiconductor |

| NCP1571 | Low Voltage Synchronous Buck Controller | ON Semiconductor |

| NCP1573 | Low Voltage Synchronous Buck Controller | ON Semiconductor |

| NCP1575 | Low Voltage Synchronous Buck Controller | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |