|

|

PDF CDB53L21 Data sheet ( Hoja de datos )

| Número de pieza | CDB53L21 | |

| Descripción | Evaluation Board | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CDB53L21 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

CDB53L21

Evaluation Board for CS53L21

Features

Selectable Analog Inputs

– Stereo Line-Level RCA Jacks

– Stereo Microphone 1/8” Jacks

Stereo Microphone Input Jacks

8- to 96-kHz S/PDIF Output

– CS8406 Digital Audio Transmitter

I/O Stake Headers

– External Control Port Accessibility

– External DSP Serial Audio I/O Accessibility

Independent, Regulated Supplies

1.8 V to 3.3 V Logic Interface

Hardware Control

– 4 Pre-Defined Switch Settings

FlexGUI S/W Control - Windows® Compatible

– Pre-Defined & User-Configurable Scripts

Layout and Grounding Recommendations

Description

The CDB53L21 evaluation board is an excellent means

for evaluating the CS53L21 ADC. Evaluation requires

an analog audio source, an analog/digital analyzer and

power supplies. Optionally, a Windows PC-compatible

computer may be used to evaluate the CS53L21 in Soft-

ware Mode.

System timing can be provided by the CS53L21 with

supplied master clock, or by using an I/O stake header

with a DSP connected.

RCA phono jacks are provided for the CS53L21 analog

inputs. 1/8” jacks are also available for microphone in-

puts. A digital data output is available from the CS8406

via RCA phono or optical connectors.

The Windows software provides a GUI to make config-

uration of the CDB53L21 easy. The software

communicates through the PC’s serial port or USB port

to configure the control port registers so that all features

of the CS53L21 can be evaluated. The evaluation board

may also be configured to accept external timing and

data signals for operation in a user application during

system development.

ORDERING INFORMATION

CDB53L21

Evaluation Board

Software Mode

Control Port

Reset

S/PDIF Output

(CS8406)

Hardware Mode

Switches

FPGA

I²C/SPI Header

MCLK

Reset

CS53L21

Analog Input

(Line or MIC)

MCLK

Oscillator

(socket)

Reset

Reset

Clocks/Data Header

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2006

(All Rights Reserved)

MARCH '06

DS700DB1

1 page

CDB53L21

1.5 CS8406 Digital Audio Transmitter

A complete description of the CS8406 transmitter (Figure 29 on page 25) and a discussion of the digital au-

dio interface are included in the CS8406 data sheet.

The CS8406 converts the PCM data generated by the CS53L21 to the standard S/PDIF data stream and

routes this signal to the optical and RCA connectors. The CS8406 operates in slave mode only, accepting

either a 128xFs or 256xFs master clock, and can operate in either the Left-Justified or I²S interface format.

Selections are made in the control port of the FPGA, accessible through the “General Configurations” tab

of the Cirrus FlexGUI software or through the on-board switches, “FPGA H/W Control.” Section 2. “Software

Mode Control” on page 7 and Section 3. “Hardware Mode Control” on page 13 provide configuration details.

1.6 Oscillator

The on-board oscillator provides one of the system master clocks. Selections are made in the control port

of the FPGA, accessible through the “General Configurations” tab of the Cirrus FlexGUI software or through

the on-board switches, “FPGA H/W Control.” Section 2. “Software Mode Control” on page 7 and Section 3.

“Hardware Mode Control” on page 13 provide configuration details.

The oscillator is mounted in pin sockets, allowing easy removal or replacement. Additional sockets are also

installed, allowing the optional use of a full- or half-can-sized oscillator.

1.7 I/O Stake Headers

The evaluation board has been designed to allow interfacing with external systems via a serial port header

(reference designation J5) and a control port header, “CS53L21 S/W Control.” The serial port header pro-

vides access to the serial audio signals required to interface with a DSP (Figure 31 on page 27). Selections

are made in the control port of the FPGA, accessible through the “General Configurations” tab of the Cirrus

FlexGUI software or through the on-board switches, “FPGA H/W Control.” Section 2. “Software Mode Con-

trol” on page 7 and Section 3. “Hardware Mode Control” on page 13 provide configuration details.

The control port header provides bidirectional access to the SPI™/I²C® control port signals by simply re-

moving all the shunt jumpers from the “PC” position. The user may then choose to connect a ribbon cable

to the “CONTROL” position, allowing operation of the CS53L21 in a user-application for system develop-

ment. A single “GND” row for the ribbon cable’s ground connection is provided to maintain signal integrity.

Two unpopulated pull-up resistors are also available should the user choose to use the CDB for the I²C pow-

er rail.

1.8 Analog Input

RCA connectors supply the line-level analog inputs through an AC-coupled passive filter. The signal from

these inputs may be driven to individual inputs or to all inputs of the CS53L21. A microphone may be con-

nected to one or both of the 1/8” jacks, MIC1 and MIC2.

To accommodate the microphone bias output available on certain input pins of the CS53L21, additional

stake headers are provided to MUX both the input audio signal and the output bias signal to or from the

CS53L21. Figure 28 on page 24 in the schematic set illustrates how signals are routed. Table 4 on page 21

provides more details for how to connect the jumpers. The CS53L21 data sheet details the required single-

ended signal amplitude that will drive the inputs to full scale.

DS700DB1

5

5 Page

CDB53L21

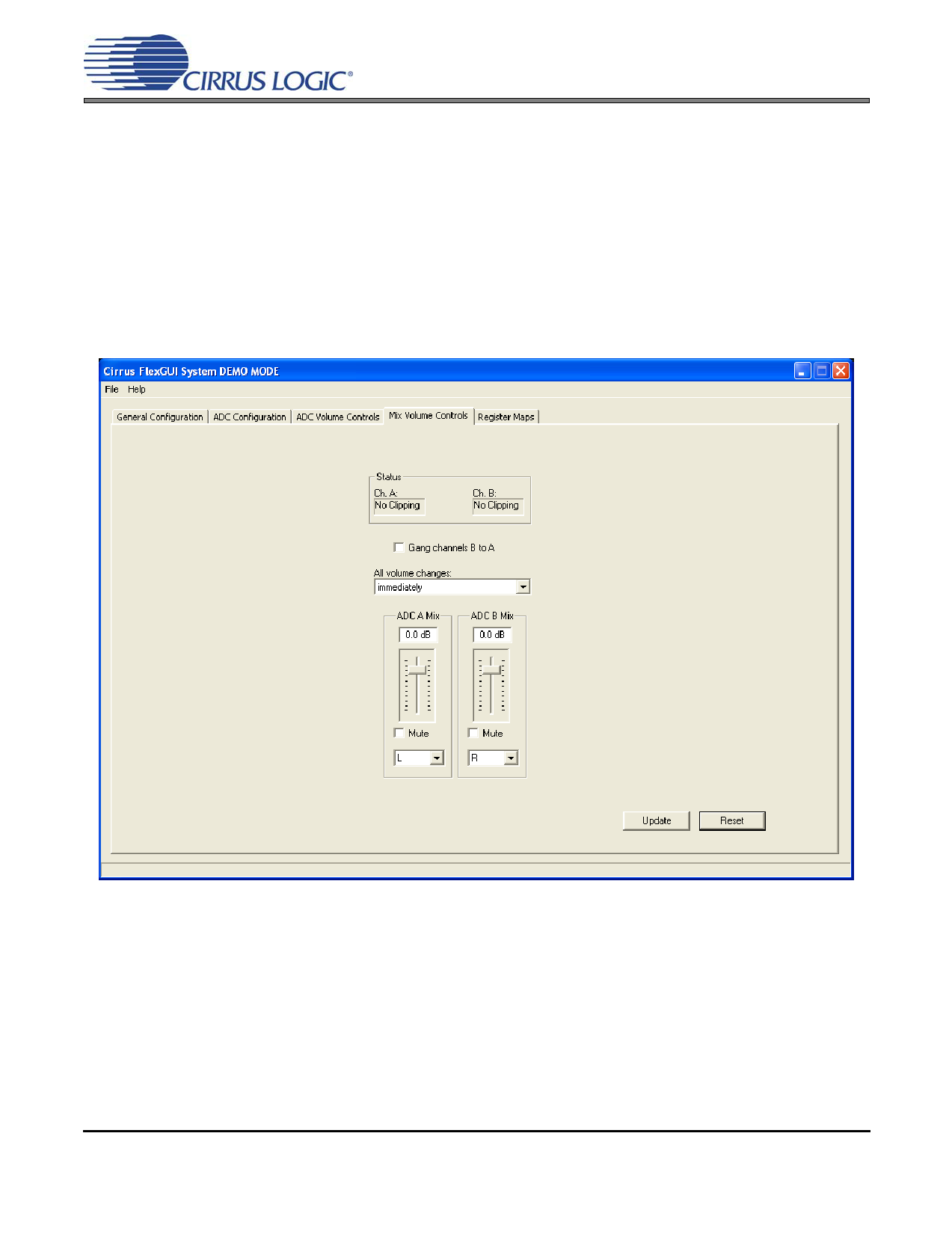

2.4 Mix Volume Controls Tab

The “Mix Volume Controls” tab provides high-level control of the ADC channel mix functions. Status text de-

tailing the ADC’s specific configuration is shown in read-only edit boxes or appears directly below the asso-

ciated control. This text will change, depending on the setting of the associated control. A description of

each control group is outlined below (a description of each register is included in the CS53L21 data sheet):

Digital Volume Control - ADC channel mix volume controls and adjustments.

Update - Reads all registers in the CS53L21 and reflects the current values in the GUI.

Reset - Resets the CS53L21.

Figure 4. Mix Volume Controls Tab

DS700DB1

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CDB53L21.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CDB53L21 | Evaluation Board | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |