|

|

PDF W3EG6464S-AD4 Data sheet ( Hoja de datos )

| Número de pieza | W3EG6464S-AD4 | |

| Descripción | 512MB - 64Mx64 DDR SDRAM UNBUFFERED | |

| Fabricantes | White Electronic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W3EG6464S-AD4 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

White Electronic Designs

W3EG6464S-AD4

-BD4

PRELIMINARY*

512MB - 64Mx64 DDR SDRAM UNBUFFERED w/PLL

FEATURES

Double-data-rate architecture

Speeds of 100MHz, 133MHz and 166MHz

Bi-directional data strobes (DQS)

Differential clock inputs (CK & CK#)

Programmable Read Latency 2,2.5 (clock)

Programmable Burst Length (2,4,8)

Programmable Burst type (sequential & interleave)

Edge aligned data output, center aligned data input

Auto and self refresh

Serial presence detect

Power supply: VCC: 2.5V ± 0.2V

JEDEC standard 200 pin SO-DIMM package

•

www.DataSheet4U.com

Package height options:

AD4: 35.5 mm (1.38"),

BD4: 31.75 (1.25")

DESCRIPTION

The W3EG6464S is a 64Mx64 Double Data Rate

SDRAM memory module based on 512Mb DDR SDRAM

component. The module consists of eight 64Mx8 DDR

SDRAMs in 66 pin TSOP packages mounted on a 200

pin FR4 substrate.

Synchronous design allows precise cycle control with the

use of system clock. Data I/O transactions are possible on

both edges and Burst Lengths allow the same device to be

useful for a variety of high bandwidth, high performance

memory system applications.

* This product is under development, is not qualified or characterized and is subject to

change without notice.

Clock Speed

CL-tRCD-tRP

OPERATING FREQUENCIES

DDR333@CL=2.5

166MHz

2.5-3-3

DDR266@CL=2

133MHz

2-2-2

DDR266@CL=2.5

133MHz

2.5-3-3

DDR200@CL=2

100MHz

2-2-2

March 2004

Rev. 1

1 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

1 page

White Electronic Designs

W3EG6464S-AD4

-BD4

PRELIMINARY

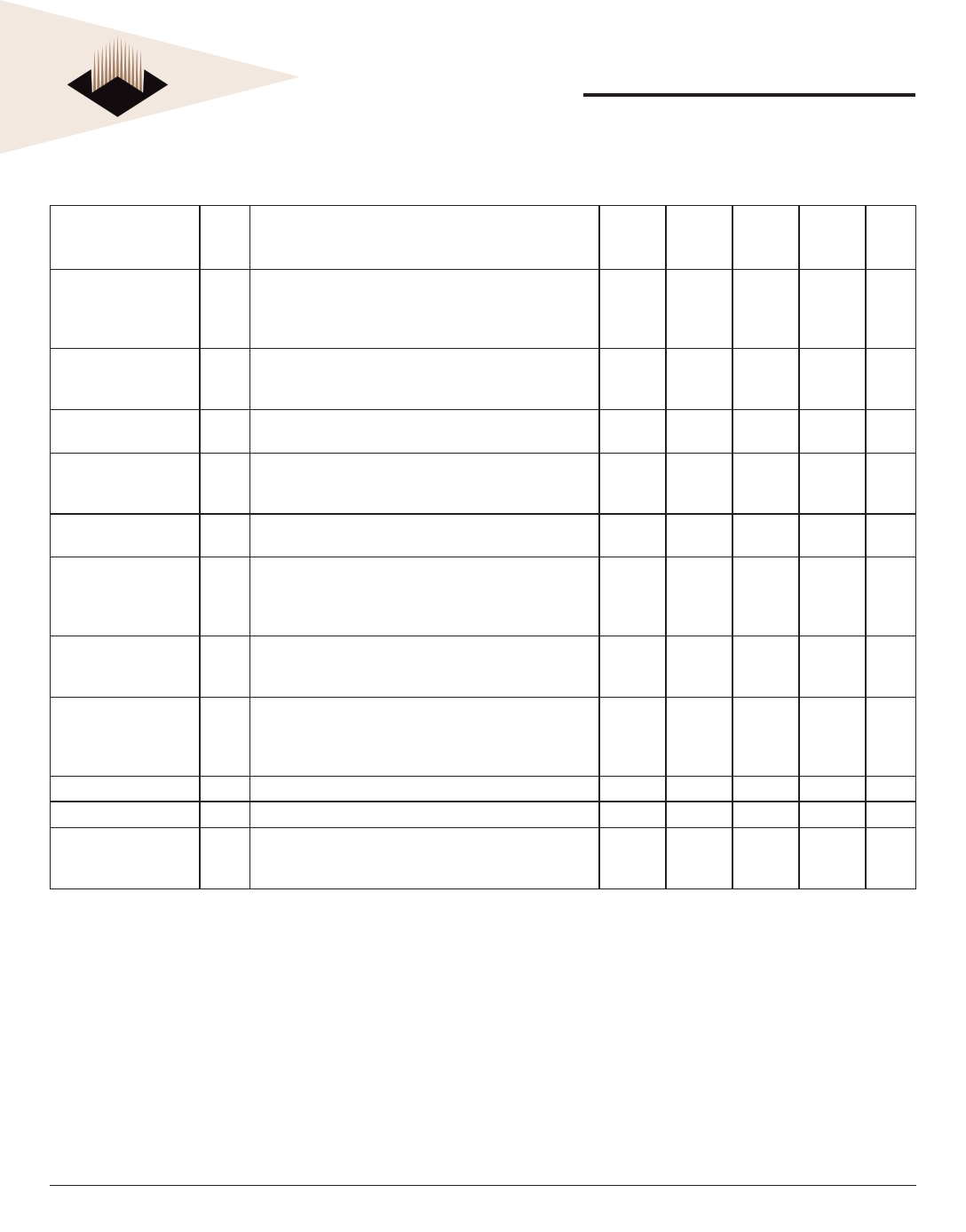

IDD SPECIFICATIONS AND TEST CONDITIONS

Recommended operating conditions, 0°C ≤ TA ≤ 70°C, VCCQ = 2.5V ± 0.2V, VCC = 2.5V ± 0.2V

Parameter

Symbol Conditions

DDR333 DDR266 DDR266

@CL=2.5 @CL=2 @CL=2.5

Max Max Max

Operating Current

One device bank; Active - Precharge; tRC=tRC(MIN);

IDD0

tCK=tCK(MIN); DQ,DM and DQS inputs changing once per

clock cycle; Address and control inputs changing once every

TBD

1595

1595

two cycles.

Operating Current

One device bank; Active-Read-Precharge; Burst = 2;

IDD1 tRC=tRC(MIN);tCK=tCK(MIN); Iout = 0mA; Address and control

inputs changing once per clock cycle.

TBD 1795 1795

Precharge Power-Down

Standby Current

IDD2P

All device banks idle; Power- down mode; tCK=tCK(MIN);

CKE=(low)

TBD 48

48

CS# = High; All device banks idle; tCK=tCK(MIN); CKE = high;

Idle Standby Current

IDD2F Address and other control inputs changing once per clock

TBD 675 675

cycle. Vin = Vref for DQ, DQS and DM.

Active Power-Down

Standby Current

IDD3P

One device bank active; Power-down mode; tCK(MIN);

CKE=(low)

TBD 400 400

CS# = High; CKE = High; One device bank; Active-Precharge;

Active Standby Current

IDD3N

tRC=tRAS(MAX); tCK=tCK(MIN); DQ, DM and DQS inputs

changing twice per clock cycle; Address and other control

TBD 1035 1035

inputs changing once per clock cycle.

Operating Current

Operating Current

Burst = 2; Reads; Continous burst; One device bank

IDD4R active;Address and control inputs changing once per clock

cycle; tCK=tCK(MIN); Iout = 0mA.

Burst = 2; Writes; Continous burst; One device bank active;

IDD4W

Address and control inputs changing once per clock cycle;

tCK=tCK(MIN); DQ,DM and DQS inputs changing twice per

clock cycle.

TBD 2035 2035

TBD 2275 2275

Auto Refresh Current

IDD5 tRC=tRC(MIN)

TBD 2755 2755

Self Refresh Current

IDD6 CKE ≤ 0.2V

TBD 315 315

Operating Current

Four bank interleaving Reads (BL=4) with auto precharge

IDD7A with tRC=tRC (MIN); tCK=tCK(MIN); Address and control inputs TBD 4115 4115

change only during Active Read or Write commands.

* For DDR333 consult factory

DDR200

@CL=2

Max

1595

1795

48

675

400

1035

2035

2275

2755

315

4115

Units

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

March 2004

Rev. 1

5 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet W3EG6464S-AD4.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W3EG6464S-AD4 | 512MB - 64Mx64 DDR SDRAM UNBUFFERED | White Electronic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |