|

|

PDF 89HPES24NT3 Data sheet ( Hoja de datos )

| Número de pieza | 89HPES24NT3 | |

| Descripción | 24-Lane 3-Port Non-Transparent PCI Express Switch | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 89HPES24NT3 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

24-Lane 3-Port Non-Transparent

PCI Express® Switch

®

89HPES24NT3

Data Sheet

Preliminary Information*

Device Overview

The 89HPES24NT3 is a member of the IDT PRECISE™ family of

PCI Express® switching solutions offering the next-generation I/O inter-

connect standard. The PES24NT3 is a 24-lane, 3-port peripheral chip

that performs PCI Express Base switching with a feature set optimized

for high performance applications such as servers, storage, and commu-

nications/networking. It provides high-performance switching functions

between a PCIe® upstream port, a transparent downstream port, and a

non-transparent downstream port.

With non-transparent bridging (NTB) functionality, the PES24NT3

can be used standalone or as a chipset with IDT PCIe System Intercon-

nect Switches in multi-host and intelligent I/O applications such as

communications, storage, and blade servers where inter-domain

communication is required.

Features

◆ High Performance PCI Express Switch

– Twenty-four PCI Express lanes (2.5Gbps), three switch ports

– Delivers 96 Gbps (12 GBps) of aggregate switching capacity

– Low latency cut-through switch architecture

– Support for Max Payload size up to 2048 bytes

– Supports one virtual channel and eight traffic classes

– PCI Express Base specification Revision 1.0a compliant

◆ Flexible Architecture with Numerous Configuration Options

– Port arbitration schemes utilizing round robin

– Supports automatic per port link width negotiation (x8, x4, x2,

or x1)

– Static lane reversal on all ports

– Automatic polarity inversion on all lanes

– Supports locked transactions, allowing use with legacy soft-

ware

– Ability to load device configuration from serial EEPROM

– Ability to control device via SMBus

◆ Non-Transparent Port

– Crosslink support on NTB port

– Four mapping windows supported

• Each may be configured as a 32-bit memory or I/O window

• May be paired to form a 64-bit memory window

– Interprocessor communication

• Thirty-two inbound and outbound doorbells

• Four inbound and outbound message registers

• Two shared scratchpad registers

– Allows up to sixteen masters to communicate through the non-

transparent port

– No limit on the number of supported outstanding transactions

through the non-transparent bridge

– Completely symmetric non-transparent bridge operation

allows similar/same configuration software to be run

– Supports direct connection to a transparent or non-transparent

port of another switch

Block Diagram

Frame Buffer

3-Port Switch Core

Route Table

Port

Arbitration

Scheduler

Transaction Layer

Data Link Layer

Multiplexer / Demultiplexer

Phy Phy

Phy

Logical Logical

Logical

Layer Layer ... Layer

SerDes SerDes

SerDes

Transaction Layer

Data Link Layer

Multiplexer / Demultiplexer

Phy Phy

Phy

Logical Logical

Logical

Layer Layer ... Layer

SerDes SerDes

SerDes

Transaction Layer

Data Link Layer

Non-

Transparent

Bridge

Multiplexer / Demultiplexer

Phy Phy

Phy

Logical Logical

Logical

Layer Layer ... Layer

SerDes SerDes

SerDes

24 PCI Express Lanes

x8 Upstream Port and Two x8 Downstream Ports

Figure 1 Internal Block Diagram

© 2007 Integrated Device Technology, Inc.

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

1 of 31

*Notice: The information in this document is subject to change without notice

April 11, 2007

DSC 6925

1 page

IDT 89HPES24NT3 Data Sheet

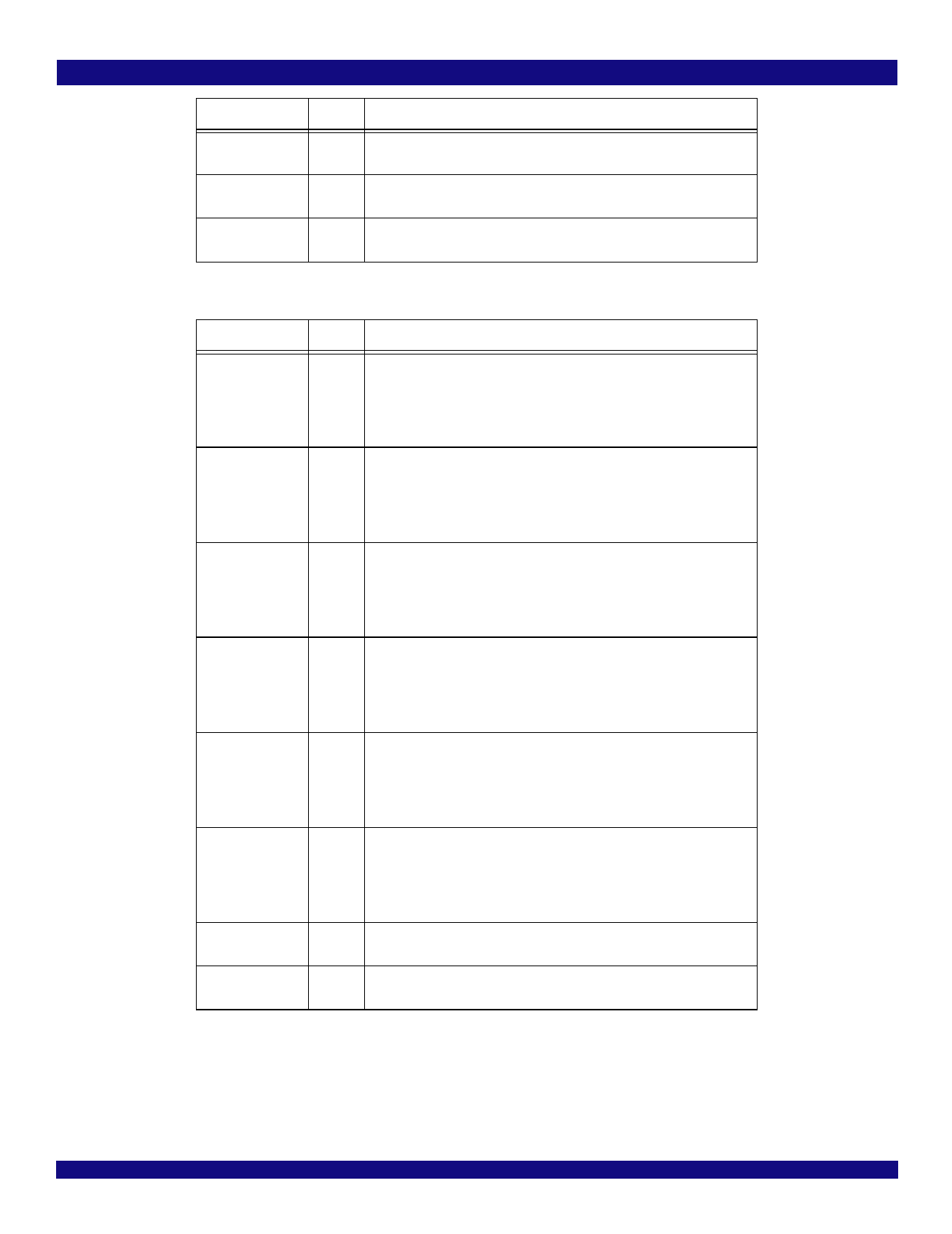

Signal

Type

Name/Description

SSMBADDR[5,3:1] I Slave SMBus Address. These pins determine the SMBus address to

which the slave SMBus interface responds.

SSMBCLK

I/O Slave SMBus Clock. This bidirectional signal is used to synchronize trans-

fers on the slave SMBus.

SSMBDAT

I/O Slave SMBus Data. This bidirectional signal is used for data on the slave

SMBus.

Table 2 SMBus Interface Pins (Part 2 of 2)

Signal

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GPIO[4]

GPIO[5]

GPIO[6]

GPIO[7]

Type

Name/Description

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: PEBRSTN

Alternate function pin type: Output

Alternate function: Reset output for downstream port B

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: PECRSTN

Alternate function pin type: Output

Alternate function: Reset output for downstream port C

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: PALINKUPN

Alternate function pin type: Output

Alternate function: Port A link up status output

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: PBLINKUPN

Alternate function pin type: Output

Alternate function: Port B link up status output

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: PCLINKUPN

Alternate function pin type: Output

Alternate function: Port C link up status output

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Alternate function pin name: FAILOVERP

Alternate function pin type: Input

Alternate function: NTB upstream port failover

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

I/O General Purpose I/O.

This pin can be configured as a general purpose I/O pin.

Table 3 General Purpose I/O Pins

5 of 31

April 11, 2007

5 Page

IDT 89HPES24NT3 Data Sheet

System Clock Parameters

Values based on systems running at recommended supply voltages and operating temperatures, as shown in Tables 12 and 13.

Parameter

Description

Min

RefclkFREQ

RefclkDC2

TR, TF

VSW

Tjitter

Input reference clock frequency range

Duty cycle of input clock

Rise/Fall time of input clocks

Differential input voltage swing4

Input clock jitter (cycle-to-cycle)

100

40

0.6

Table 8 Input Clock Requirements

1. The input clock frequency will be either 100 or 125 MHz depending on signal REFCLKM.

2. ClkIn must be AC coupled. Use 0.01 — 0.1 µF ceramic capacitors.

3. RCUI (Reference Clock Unit Interval) refers to the reference clock period.

4. AC coupling required.

Typical

50

Max

1251

60

0.2*RCUI

1.6

125

Unit

MHz

%

RCUI3

V

ps

AC Timing Characteristics

Parameter

Description

Min1

PCIe Transmit

UI Unit Interval

399.88

TTX-EYE

TTX-EYE-MEDIAN-to-

MAX-JITTER

TTX-RISE, TTX-FALL

TTX- IDLE-MIN

TTX-IDLE-SET-TO-

IDLE

TTX-IDLE-TO-DIFF-

DATA

TTX-SKEW

PCIe Receive

Minimum Tx Eye Width

Maximum time between the jitter median and maximum

deviation from the median

D+ / D- Tx output rise/fall time

Minimum time in idle

Maximum time to transition to a valid Idle after sending

an Idle ordered set

Maximum time to transition from valid idle to diff data

Transmitter data skew between any 2 lanes

0.7

50

50

UI Unit Interval

399.88

TRX-EYE (with jitter)

TRX-EYE-MEDIUM TO

MAX JITTER

TRX-IDLE-DET-DIFF-

ENTER TIME

TRX-SKEW

Minimum Receiver Eye Width (jitter tolerance)

Max time between jitter median & max deviation

Unexpected Idle Enter Detect Threshold Integration Time

Lane to lane input skew

0.4

Table 9 PCIe AC Timing Characteristics

1. Minimum, Typical, and Maximum values meet the requirements under PCI Specification 1.1

Typical1

400

.9

90

500

400

Max1

400.12

0.15

20

20

1300

400.12

0.3

10

20

Units

ps

UI

UI

ps

UI

UI

UI

ps

ps

UI

UI

ms

ns

11 of 31

April 11, 2007

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 89HPES24NT3.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 89HPES24NT3 | 24-Lane 3-Port Non-Transparent PCI Express Switch | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |