|

|

PDF HCTL2021 Data sheet ( Hoja de datos )

| Número de pieza | HCTL2021 | |

| Descripción | (HCTL2017 / HCTL2021) Quadrature Decoder/Counter Interface ICs | |

| Fabricantes | AVAGO TECHNOLOGIES | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HCTL2021 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

HCTL-2017 and HCTL-2021

Quadrature Decoder/Counter Interface ICs

Data Sheet

Description

Features

The HCTL-2021/2017 is CMOS ICs that performs the

quadrature decoder, counter, and bus interface

function. The HCTL-2021/2017 is designed to improve

system performance in digital closed loop motion

control systems and digital data input systems. It does

this by shifting time intensive quadrature decoder

functions to a cost effective hardware solution. The

HCTL-2021/2017 consists of a quadrature decoder logic,

a binary up/down state counter, and an 8-bit bus

interface. The use of Schmitt-triggered CMOS inputs and

input noise filters allows reliable operation in noisy

environments. The HCTL-2021/2017 contains 16-bit

counter and provides TLL/CMOS compatible tri-state

output buffers. Operation is specified for a temperature

range from –40 to +85°C at clock frequencies up to

33MHz.

The HCTL-2021/2017 provides quadrature decoder

output signals and cascade signals for use with many

standard computer ICs.

The HCTL-2021/2017 is compliant to RoHS directive and

had been declared as a lead free product.

• Interfaces Encoder to Microprocessor

• 33 MHz Clock Operation

• High Noise Immunity:

Schmitt Trigger Inputs and Digital Noise Filter

• 16-Bit Binary Up/Down Counter

• Latched Outputs

• 8-Bit Tristate Interface

• 8 or 16-Bit Operating Modes

• Quadrature Decoder Output Signals, Up/Down and

Count

• Cascade Output Signals, Up/Down and Count

• Substantially Reduced System Software

• 5V Operation (VDD – VSS)

• TTL/CMOS Compatible I/O

• Operating Temperature: -40°C to 85°C

• 16-pin and 20-Pin Launch Pad

Applications

Devices

• Interface Quadrature Incremental Encoders to

Microprocessors

• Interface Digital Potentiometers to Digital Data Input

Buses

Part Number

HCTL-2017

HCTL-2021

Description

33 MHz clock operation. 16-bit counter.

33 MHz clock operation. 16-bit counter. Quadrature decoder output signals.

Cascade output signals.

Pinout

PINOUT A

PINOUT B

1 page

www.DataSheet4U.com

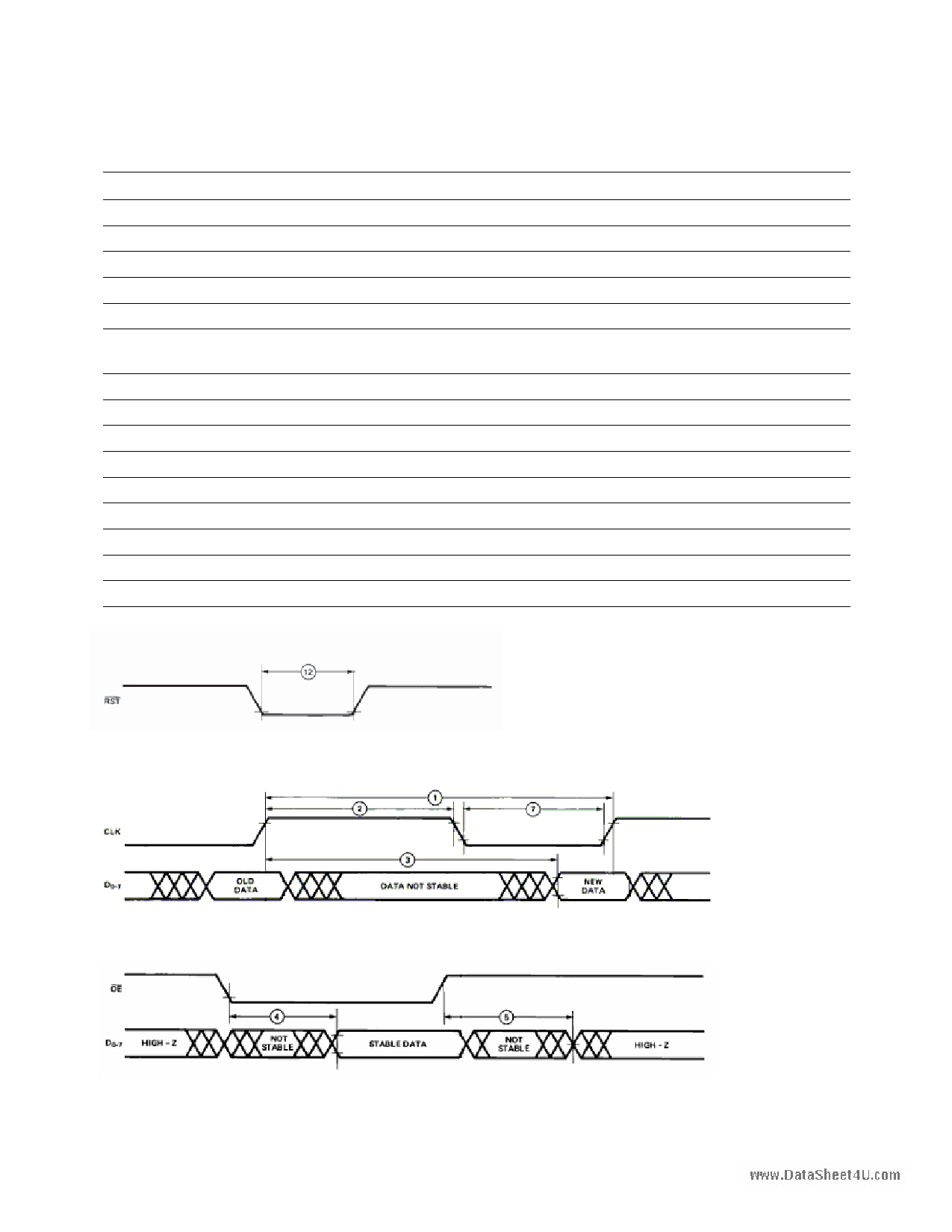

Switching Characteristics

Table 5. Switching Characteristics Max/Min specifications at VDD = 5.0 ? 5%, TA = -40 to +85 OC, CL = 40 pf

Symbol Description

1 tCLK

2 tCHH

3 tCD

Clock Period

Pulse width, clock high

Delay time, rising edge of clock to valid, updated count information on D0-7

4 tODE

Delay time, OE fall to valid data

5 tODZ

6 tSDV

Delay time, OE rise to Hi-Z state on D0-7

Delay time, SEL valid to stable, selected data byte

(delay to High Byte = delay to Low Byte)

7 tCLH

Pulse width, clock low

8 tSS

Setup time, SEL before clock fall

9 tOS

Setup time, OEN before clock fall

10 tSH

Hold time, SEL after clock fall

11 tOH

Hold time, OE after clock fall

12 tRST

Pulse width, RST low

13 tUDD

Delay time, U/D valid after clock rise

14 tCHD

Delay time, CNTDCDR or CNTCAS high after clock rise

15 tCLD

Delay time, CNTDCDR or CNTCAS low after clock fall

Min. Max. Units

30 ns

15 ns

31 ns

29 ns

29 ns

29 ns

15 ns

12 ns

12 ns

0 ns

0 ns

10 ns

4 29 ns

4 31 ns

4 31 ns

Figure 1. Reset Waveform

Figure 2. Waveforms for Positive Clock Edge Related Delays

Figure 3. Tri-State Output Timing

5

5 Page

www.DataSheet4U.com

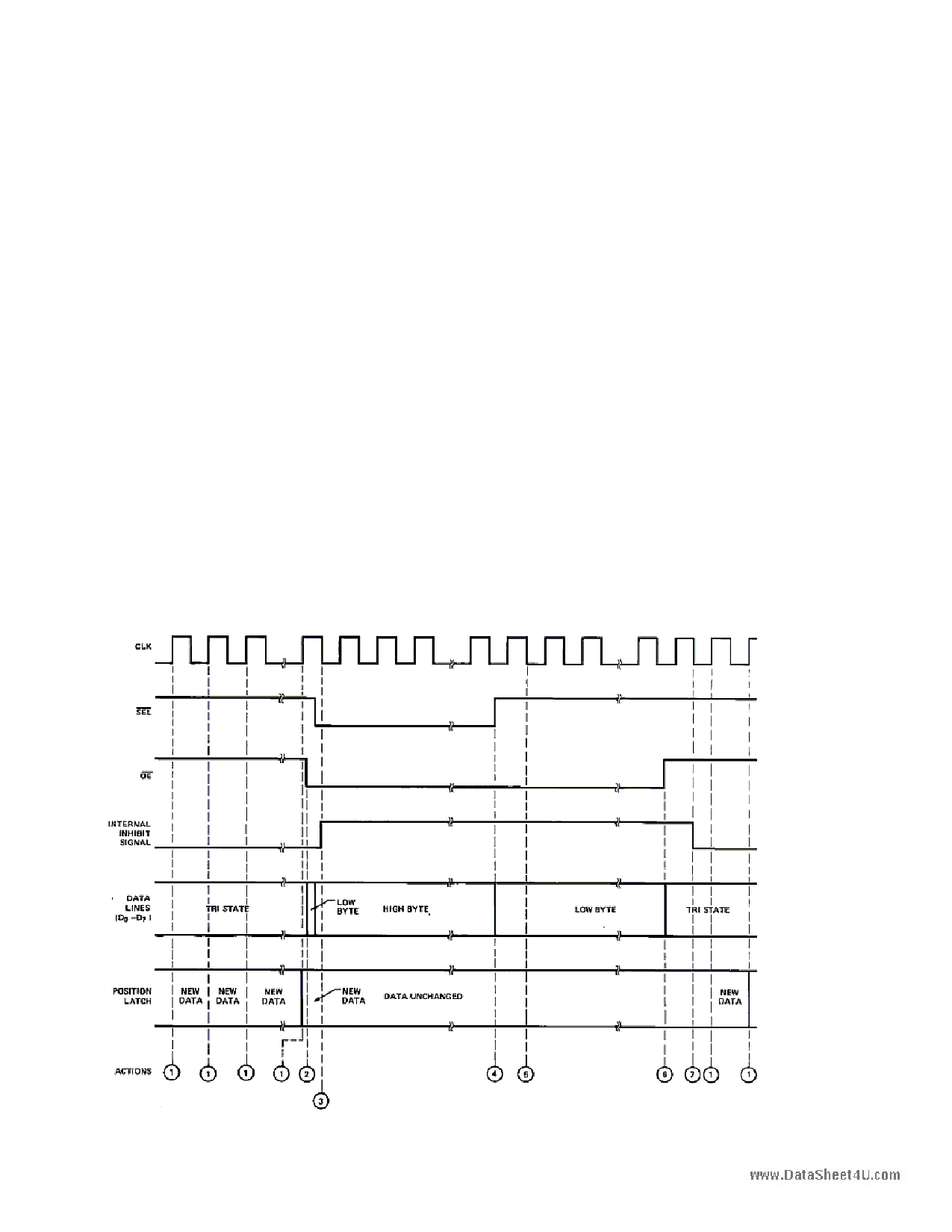

General Interfacing

Actions

The 16-bit latch and inhibit logic allows access to 16

bits of count with an 8-bit bus. When only 8-bits of

count are required, a simple 8-bit (1-byte) mode is

available by holding SEL high continuously. This

disables the inhibit logic. OE provides control of the tri-

state bus, and read timing is shown in Figure 2 and 3.

For proper operation of the inhibit logic during a two-

byte read, OE and SEL must be synchronous with CLK

due to the falling edge sampling of OE and SEL.

The internal inhibit logic on the HCTL-2021/2017

inhibits the transfer of data from the counter to the

position data latch during the time that the latch

outputs are being read. The inhibit logic allows the

microprocessor / microcontroller to first read the high

order 4 or 8 bits from the latch and then read the low

order 8 bits from the latch. Meanwhile, the counter can

continue to keep track of the quadrature states from

the CHA and CHB input signals.

Figure 11 shows the simplified inhibit logic circuit. The

operation of the circuitry is illustrated in the read timing

shown in Figure 13.

1. On the rising edge of the clock, counter data is

transferred to the position data latch, provided the

inhibit signal is low.

2. When OE goes low, the outputs of the multiplexer

are enabled onto the data lines. If SEL is low, then

the high order data bytes are enabled onto the data

lines. If SEL is high, then the low order data bytes

are enabled onto the data lines.

3. When the IC detects a low on OE and SEL during a

falling clock edge, the internal inhibit signal is

activated. This blocks new data from being

transferred from the counter to the position data

latch.

4. When SEL goes high, the data outputs change from

the high byte to the low byte.

5. The first of two reset conditions for the inhibit logic

is met when the IC detects a logic high on SEL and a

logic low on OE during a falling clock edge.

6. When OE goes high, the data lines change to a high

impedance state.

7. The IC detects a logic high on OE during a falling

clock edge. This satisfies the second reset condition

for the inhibit logic.

Figure 13. Typical Interface Timing

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet HCTL2021.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HCTL2020 | (HCTL20xx) Quadrature Decoder/Counter Interface ICs | Hewlett-Packard |

| HCTL2021 | (HCTL2017 / HCTL2021) Quadrature Decoder/Counter Interface ICs | AVAGO TECHNOLOGIES |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |