|

|

PDF NB7V32M Data sheet ( Hoja de datos )

| Número de pieza | NB7V32M | |

| Descripción | 10 GHz/2 Clock Divider | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB7V32M (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

NB7V32M

1.8V / 2.5V, 10GHz ÷2 Clock

Divider with CML Outputs

Multi−Level Inputs w/ Internal

Termination

Description

The NB7V32M is a differential B2 Clock divider with

asynchronous reset. The differential Clock inputs incorporate internal

50 W termination resistors and will accept LVPECL, CML and LVDS

logic levels.

The NB7V32M produces a B2 output copy of an input Clock

operating up to 10 GHz with minimal jitter.

The RESET Pin is asserted on the rising edge. Upon power−up, the

internal flip−flops will attain a random state; the Reset allows for the

synchronization of multiple NB7V32M’s in a system.

The 16 mA differential CML output provides matching internal

50 W termination which guarantees 400 mV output swing when

externally receiver terminated with 50 W to VCC .

The NB7V32M is the 1.8 V/2.5 V version of the NB7L32M

(2.5 V/3.3 V) and is offered in a low profile 3 mm x 3 mm 16−pin

QFN package. The NB7V32M is a member of the GigaComm™

family of high performance clock products. Application notes,

models, and support documentation are available at

www.onsemi.com.

Features

• Maximum Input Clock Frequency > 10 GHz, typical

• Random Clock Jitter < 0.8 ps RMS

• 200 ps Typical Propagation Delay

www.Dat•aS3he5ept4sUT.cyopmical Rise and Fall Times

• Differential CML Outputs, 400 mV Peak−to−Peak, Typical

• Operating Range: VCC = 1.71 V to 2.625 V with GND = 0 V

• Internal 50 W Input Termination Resistors

• QFN−16 Package, 3 mm x 3 mm

• −40°C to +85°C Ambient Operating Temperature

• These are Pb−Free Devices

http://onsemi.com

1

QFN−16

MN SUFFIX

CASE 485G

MARKING

DIAGRAM*

16

1

NB7V

32M

ALYWG

G

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

*For additional marking information, refer to

Application Note AND8002/D.

R

VTCLK

50W

CLK

CLK

50W

VTCLK

VREFAC

RESET

B2

Q

Q

Figure 1. Simplified Logic Diagram

© Semiconductor Components Industries, LLC, 2009

November, 2009 − Rev. 4

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 8 of this data sheet.

1 Publication Order Number:

NB7V32M/D

1 page

NB7V32M

10. VCMR min varies 1:1 with GND, VCMR max varies 1:1 with VCC. The VCMR range is referenced to the most positive side of the differential

input signal.

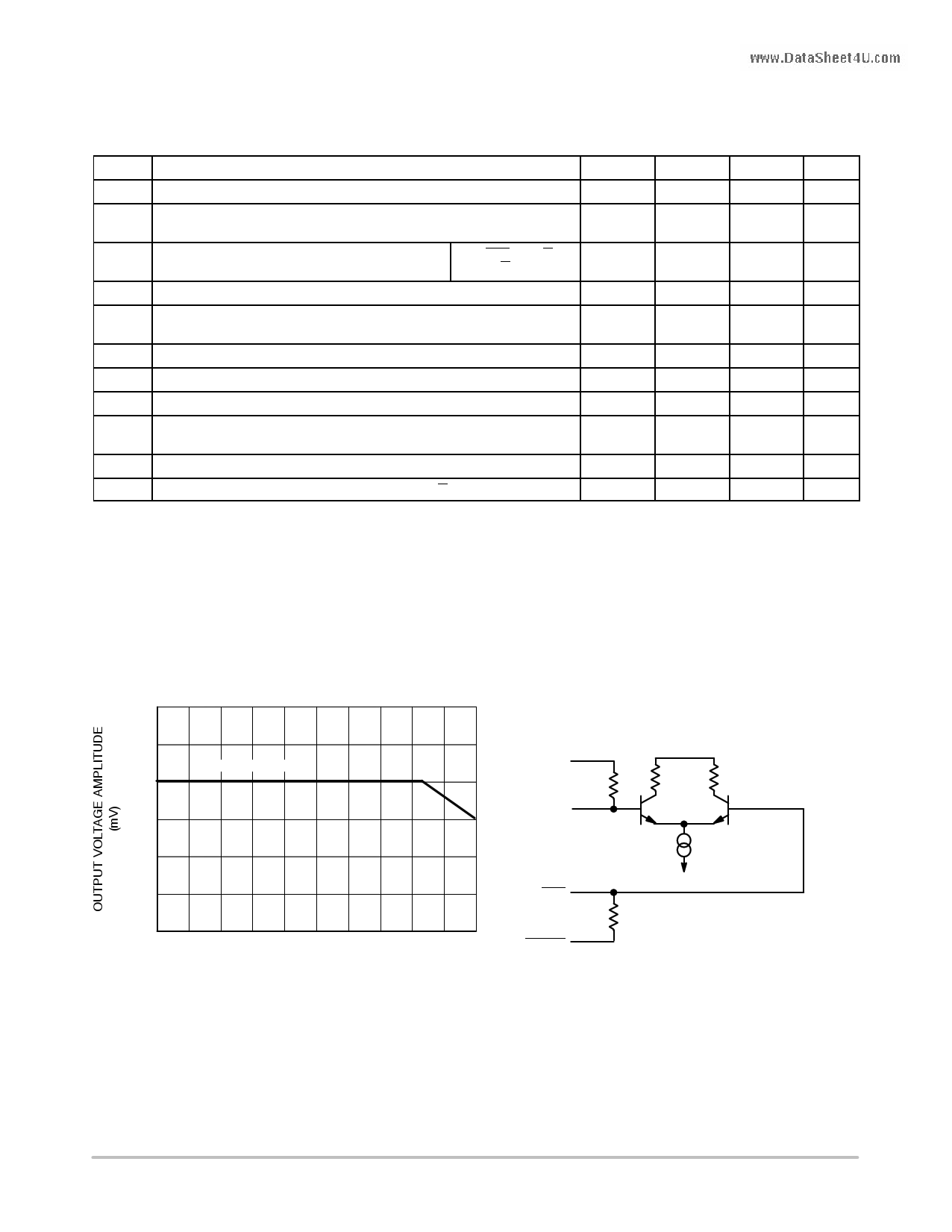

Table 6. AC CHARACTERISTICS VCC = 1.71 V to 2.625 V; GND = 0 V; TA = −40°C to 85°C (Note 11)

Symbol

Characteristic

Min Typ

Max Unit

fMAX

VOUTPP

Maximum Input Clock Frequency

Output Voltage Amplitude (@ VINPPmin)

(Note 12) (Figure 3)

fin ≤ 10GHz

10

280 400

GHz

mV

tPLH,

Propagation Delay to Differential Outputs, @

CLK/CLK to Q, Q

150

200

275 ps

tPHL 1 GHz, measured at differential cross−point

R to Q, Q

200

tPLH TC Propagation Delay Temperature Coefficient

50 Dfs/°C

tskew

Duty Cycle Skew (Note 13)

Device − Device skew (tpdmax – tpdmin)

20 ps

50

tRR Reset Recovery (See Figure 11)

300 135

tPW Minimum Pulse Width R

500 200

tDC Output Clock Duty Cycle (Reference Duty Cycle = 50%) fin v 10 GHz

45 50 55 %

tJITTER RJ – Output Random Jitter (Note 14) fin v 10 GHz

0.2 0.8 ps

RMS

VINPP

tr, tf

Input Voltage Swing (Differential Configuration) (Figure 10) (Note 15)

Output Rise/Fall Times @ 1 GHz (20% − 80%), Q, Q

100

1200

mV

35 60 ps

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

11. Measured using a 1 GHz, VINPPmin, 50% duty−cycle clock source. All output loading with external 50 W to VCC. Input edge rates 40 ps

(20% − 80%).

12. Output voltage swing is a single−ended measurement operating in differential mode.

13. Duty cycle skew is defined only for differential operation when the delays are measured from cross−point of the inputs to the cross−point

of the outputs. Duty cycle skew is measured between differential outputs using the deviations of the sum of Tpw− and Tpw+ @ 1 GHz. Skew

is measured between outputs under identical transitions and conditions.

14. Additive RMS jitter with 50% duty cycle clock signal.

15. Input voltage swing is a single−ended measurement operating in differential mode.

500

www.DataSheet445U0.com

400

350

300

Q AMP (mV)

VTCLK

50 W

CLK

VCC

RC

RC

I

250

200

0

24 68

fin, Clock Input Frequency (GHz)

10

Figure 3. CLOCK Output Voltage Amplitude

(VOUTPP) vs. Input Frequency (fin) at Ambient

Temperature (Typ)

CLK

50 W

VTCLK

Figure 4. Input Structure

http://onsemi.com

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet NB7V32M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB7V32M | 10 GHz/2 Clock Divider | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |