|

|

PDF HE84G752B Data sheet ( Hoja de datos )

| Número de pieza | HE84G752B | |

| Descripción | 8-bit Micro-controller | |

| Fabricantes | King blillion Electronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HE84G752B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

KING BILLION ELECTRONICS CO., LTD

駿億電子股份有限公司

HE84G752B

www.DaHtaES8he0e0t04U4.cSoemries

- Table of Contents -

1. General Description ___________________________________________________________________3

2. Features _____________________________________________________________________________3

3. Functional Block Diagram ______________________________________________________________4

4. Pin Description _______________________________________________________________________4

5. Pad Location _________________________________________________________________________6

6. ROM Map Configurations_____________________________________________________________11

7. LCD Display RAM Map ______________________________________________________________12

7.1. 16 Gray Scale LCD Display RAM Map ________________________________________________14

7.2. 4 Gray Scale LCD Display RAM Map _________________________________________________16

7.3. Black and White LCD Display RAM Map______________________________________________17

8. LCD Power Supply ___________________________________________________________________19

9. LCDC Control register________________________________________________________________21

10. Oscillators ________________________________________________________________________22

11. General Purpose I/O _______________________________________________________________24

12. Timer1 ___________________________________________________________________________26

13. Timer2 ___________________________________________________________________________27

14. Time Base ________________________________________________________________________28

15. Watch Dog Timer __________________________________________________________________29

16. Voice Output ______________________________________________________________________30

17. Low Voltage Detection/Reset _________________________________________________________34

18. Infrared output____________________________________________________________________35

19. Universal Asynchronous Receiver/Transmitter__________________________________________37

19.1. Interface Registers _________________________________________________________________38

19.2. Baud Rate Configuration Register ____________________________________________________38

19.3. Interrupt & Identification Register ___________________________________________________39

19.4. Line Control Register_______________________________________________________________40

19.5. Line Status Register ________________________________________________________________41

January 21, 2005

1

V0.93

This specification is subject to change without notice. Please contact sales person for the latest version before use.

1 page

KING BILLION ELECTRONICS CO., LTD

駿億電子股份有限公司

HE84G752B

www.DaHtaES8he0e0t04U4.cSoemries

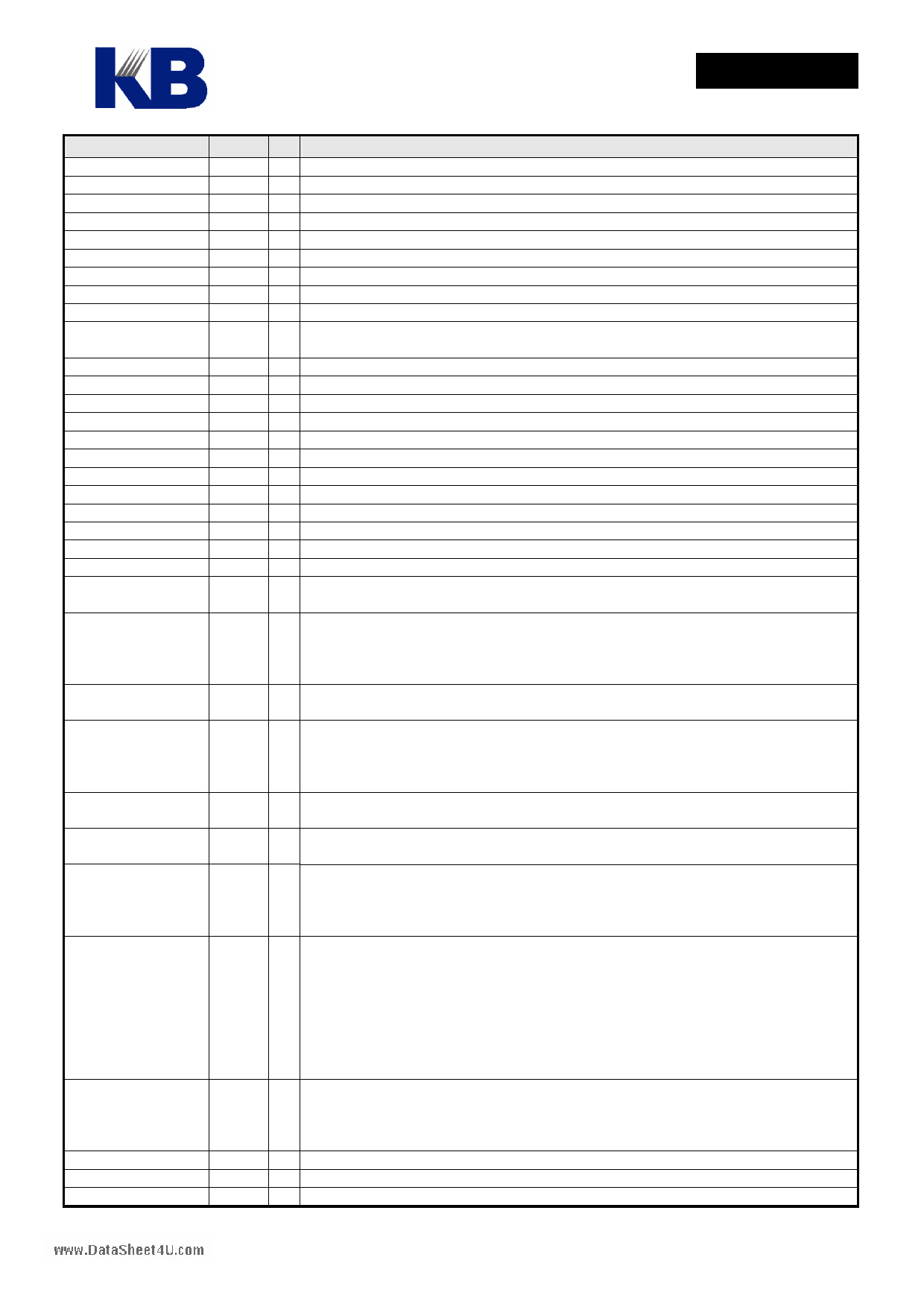

Pin Name

LVL3

LVL4

LVL5

LCAP4A

LCAP2B

LCAP2A

LCAP1A

LCAP1B

LCAP3A

LVREG

LGS1

LVAG

VDD_LCD(VDDA)

GND_LCD(VSSA)

OAC

OCCK

GND

OPO

OPIP

OPIN

DAO

VO

RSTP_N

FXO,

FXI

TSTP_P

SXO,

SXI

VX

VDD

PRT10[7..0]

PRTD[7..2]

PRTD[1]/SIN

PRTD[0]/SOUT

PRTC[7:0]

VDD_RAM

IRO

PWM

Pin # I/O

Description

49 P LCD Bias Voltage 3

50 P LCD Bias Voltage 4

51 P LCD Bias Voltage 5.

52 O Charge Pump Capacitor Pin.

53 O Charge Pump Capacitor Pin.

54 O Charge Pump Capacitor Pin.

55 O Charge Pump Capacitor Pin.

56 O Charge Pump Capacitor Pin.

57 O Charge Pump Capacitor Pin.

58

O

Voltage Regulator Output. VDD is regulated to generate LVREG, which is in turns

pumped to LVP. Adjust resistor between LGS1 and LVREG to set LVREG voltage.

59 I Regulator Voltage Setting

60 O Reference Voltage Output. Fixed 0.9 Volt DC reference voltage

61 P Power supply for LCD charge-pump.

62 P LCD power system ground.

63 O LCD frame signal for interfacing with LCD segment extender KD80.

64 O LCD data load pin for interfacing with LCD segment extender KD80.

65 P Power ground Input.

66 O Output of OP Amp.

67 I Non-inverting input of OP Amp.

68 I Inverting input of OP Amp.

69 O Alternate output of DAC.

70 O DAC Output.

71

I

System Reset input pin. Level trigger, active low on this pin will put the chip in reset

state.

External fast clock pin. Two types of oscillator can be selected by MO_FXTAL (‘0’ for

72, O, RC type and ‘1’ for crystal type). For RC type oscillator, one resistor needs to be

73 B connected between FXI and GND. For crystal oscillator, one crystal needs to be placed

between FXI and FXO. Please refer to application circuit for details.

74

I

Test input pin. Please bond this pad and reserve a test point on PCB for debugging. But

for improving ESD, please connect this point with zero Ohm resistor to GND.

External slow clock pins. Slow clock is clock source for LCD display, TIMER1,

75, O, Time-Base and other internal blocks. Both crystal and RC oscillator are provided. The

76 I slow clock type can be selected by mask option MO_SXTAL. Choose ‘0’ for RC type

and ‘1’ for crystal oscillator.

77

I

Input pin for x32 PLL circuit. Connect to external resistor and capacitors as shown in

application circuit.

78

P

Positive power Input. A 0.1 µF decoupling capacitors should be placed as close to IC

VDD and GND pads as possible for best decoupling effect.

8-bit bi-directional I/O port 10. The output type of I/O pad can also be selected by mask

79~86

B

option MO_10PP[7..0] (‘1’ for push-pull and ‘0’ for open-drain).

As the output structure of I/O pad does not contain tri-state buffer. When using the I/O

pad as input pad, “1” must be outputted before reading.

8-bit bi-directional I/O port D. The output type of I/O pad can also be selected by mask

option MO_DPP[7..0] (‘1’ for push-pull and ‘0’ for open-drain).

As the output structure of I/O pad does not contain tri-state buffer. When using the I/O

87~94

B

as input, ‘1’ must be outputted before reading the pin.

PRTD[7..2] can be used as wake-up pins. PRTD[7..6] can be as external interrupt

sources.

PRTD[1] shares pad with UART Receiver SIN pin.

PRTD[0] shares pad with UART transmitter SOUT pin.

8-bit bi-directional I/O port C. The output type of I/O pad can also be selected by mask

95~102

B

option MO_CPP[7..0] (‘1’ for push-pull and ‘0’ for open-drain).

As the output structure of I/O pad does not contain tri-state buffer. When using the I/O

as input, ‘1’ must be outputted before reading the pin.

103 P Dedicated power input for RAM

104 O The Infrared output.

105 O The PWM output can drive speaker or buzzer directly. Using VDD & PWM to drive

January 21, 2005

5

V0.93

This specification is subject to change without notice. Please contact sales person for the latest version before use.

5 Page

KING BILLION ELECTRONICS CO., LTD

駿億電子股份有限公司

HE84G752B

www.DaHtaES8he0e0t04U4.cSoemries

185 SEG[17] X= -3631.60 Y= 1354.05

186 SEG[16] X= -3731.60 Y= 1354.05

187 SEG[15] X= -3831.60 Y= 1354.05

188 SEG[14] X= -3931.60 Y= 1354.05

6. ROM Map Configurations

The chip has built-in 512K bytes internal ROM. In addition, address and data buses are provided to access

External ROM. The MCU can access up to 4M bytes program ROM and up to 16M bytes data space

through external buses. The SEG[47..40], SEG[39..16] pads are used as either data and address buses for

external ROM or LCD segment driver pads depending on the mask option MO_EXMEM. When the

external ROM mask option is selected, the MCU will retrieve the instructions and data from external

ROM through the address and data buses.

The bit 14 ~ 15 bit of 16-bit logical program address can be mapped to any one (16K bytes per page) of

256 pages through mapping registers PSA1, PSA2, PSA3. As logical page 0 can not be moved and is

always physical page 0, the PSA1 ~ PSA3 contain the physical page addresses of logical pages 1 ~ 3.

Logical Address

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

Page Addr. A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

A[15..14]

00

01

10

11

Logical Page

0

1

2

3

Physical Page Address Physical Address

0 00A[13..0]

PSA1

PSA1+A[13..0]

PSA2

PSA2+A[13..0]

PSA3

PSA3+A[13..0]

Register Address Type

Bits Definition

Reset

PSA1 0x2C R/W A21 A20 A19 A18 A17 A16 A15 A14 0x01

PSA2 0x2D R/W A21 A20 A19 A18 A17 A16 A15 A14 0x02

PSA3 0x2E R/W A21 A20 A19 A18 A17 A16 A15 A14 0x03

January 21, 2005

11

V0.93

This specification is subject to change without notice. Please contact sales person for the latest version before use.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HE84G752B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HE84G752B | 8-bit Micro-controller | King blillion Electronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |