|

|

PDF ZL50402 Data sheet ( Hoja de datos )

| Número de pieza | ZL50402 | |

| Descripción | Managed 2 - Port 10/100 M + 1 - Port 10/100/1000 M Ethernet Switch | |

| Fabricantes | Zarlink Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ZL50402 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ZL50402

Managed 2 - Port 10/100 M +

1 - Port 10/100/1000 M Etherwnwewt.DSatwaShiteceth4U.com

Data Sheet

Features

• Integrated Single-Chip 10/100/1000 Mbps

Ethernet Switch

• Two 10/100 Mbps auto-negotiating Fast

Ethernet (FE) ports with RMII, MII, GPSI,

Reverse MII & Reverse GPSI interface options

• One 10/100/1000 Mbps auto-negotiating port

with GMII & MII interface options, that can be

used as a WAN uplink or as a 9th port

• a 10/100 Mbps Fast Ethernet (FE) CPU port

with Reverse MII interface option

• Embedded 2 Mbits (256 KBytes) internal memory

• supports up to 4 K byte frames

• L2 switching

• MAC address self learning, up to 4 K MAC

addresses using internal table

• Supports IP Multicast with IGMP snooping, up

to 4 K IP Multicast groups

• Supports the following spanning standards

- IEEE 802.1D spanning tree

- IEEE 802.1w rapid spanning tree

• Supports Ethernet multicasting and

broadcasting and flooding control

• VLAN Support

• Supports port-based VLAN and tagged-based

June 2005

Ordering Information

ZL50402GDG

208-Ball LBGA

ZL50402GDG2 208-Ball LBGA*

*Pb Free Tin/Silver/Copper

-40°C to +85°C

VLAN (IEEE 802.1Q), up to 4 K VLANs

• Supports both shared VLAN learning (SVL)

and independent VLAN learning (IVL)

• CPU access supports the following interface

options:

• 8/16-bit parallel and Serial+MII interface in

managed mode

• Serial interface in lightly managed mode, or in

unmanaged mode with optional I2C EEPROM

interface

• Rate Control (both ingress and egress)

• Bandwidth rationing, Bandwidth on demand, SLA

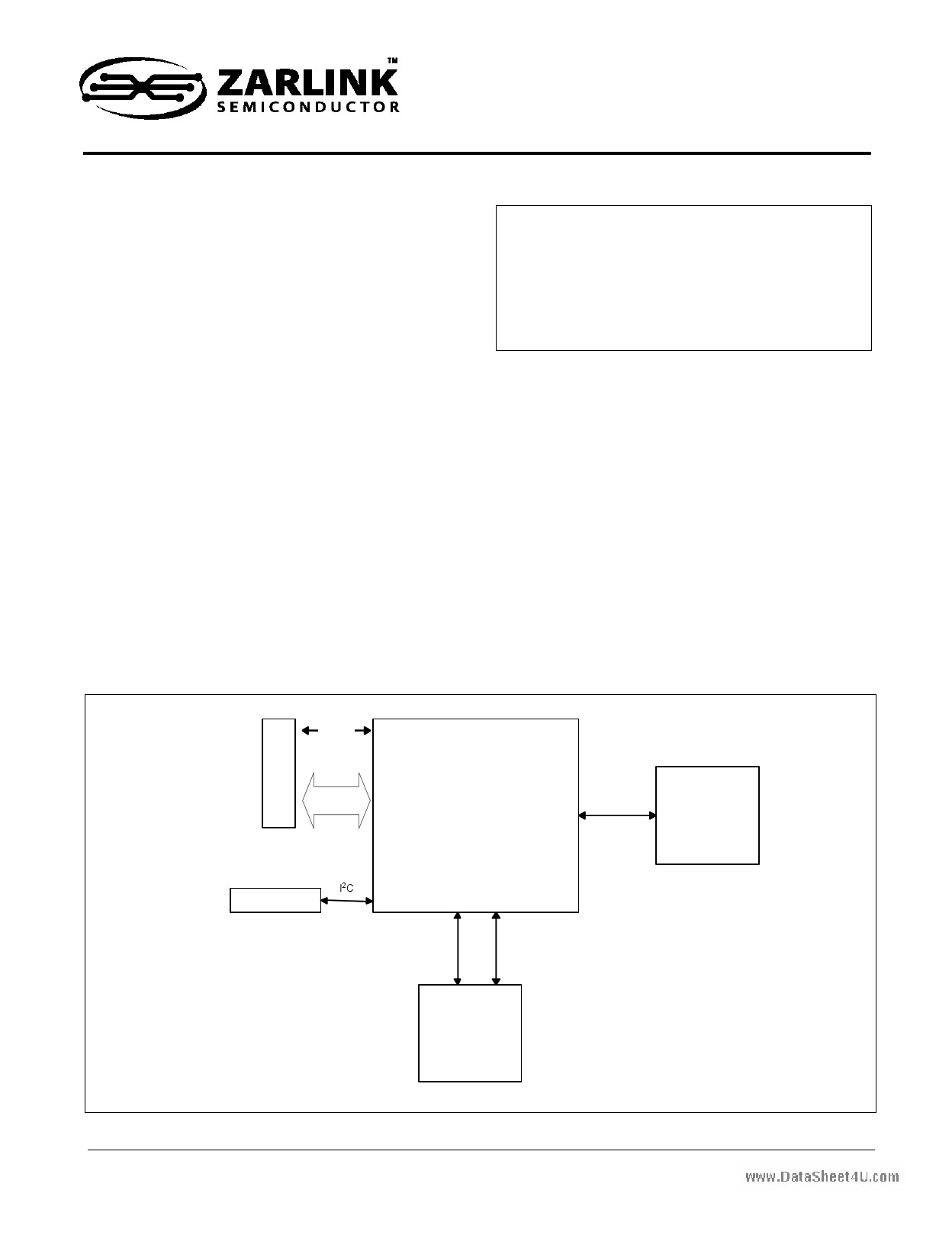

8/16-bit

or

C Serial

P

ZL50402

U MII

GM II/M II

2-Port 10/100M + 1G

Ethernet Switch

EEPROM I2C

10/100/

1000

PHY

RM II / M II/ GPSI

Dual

10/100

PHY

Figure 1 - System Block Diagram

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003-2005, Zarlink Semiconductor Inc. All Rights Reserved.

1 page

ZL50402

Data Sheet

Table of Contents

www.DataSheet4U.com

5.8 Priority Classification Rule. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.9 Port and Tag Based VLAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.9.1 Port-Based VLAN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.9.2 Tag-Based VLAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.9.3 VLAN Stacking (Q-in-Q). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.10 IP Multicast Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.0 Frame Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.1 Data Forwarding Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.2 Frame Engine Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.2.1 FCB Manager. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.2.2 Rx Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.2.3 RxDMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.2.4 TxQ Manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.2.5 Port Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.2.6 TxDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

7.0 Quality of Service and Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

7.1 Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

7.2 Two QoS Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7.2.1 Strict Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.2.2 Weighted Fair Queuing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.3 WRED Drop Threshold Management Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.4 Shaper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

7.5 Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.6 Buffer Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

7.6.1 Dropping When Buffers Are Scarce . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.7 Flow Control Basics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.7.1 Unicast Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.7.2 Multicast Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

7.8 Mapping to IETF Diffserv Classes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

8.0 Traffic Mirroring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

8.1 Mirroring Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

8.2 Using port mirroring for loop back . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

9.0 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.1 Clock Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.1.1 System Clock (SCLK) Speed Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.1.2 RMAC Reference Clock (M_CLK) Speed Requirement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.1.3 GMAC Reference Clock (GREF_CLK) Speed Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.1.4 JTAG Test Clock (TCK) Speed Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.2 Clock Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.2.1 MDC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.2.2 SCL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.2.3 Ethernet Interface Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

10.0 Hardware Statistics Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

10.1 Hardware Statistics Counters List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

10.2 IEEE 802.3 HUB Management (RFC 1516) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

10.2.1 Event Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

10.2.1.1 ReadableOctet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

10.2.1.2 ReadableFrame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

10.2.1.3 FCSErrors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

10.2.1.4 AlignmentErrors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

10.2.1.5 FrameTooLongs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

10.2.1.6 ShortEvents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5

Zarlink Semiconductor Inc.

5 Page

ZL50402

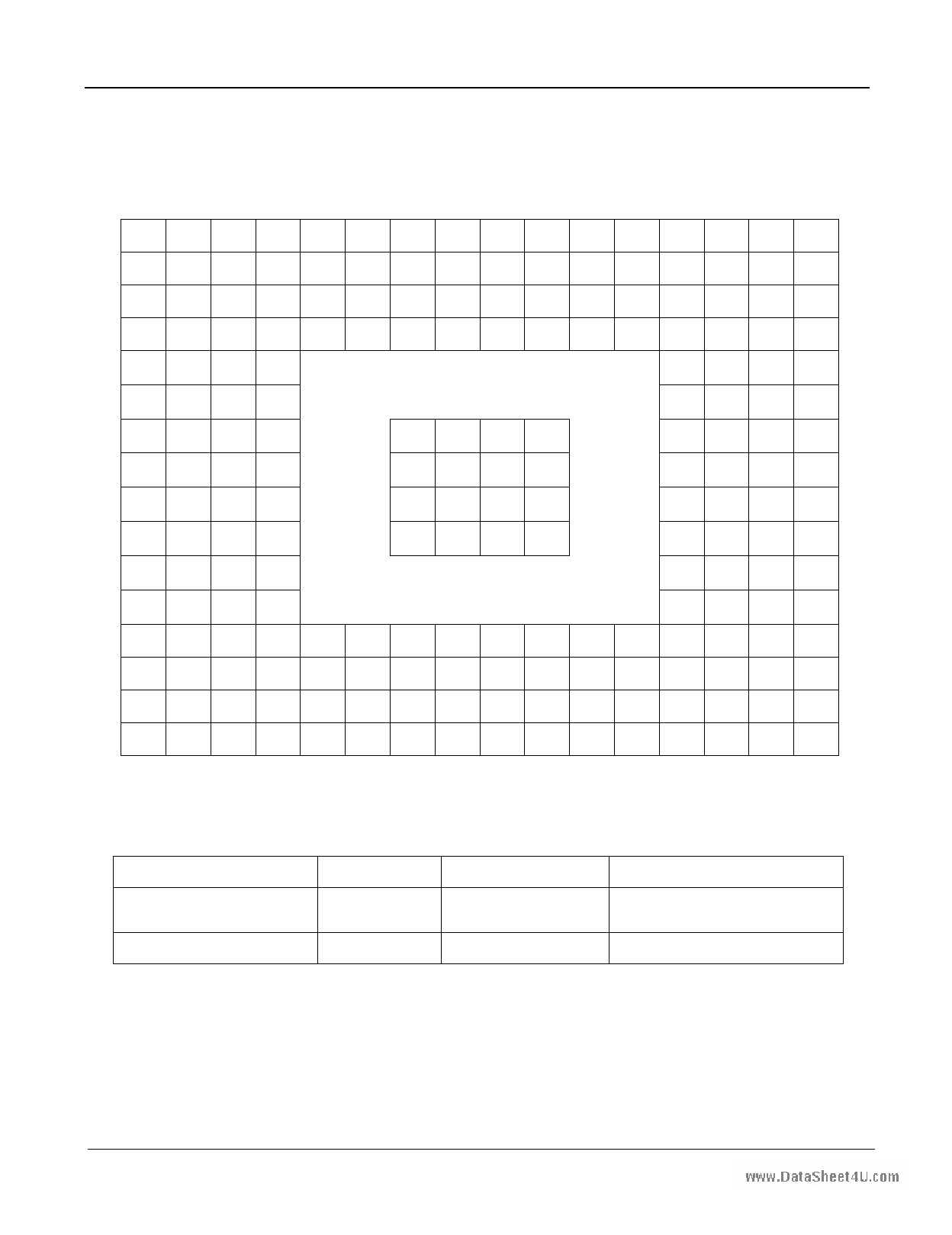

1.0 BGA and Ball Signal Descriptions

1.1 BGA Views (Top-View)

Data Sheet

www.DataSheet4U.com

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

A SCLK

P_CS#

P_RD#

P_WE

#

P_DAT

A1

P_DAT

A3

P_DAT

A5

P_DAT

A7

P_DAT

A9

P_DAT

A11

P_DAT

A13

P_DAT

A15

GREF_

CLK

M9_TX

CLK

M9_M

TXCLK

M9_TX

EN

A

B P_INT

#

P_A0

P_A1

P_A2

P_DAT

A0

P_DAT

A2

P_DAT

A4

P_DAT

A6

P_DAT

A8

P_DAT

A10

P_DAT

A12

P_DAT

A14

TCK

TMS

M9_TX

ER

M9_RX

CK

B

C RESET TSTO

OUT#

UT1

TSTO

UT3

TSTO

UT5

TSTO

UT6

TSTO

UT7

TSTO

UT9

TSTO

UT11

TSTO

UT12

TSTO

UT14

TSTO

UT15

TRST#

TDI

M9_RX

D7

M9_C

RS

M9_C

OL

C

D RESIN TSTO

# UT0

TSTO

UT2

TSTO

UT4

3.3V

IC_GN

D

TSTO

UT8

TSTO

UT10

1.8V

TSTO

UT13

TDO

3.3V

M9_RX

D5

M9_RX

D6

M9_RX

DV

M9_RX

ER

D

E RSVD

M0_C

OL

M1_C

OL

3.3V

3.3V

M9_RX

D4

M9_TX

D6

M9_TX

D7

E

F

M_MD

M_MDI

M0_RX

M0_RX

C O D2 D3

M9_RX

D2

M9_RX

D3

M9_TX

D4

M9_TX

D5

F

G M0_RX M0_RX M0_RX M0_TX

D0 D1 CK D3

GND

GND

GND

GND

M9_RX

D0

M9_RX

D1

M9_TX

D2

M9_TX

D3

G

H M0_C

RS

M0_TX

EN

M0_TX

D2

1.8V

GND

GND

GND

GND

1.8V

RSVD

M9_TX

D0

M9_TX

D1

H

J

M0_TX

M0_TX

M0_TX

M1_RX

D0 D1 CK D3

GND

GND

GND

GND

RSVD

RSVD

RSVD

RSVD

J

K M1_RX M1_RX M1_RX M1_RX

D0 D1 D2 CK

GND

GND

GND

GND

RSVD

RSVD

RSVD

RSVD

K

L M1_C

RS

M1_TX

EN

M1_TX

D2

M1_TX

D3

RSVD

RSVD

RSVD

RSVD

L

M M1_TX M1_TX M1_TX 3.3V

D0 D1 CK

3.3V

RSVD

RSVD

RSVD

M

N RSVD

RSVD

RSVD

RSVD

3.3V

RSVD

1.8V

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N

P RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

P

R RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

M_CLK RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

R

T RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

T

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

1.2 Power and Ground Distribution

G7-10, H7-10, J7-10, K7-10

D5, D12, E4, E13, M4, M13,

N5

D9, H4, H13, N7

GND

3.3V

1.8V

VSS

VCC

VDD

Ground

I/O Power

Core Power

11

Zarlink Semiconductor Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ZL50402.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ZL50400 | Lightly Managed/Unmanaged 9-Port 10/100 M Ethernet Switch | Zarlink Semiconductor |

| ZL50402 | Managed 2 - Port 10/100 M + 1 - Port 10/100/1000 M Ethernet Switch | Zarlink Semiconductor |

| ZL50404 | Lightly Managed/Unmanaged 5-Port 10/100 M Ethernet Switch | Zarlink Semiconductor |

| ZL50405 | Managed5-Port 10/100 M Ethernet Switch | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |