|

|

PDF NJU3610 Data sheet ( Hoja de datos )

| Número de pieza | NJU3610 | |

| Descripción | 1bit Delta-Sigma Stereo ADC | |

| Fabricantes | NJR | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NJU3610 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

NJU3610www.DataSheet4U.com

Confidential

1bit Delta-Sigma Stereo ADC

General Description

The NJU3610 is the stereo Analog to Digital Convector (ADC) that covers from 8

to 192 kHz sampling frequency. The NJU3610 provides 1bit Delta-Sigma

technology with high accuracy and low power consumption. The analog inputs are

differential signal and stereo 4-1 selectors are provided. The NJU3610 provides two

power-supply 1.8V / 3.3V(typical) or single power-supply 3.3V(typical) application.

Package

Features

NJU3610FR3

1bit Delta-Sigma stereo ADC

64fs over sampling (MCK=256fs, 384fs)

32fs over sampling (MCK=128fs)

Digital Filter

High-pass filter

Stereo 4-1 selectors

Sampling Rate

: 8 to 192kHz

Dynamic Range

: 100dB([email protected], 96kHz)

S/N : 100dB([email protected], 96kHz)

S/(N+D)

: 90dB([email protected], 48kHz, -1.0dBFS)

Master Clock

: 128fs(8 to 192kHz), 256fs / 384fs(8 to 96kHz)

Power Supply

: Single power supply 3.0 to 3.6V(3.3Vtyp) Built-in regulator using together

: Two power supply 3.0 to 3.6V(Analog, I/O:3.3Vtyp)

Digital Audio Format

1.65 to 2.0V(Digital:1.8Vtyp)

: 24/16bit Left-justified, I2S Master/Slave

Operating Temperature

: -40 to +85 C

Package

: LQFP48-R3 (Pb-Free)

Ver.2009.12.4

-1-

1 page

NJU3610www.DataSheet4U.com

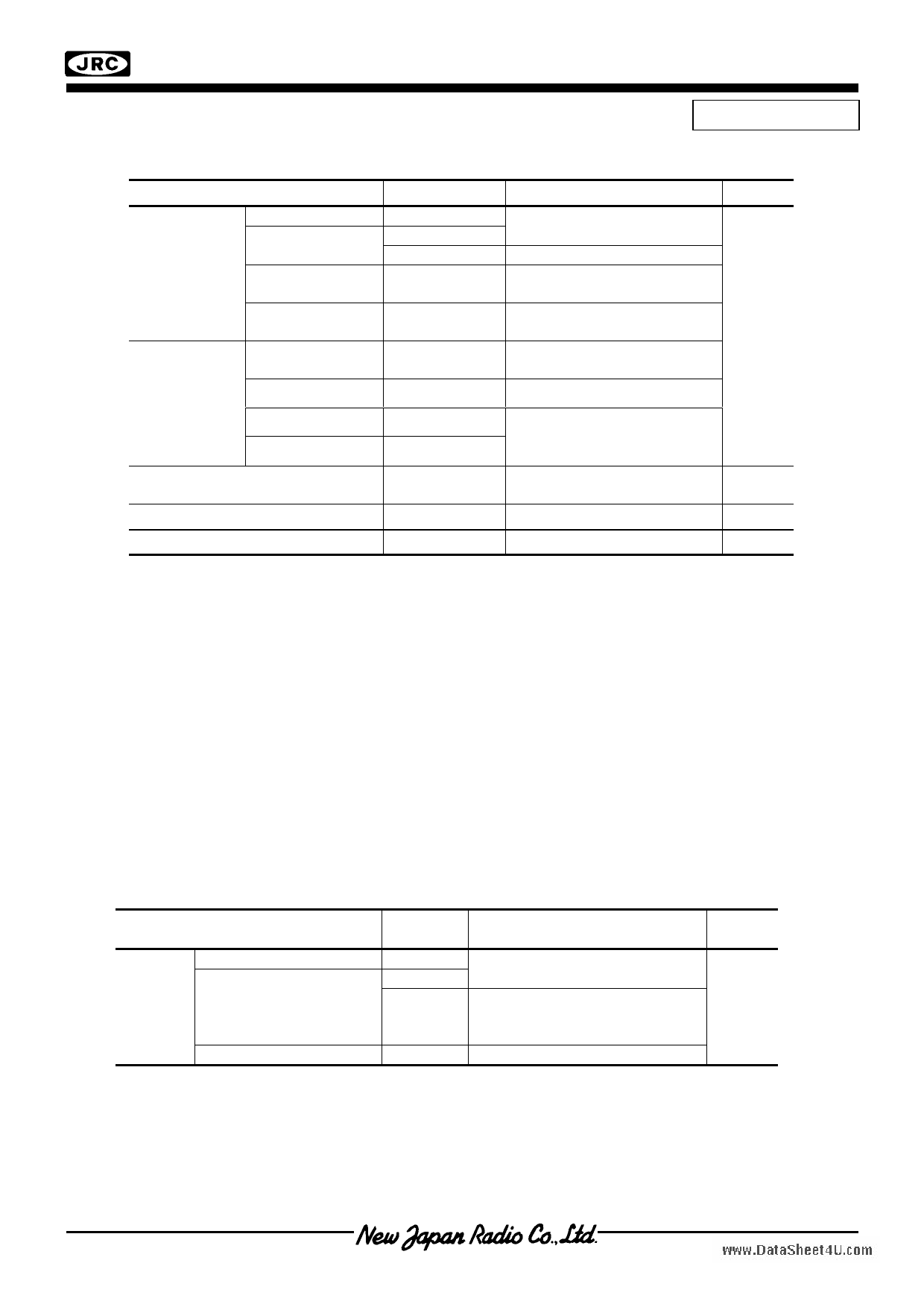

Absolute Maximum Ratings

Table 2. Absolute Maximum Ratings

Parameter

Analog

Digital

Power supplies

Built-in Regulator

Input

Built-in Regulator

Output

Digital Input

Pin Voltage

Digital Output

Analog Input

VCOM Output

Power Dissipation

Operating Temperature

Storage Temperature

Symbol

AVDD

VDD33

VDD18

VREGI

VREGO

Vx(IN)

Vx(OUT)

Vx(AIN)

Vx(VCOM)

PD

TOPR

TSTR

Confidential

(VSS=AVSS=0V=GND, Ta=25 C)

Rating

Units

-0.3 to +4.2

-0.3 to +2.3

-0.3 to +4.2

-0.3 to +2.3

-0.3 to +5.5 (VDD33‡3.0V)

-0.3 to +4.2 (VDD33<3.0V)

-0.3 to VDD33 + 0.3

V

-0.3 to AVDD + 0.3

800

Mounted on two-layer board of based on the JEDEC.

-40 to +85

-40 to +125

mW

C

C

* AVDD

* VDD33

* VDD18

* VREGI

* VREGO

* VX(IN)

* VX(OUT)

* VX(AIN)

* VX(VCOM)

: 8, 29, 42pin

: 9pin

: 18pin

: 11pin

: 12pin

: 16, 20-28pin, and 14-15pin (set in the state of the input.)

: 13pin, and 14-15pin (set in the state of the output.)

: 1-6, 31-40, 44-48pin

: 41pin

Note 1)

Note 2)

If the LSI is used on condition beyond the absolute maximum rating, the LSI may be destroyed. Using

LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the

electrical characteristics conditions will cause malfunction and poor reliability.

Please do not open the digital input terminal. Moreover, please do not open the digital I/O terminal set

in the state of the input.

Recommended operating conditions

Table 3. Recommended operating conditions

Parameter

Analog

Power

Supplies

Digital

Symbol

AVDD *1

VDD33 *1

VDD18 *2

Built-in Regulator Input VREGI *3

Recommended operating

conditions

3.0 to 3.6

AVDD33‡VDD33

1.65 to 2.0

(Or, a built-in regulator supplies

the voltage.)

3.0 to VDD33

Units

V

*1 VDD33 is recommended to be turned on from AVDD and simultaneous or AVDD back.

*2 The power up sequence VDD18 is not critical.

*3 When a built-in regulator is used, VREGI is connected with VDD33. When a built-in regulator is not used,

VREGI and VREGO are connected with VSS.

Ver.2009.12.4

-5-

5 Page

NJU3610www.DataSheet4U.com

2. ADC Function

Confidential

2.1 Clock and Digital Audio Interface

The NJU3610 requires MCK, BCK and LRCK audio clock. BCK and LRCK can be generated by MCK in Master

mode. MCK, BCK and LRCK are synchronized in Master mode.

In Slave mode, BCK and LRCK are inputted from the outside. In Slave mode, MCK, BCK and LRCK should be

synchronized. But it is not necessary that the phase of these three clocks are synchronized.

MCK frequency should be one of 128fs, 256fs or 384fs. If fs>96KHz, MCK should be 128fs. The ADC operates

with the next frequency. The operate frequency is 64fs in case of fs 96KHz. The operate frequency is 32fs in case

of fs>96KHz.

Mode0 and mode1 terminals select the MCK frequency and ADC operating frequency.

In case that ADC operating frequency is 32fs, the effective bandwidth is 1/4fs. Between 1/4fs and 1/2fs, ADC

shaping noise exists.

The NJU3610 digital audio format provides Left-justified and I2S 24bit(BCK=64clocks/fs) in Master mode. The

NJU3610 digital audio format provides Left-justified, I2S 16bit (BCK=32clocks/fs) and I2S 24bit(BCK=64clocks/fs)

in Slave mode.

FMT0 and FMT1 terminals select the above digital audio format. When FMT0, FMT1, MODE0 and MODE1 are

changed, RESET should be done again.

MCK, BCK and LRCK frequency is shown in table11. Digital Audio Format and operation mode is shown in table12.

In Master mode, BCK and LRCK terminals generate clocks. BCK output clock is fixed at 64fs in Master mode. In

Slave mode, BCK and LRCK terminals are assigned input.

Table 11. MCK, BCK, LRCK (1)

LRCK(kHz)

Master: Generation from MCK

Slave: From outside

8

16

22.05

32

44.1

48

64

88.2

96

176.4 *1

192 *1

MCK (MHz)

128fs

-*2

-*2

-*2

-*2

-*2

-*2

-*2

-*2

-*2

22.5792

24.576

256fs

2.048

4.096

5.6448

8.192

11.2896

12.288

16.384

22.5792

24.576

-

-

384fs

3.072

6.144

8.4672

12.288

16.9344

18.432

24.576

33.8688

36.864

-

-

BCK(MHz)

32fs

Slave only: from outside

0.256

0.512

0.7056

1.024

1.4112

1.536

2.048

2.8224

3.072

5.6448

6.144

64fs

Master: Generation from MCK

Slave: From outside

0.512

1.024

1.4112

2.048

2.8224

3.072

4.096

5.6448

6.144

11.2896

12.288

*1 It is only a setting of “CKMODE[1:0]=10,11”. At this time, frequency bandwidth is up to 1/4fs.

The shaping noise of the ADC is included in the band from 1/4fs to 1/2fs.

*2 Because an effective bandwidth is limited, it is not practicable.

Ver.2009.12.4

- 11 -

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet NJU3610.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NJU3610 | 1bit Delta-Sigma Stereo ADC | NJR |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |