|

|

PDF HMP525F7FFP4C-xx Data sheet ( Hoja de datos )

| Número de pieza | HMP525F7FFP4C-xx | |

| Descripción | 240pin Fully Buffered DDR2 SDRAM DIMMs | |

| Fabricantes | Hynix Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HMP525F7FFP4C-xx (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

www.DataSheet4U.net

240pin Fully Buffered DDR2 SDRAM DIMMs based on 512 Mb F-ver.

This Hynix’s Fully Buffered DIMM is a high-bandwidth & large capacity channel solution that has a narrow

host interface. Hynix’s FB-DIMM features novel architecture including the Advanced Memory Buffer that

isolates the DDR2 SDRAMs from the channel. This single component located in the front side center of

each DIMM, acts as a repeater and buffer for all signals and commands which are exchanged between the

host controller and the DDR2 SDRAMs including data in and output. The AMB communicates with the host

controller and adjacent DIMMs on a system board using an industry standard Differential Point to Point

Link Interface at 1.5V power.

The AMB also allows buffering of memory traffic to support large memory capacities. All memory control

for the DDR2 SDRAM devices resides in the host, including memory request initiation, timing, refresh,

scrubbing, sparing, configuration access and power management. The AMB interface is responsible for

handling channel and memory requests to and from the local FBDIMM and for forwarding request to other

FBDIMMs on the memory channel.

FEATURES

• 240 pin Fully Buffered ECC dual In-Line DDR2 SDRAM Module

• JEDEC standard Double Data Rate2 Synchronous DRAMs (DDR2 SDRAMs) with 1.8V +/- 0.1V Power Supply

• All inputs and outputs are compatible with SSTL_1.8 interface

• Built with 512Mb DDR2 SDRAMs in 60ball FBGA

• Host interface and AMB component industry standard compliant

• MBIST & IBIST test functions

• 4 Bank architecture

• OCD (Off-Chip Driver Impedance Adjustment)

• ODT (On-Die Termination)

• Fully differential clock operations (CK & CK)

• Programmable Burst Length 4 / 8 with both sequential and interleave mode

• Auto refresh and self refresh supported

• 8192 refresh cycles / 64ms

• Serial presence detect with EEPROM

• 133.35 x 30.35 mm form factor

• RoHS compliant

• Full Module Heat Spreader

This document is a general product description and is subject to change without notice. Hynix Semiconductor does not assume any

responsibility for use of circuits described. No patent licenses are implied.

Rev 1.2 / Feb. 2009

1

1 page

www.DataSheet4U.net

1240pin Fully Buffered DDR2 SDRAM DIMMs

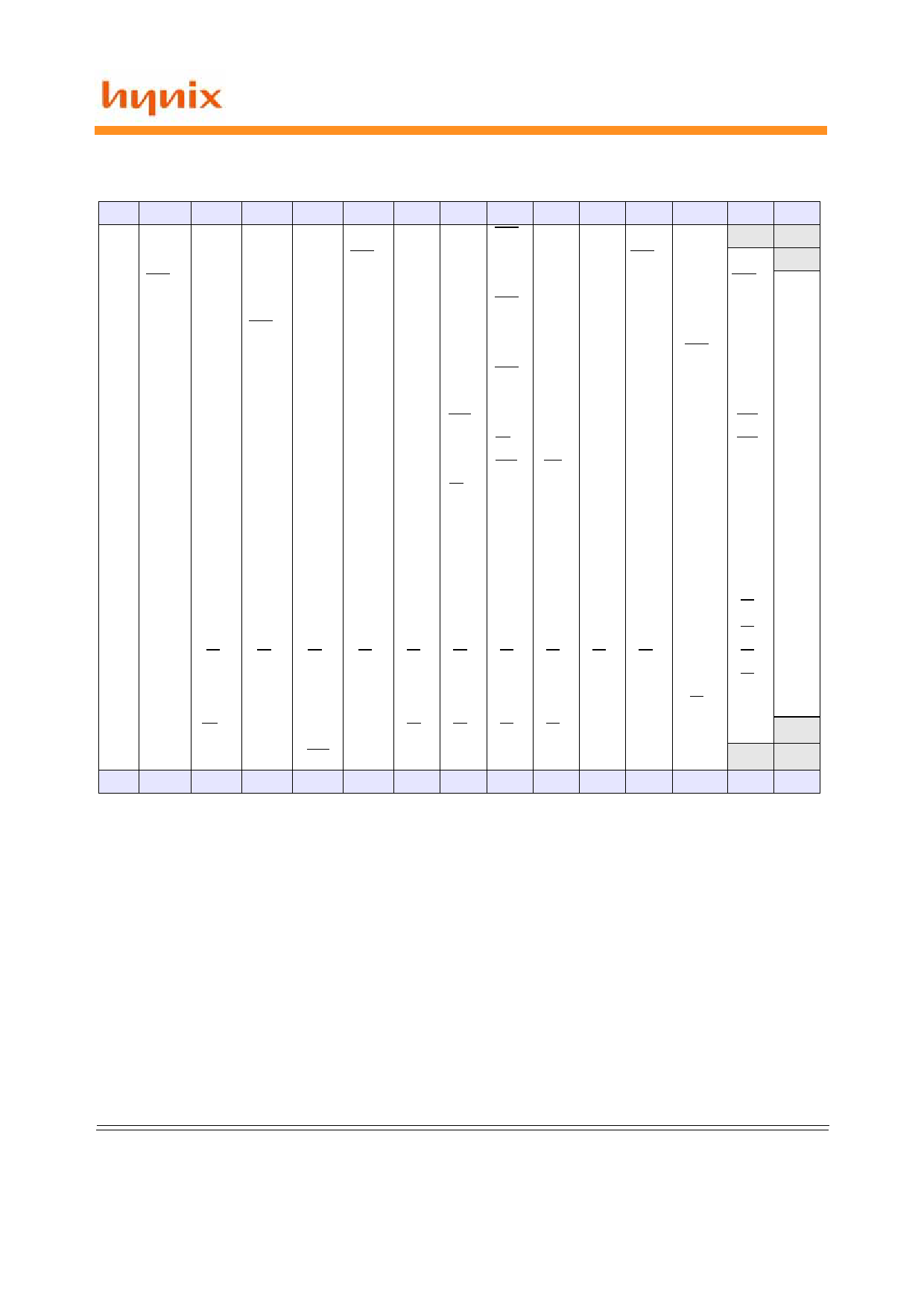

FUNCTIONAL BLOCK DIAGRAM

512MB(64Mbx72) ECC FB-DIMM

/S0

DQS0

/DQS0

DQS9

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D0

DQS /DQS

DQS1

/DQS1

DQS10

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D1

DQS /DQS

DQS2

/DQS2

DQS11

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D2

DQS /DQS

DQS3

/DQS3

DQS12

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D3

DQS /DQS

All address/command/control/clock

VTT

Serial PD

SCL

SCL U0

SDA

WP A0 A1 A2

SA0 SA1 SA2

SDA

VTT

VCC

VDD SPD

VDD

VREF

VSS

DQS4

/DQS4

DQS13

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D4

DQS /DQS

DQS5

/DQS5

DQS14

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D5

DQS /DQS

DQS6

/DQS6

DQS15

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D6

DQS /DQS

DQS7

/DQS7

DQS16

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D7

DQS /DQS

DQS8

/DQS8

DQS17

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DM

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NU /CS

/RDQS

D8

DQS /DQS

PN0-PN13

SN0-SN13

/PN0-/PN13

/SN0-/SN13

Terminators

AMB

Serial PD,AMB

PS0-PS9

SS0-SS9

/PS0-/PS9

A /SS0-/SS9

DQ0-DQ63

CB0-CB7

M

B

/S0-/CS(all SDRAMs)

CKE0 -> CKE

DQS0-DQS17

DO-D8, AMB

/DQS0-/DQS8

ODT -> ODT

DO-D8

SCL

SDA

BA0-BA2

SA0-SA2

A0-A15

DO-D8,SPD, AMB

/RESET

/RAS

/CAS

/WE

SCK/ /SCK

CK/ /CK

Notes :

1. DQ-to-I/O wiring may be changed within a byte.

2. There are two physical copies of each address/command/control/clock.

Rev 1.2 / Feb. 2009

5

5 Page

www.DataSheet4U.net

1240pin Fully Buffered DDR2 SDRAM DIMMs

Right Side

16 17 18 19 20 21 22 23 24 25 26 27 28 29

A VDD TEST VDD DQ52 DQS15 VDD DQ49 DQS6 VDD DQ48 DQ38 VDD

B VDD TEST DDRC VSS DQS15 DQ53 VSS DQS6 DQ50 VSS DQS13 DQS13 VSS

C DQS17 VSS DDRC DQ54 VSS DQ55 DQ51 VSS DQS7 DQ56 VSS DQ46 DQS14 VDD

D CB6 CB7 VSS DQS16 DQ63 VSS DQ59 DQS7 VSS DQ36 DQ44 VSS DQS14 DQ47

E VSS CB5 DQS16 VSS DQ61 DQ57 VSS DQ58 DQ39 VSS DQ33 DQ45 VSS DQ41

F CB4 VDD DQ62 DQ60 VSS TEST TEST VSS DQ37 DQ35 VSS DQS5 DQ43 VSS

G TESTLO RFU RFU

NC

NC NC DQS4 DQS4 VSS NC NC

NC DQS5 DQ40

H VSS VDD VSS NC

NC NC VSS DQ34 DQ32 NC NC

NC VSS DQ42

J VDD VSS VDD NC

NC NC RASB VSS RFU NC NC

NC CLK3 VSS

K VSS VCC VSS NC

NC NC ODT0B CS1B VSS NC NC

NC CLK1 CLK3

L VCC VSS VCC NC

NC NC VSS CASB WEB NC NC

NC VSS CLK1

M VSS VCC VSS NC

NC NC CS0B VSS BA1B NC NC

NC CKE0B VSS

N VCC VSS VCC NC

NC NC A0B A2B VSS NC NC

NC BA0B BA2B

P VSS VCC VSS NC

NC NC VSS A4B A1B NC NC

NC VSS CKE1B

R VCC VSS VCC NC

NC NC A6B VSS A10B NC NC

NC A3B VSS

T VSS VCC VSS NC

NC NC A11B A9B VSS NC NC

NC A7B A5B

U VSS VCCFBD RFU NC NC NC A8B A15B A14B SA0 SCL SDA PS8 PS8

V VCCFBD VSS VCCFBD VSS VCCFBD RFUa RFUa VSS A13B A12B SA2 SA1 PS7 PS7

W VSS SS0 SS1 SS2 SS3 SS4 SS9 SS5 SS6 SS7 SS8 VSS PS6 PS6

Y VSS SS0 SS1 SS2 SS3 SS4 SS9 SS5 SS6 SS7 SS8 VSS PS5 PS5

AA VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS PS9 PS9 VSS

AB VSS SN11 VSS SCK TESTLO PS0 PS1 PS2 PS3 PS4 RFUa VDDSPD VSS

AC RFU SN11 VSS SCK TESTLO PS0 PS1 PS2 PS3 PS4 RFUa VSS

16 17 18 19 20 21 22 23 24 25 26 27 28 29

NC= No Connect, RFU= Reserved for Future Use.

Note:

a. These pin positions are reserved for forwarded clocks to be used in future AMB implementations

Rev 1.2 / Feb. 2009

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet HMP525F7FFP4C-xx.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HMP525F7FFP4C-xx | 240pin Fully Buffered DDR2 SDRAM DIMMs | Hynix Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |