|

|

PDF W947D2HB Data sheet ( Hoja de datos )

| Número de pieza | W947D2HB | |

| Descripción | (W947D2HB / W947D6HB) 128Mb Mobile LPDDR | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W947D2HB (archivo pdf) en la parte inferior de esta página. Total 60 Páginas | ||

|

No Preview Available !

www.DataSheet.co.kr

W947D6HB / W947D2HB

128Mb Mobile LPDDR

TABLE OF CONTENTS

1. GENERAL DESCRIPTION.......................................................................................................... 4

2. FEATURES.................................................................................................................................. 4

3. PIN CONFIGURATION................................................................................................................ 5

3.1 Ball Assignment: LPDDR X16 ..........................................................................................................5

3.2 Ball Assignment: LPDDR X32 ..........................................................................................................5

4. PIN DESCRIPTION ..................................................................................................................... 6

4.1 Signal Descriptions...........................................................................................................................6

4.2 Addressing Table .............................................................................................................................7

5. BLOCK DIAGRAM ...................................................................................................................... 8

5.1 Block Diagram ..................................................................................................................................8

5.2 Simplified State Diagram ..................................................................................................................9

6. FUNCTION DESCRIPTION....................................................................................................... 10

6.1 Initialization ....................................................................................................................................10

6.1.1 Initialization Flow Diagram ....................................................................................................................11

6.1.2 Initialization Waveform Sequence.........................................................................................................12

6.2 Register Definition ..........................................................................................................................12

6.2.1 Mode Register Set Operation................................................................................................................12

6.2.2 Mode Register Definition .......................................................................................................................13

6.2.3. Burst Length .........................................................................................................................................13

6.3 Burst Definition ...............................................................................................................................14

6.4 Burst Type......................................................................................................................................15

6.5 Read Latency .................................................................................................................................15

6.6 Extended Mode Register Description .............................................................................................15

6.6.1 Extended Mode Register Definition ......................................................................................................16

6.7 Status Register Read .....................................................................................................................16

6.7.1 SRR Register (A[n:0] = 0) .....................................................................................................................17

6.7.2 Status Register Read Timing Diagram .................................................................................................18

6.8 Partial Array Self Refresh ...............................................................................................................19

6.9 Automatic Temperature Compensated Self Refresh.......................................................................19

6.10 Output Drive Strength...................................................................................................................19

6.11 Commands...................................................................................................................................19

6.11.1 Basic Timing Parameters for Commands ...........................................................................................19

6.11.2 Truth Table - Commands ....................................................................................................................20

6.11.3 Truth Table - DM Operations ..............................................................................................................21

6.11.4 Truth Table - CKE ...............................................................................................................................21

6.11.5 Truth Table - Current State BANKn - Command to BANKn ...............................................................22

6.11.6 Truth Table - Current State BANKn, Command to BANKn.................................................................23

7. OPERATION.............................................................................................................................. 24

7.1. Deselect ........................................................................................................................................24

7.2. No Operation .................................................................................................................................24

7.2.1 NOP Command .....................................................................................................................................25

-1-

Publication Release Date:Jun,17, 2011

Revision A01-003

Datasheet pdf - http://www.DataSheet4U.net/

1 page

www.DataSheet.co.kr

W947D6HB / W947D2HB

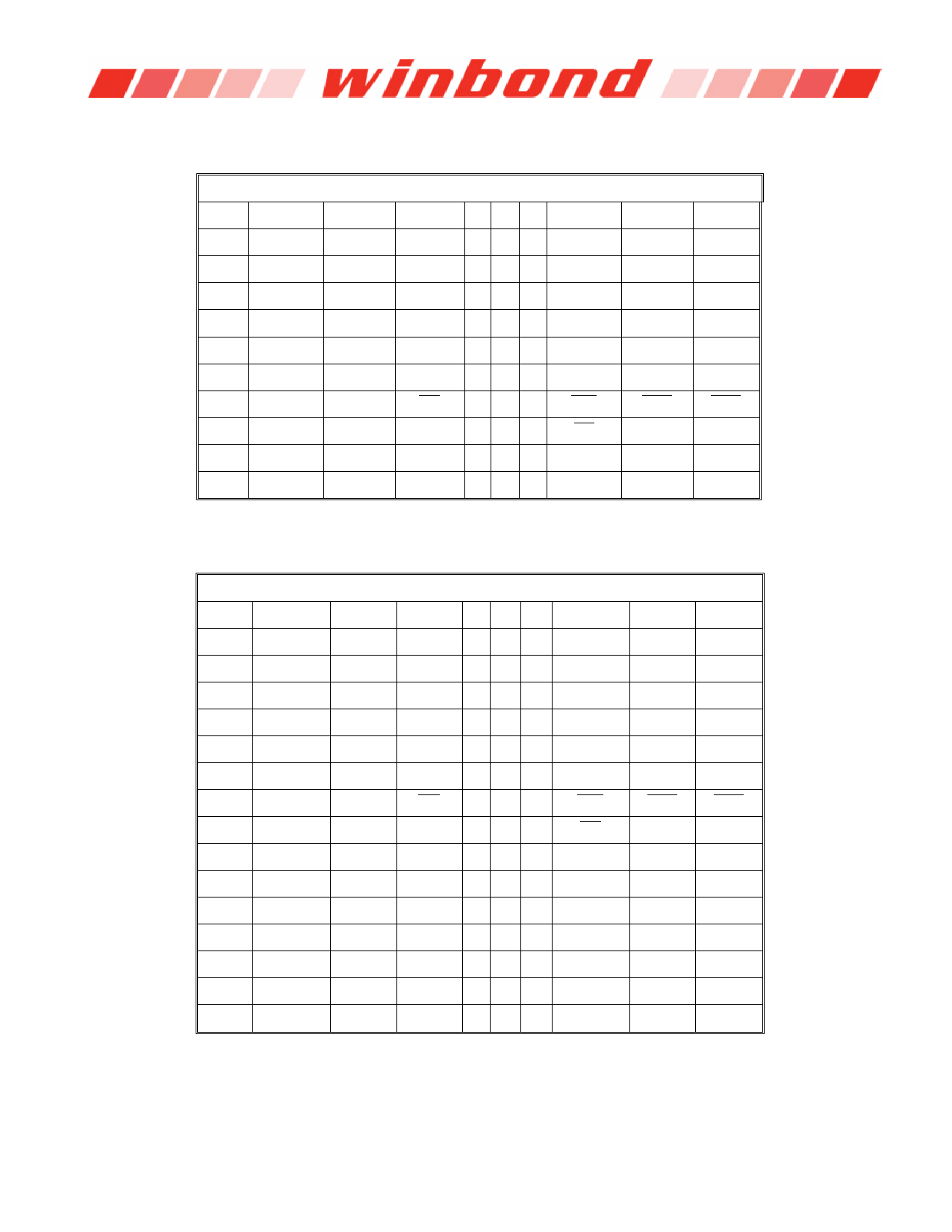

3. PIN CONFIGURATION

3.1 Ball Assignment: LPDDR X16

60 BALL VFBGA

1 2 3 456 7

A VSS DQ15 VSSQ

VDDQ

B VDDQ DQ13 DQ14

DQ1

C VSSQ DQ11 DQ12

DQ3

D VDDQ DQ9 DQ10

DQ5

E VSSQ UDQS DQ8

DQ7

F VSS UDM NC

NC

G CKE CK CK

WE

H A9 A11 NC

CS

J A6 A7 A8

A10/AP

K VSS

A4

A5

A2

(Top View) Pin Configuration

128Mb Mobile LPDDR

8

DQ0

DQ2

DQ4

DQ6

LDQS

LDM

CAS

BA0

A0

A3

9

VDD

VSSQ

VDDQ

VSSQ

VDDQ

VDD

RAS

BA1

A1

VDD

3.2 Ball Assignment: LPDDR X32

90 BALL VFBGA

1

2

3 45 6

7

A VSS DQ31 VSSQ

VDDQ

B VDDQ DQ29 DQ30

DQ17

C VSSQ DQ27 DQ28

DQ19

D VDDQ DQ25 DQ26

DQ21

E VSSQ DQS3 DQ24

DQ23

F VDD DM3 NC

NC

G CKE CK CK

WE

H A9 A11 NC

CS

J A6 A7 A8

A10/AP

K A4 DM1 A5

A2

L VSSQ DQS1 DQ8

DQ7

M VDDQ DQ9 DQ10

DQ5

N VSSQ DQ11 DQ12

DQ3

P VDDQ DQ13 DQ14

DQ1

R VSS DQ15 VSSQ

VDDQ

(Top View) Pin Configuration

8

DQ16

DQ18

DQ20

DQ22

DQS2

DM2

CAS

BA0

A0

DM0

DQS0

DQ6

DQ4

DQ2

DQ0

9

VDD

VSSQ

VDDQ

VSSQ

VDDQ

VSS

RAS

BA1

A1

A3

VDDQ

VSSQ

VDDQ

VSSQ

VDD

-5-

Publication Release Date:Jun,17, 2011

Revision A01-003

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

www.DataSheet.co.kr

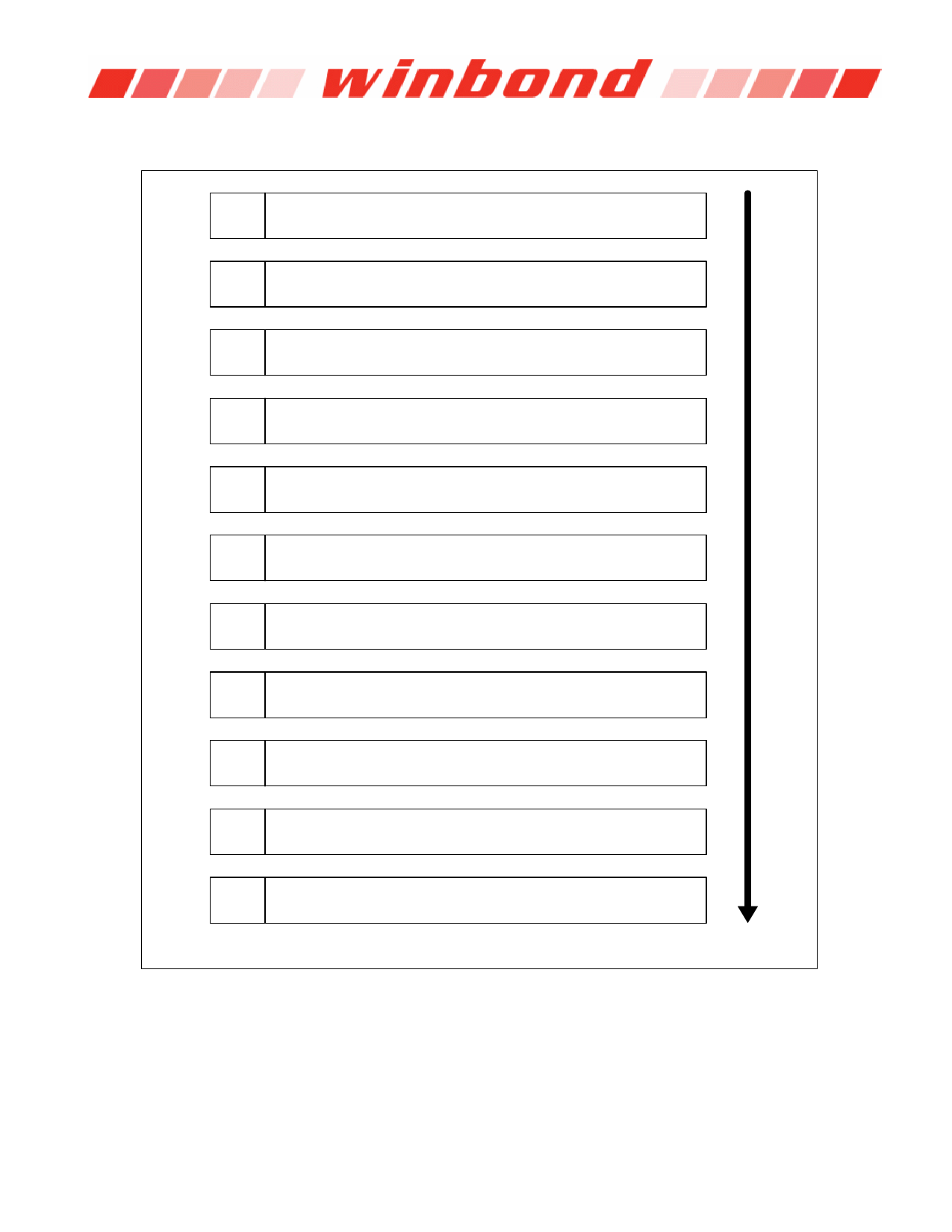

6.1.1 Initialization Flow Diagram

W947D6HB / W947D2HB

128Mb Mobile LPDDR

1 VDD and VDDQ Ramp: CKE must be held high

2 Apply stable clocks

3 Wait at least 200us with NOP or DESELECT on command bus

4 PRECHARGE ALL

5 Assert NOP or DESELCT for tRP time

Issue two AUTO REFRESH commands each followed by

6 NOP or DESELECT commands for tRFC time

7 Configure Mode Register

8 Assert NOP or DESELECT for tMRD time

9 Configure Extended Mode Register

10 Assert NOP or DESELECT for tMRD time

11 LPDDR SDRAM is ready for any valid command

- 11 -

Publication Release Date:Jun,17, 2011

Revision A01-003

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 60 Páginas | |

| PDF Descargar | [ Datasheet W947D2HB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W947D2HB | (W947D2HB / W947D6HB) 128Mb Mobile LPDDR | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |