|

|

PDF CAV24C64 Data sheet ( Hoja de datos )

| Número de pieza | CAV24C64 | |

| Descripción | 64-Kb I2C CMOS Serial EEPROM | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CAV24C64 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

CAV24C64

64-Kb I2C CMOS Serial

EEPROM

Description

The CAV24C64 is a 64−Kb CMOS Serial EEPROM device,

internally organized as 8192 words of 8 bits each.

It features a 32−byte page write buffer and supports the Standard

(100 kHz) and Fast (400 kHz) I2C protocol.

External address pins make it possible to address up to eight

CAV24C64 devices on the same bus.

Features

• Automotive Temperature Grade 1 (−40°C to +125°C)

• Supports Standard and Fast I2C Protocol

• 2.5 V to 5.5 V Supply Voltage Range

• 32−Byte Page Write Buffer

• Hardware Write Protection for Entire Memory

• CAV Prefix for Automotive and Other Applications Requiring Site

and Change Control

• Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs

(SCL and SDA)

• Low Power CMOS Technology

• 1,000,000 Program/Erase Cycles

• 100 Year Data Retention

• SOIC, TSSOP 8−lead, and WLCSP 4−Ball Packages

• This Device is Pb−Free, Halogen Free/BFR Free, and RoHS

Compliant

VCC

SCL

A2, A1, A0

WP

CAV24C64

SDA

VSS

Figure 1. Functional Symbol

www.onsemi.com

SOIC−8

W SUFFIX

CASE 751BD

WLCSP−4

C4C SUFFIX

CASE 567JY

TSSOP−8

Y SUFFIX

CASE 948AL

PIN CONFIGURATIONS (Top Views)

A0 1

A1

A2

VSS

VCC

WP

SCL

SDA

SOIC (W), TSSOP (Y)

1

VCC A1 A2 VSS

SCL B1 B2 SDA

WLCSP (C4C)

Pin Name

A0, A1, A2

SDA

SCL

WP

VCC

VSS

PIN FUNCTION

Function

Device Address Input

Serial Data Input/Output

Serial Clock Input

Write Protect Input

Power Supply

Ground

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 11 of this data sheet.

© Semiconductor Components Industries, LLC, 2016

February, 2016 − Rev. 2

1

Publication Order Number:

CAV24C64/D

1 page

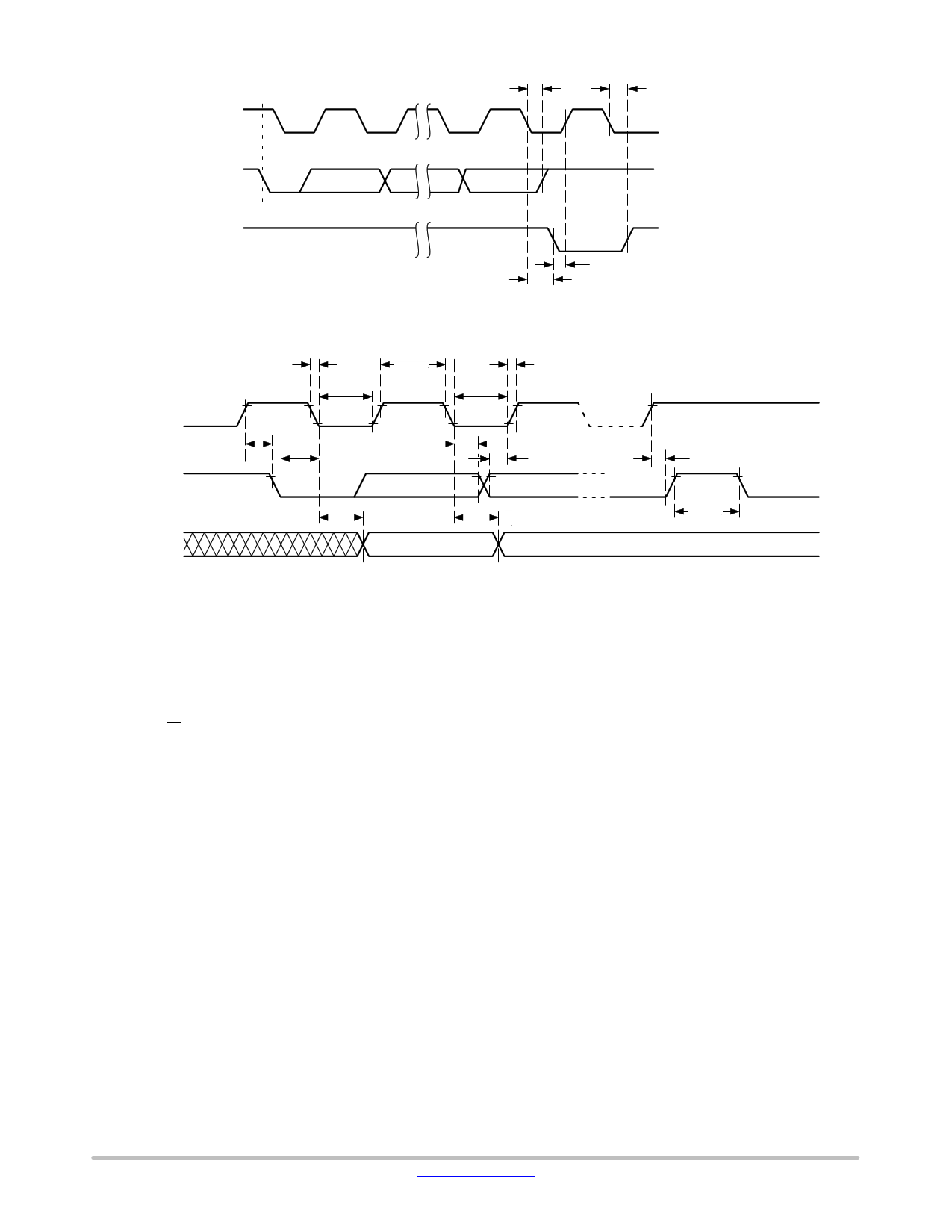

SCL FROM

MASTER

CAV24C64

BUS RELEASE DELAY (TRANSMITTER)

18

9

BUS RELEASE DELAY (RECEIVER)

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

START

ACK DELAY (≤ tAA)

Figure 4. Acknowledge Timing

ACK SETUP (≥ tSU:DAT)

SCL

tSU:STA

SDA IN

tF tHIGH

tLOW

tLOW

tHD:STA

tHD:DAT

tR

tSU:DAT

SDA OUT

tAA tDH

Figure 5. Bus Timing

tSU:STO

tBUF

WRITE OPERATIONS

Byte Write

To write data to memory, the Master creates a START

condition on the bus and then broadcasts a Slave address

with the R/W bit set to ‘0’. The Master then sends two

address bytes and a data byte and concludes the session by

creating a STOP condition on the bus. The Slave responds

with ACK after every byte sent by the Master (Figure 6). The

STOP starts the internal Write cycle, and while this

operation is in progress (tWR), the SDA output is tri-stated

and the Slave does not acknowledge the Master (Figure 7).

Page Write

The Byte Write operation can be expanded to Page Write,

by sending more than one data byte to the Slave before

issuing the STOP condition (Figure 8). Up to 32 distinct data

bytes can be loaded into the internal Page Write Buffer

starting at the address provided by the Master. The page

address is latched, and as long as the Master keeps sending

data, the internal byte address is incremented up to the end

of page, where it then wraps around (within the page). New

data can therefore replace data loaded earlier. Following the

STOP, data loaded during the Page Write session will be

written to memory in a single internal Write cycle (tWR).

Acknowledge Polling

As soon (and as long) as internal Write is in progress, the

Slave will not acknowledge the Master. This feature enables

the Master to immediately follow-up with a new Read or

Write request, rather than wait for the maximum specified

Write time (tWR) to elapse. Upon receiving a NoACK

response from the Slave, the Master simply repeats the

request until the Slave responds with ACK.

Hardware Write Protection

With the WP pin held HIGH, the entire memory is

protected against Write operations. If the WP pin is left

floating or is grounded, it has no impact on the Write

operation. The state of the WP pin is strobed on the last

falling edge of SCL immediately preceding the 1st data byte

(Figure 9). If the WP pin is HIGH during the strobe interval,

the Slave will not acknowledge the data byte and the Write

request will be rejected.

Delivery State

The CAV24C64 is shipped erased, i.e., all bytes are FFh.

www.onsemi.com

5

5 Page

CAV24C64

ORDERING INFORMATION

Device Order Number

Specific

Device Marking

Package Type

Lead Finish

Shipping†

CAV24C64YE−GT3

C64F

TSSOP−8

NiPdAu

Tape & Reel,

3,000 Units / Reel

CAV24C64YE−G (Note 9)

C64F

TSSOP−8

NiPdAu

Tube, 100 Units / Tube

CAV24C64WE−GT3

24C64F

SOIC−8, JEDEC

NiPdAu

Tape & Reel,

3,000 Units / Reel

CAV24C64C4CTR (Note 9)

A

WLCSP4

SnAgCu

Tape & Reel,

5,000 Units / Reel

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging

Specifications Brochure, BRD8011/D.

9. Please contact your nearest ON Semiconductor Sales office for availability.

ON Semiconductor is licensed by Philips Corporation to carry the I2C Bus Protocol.

ON Semiconductor and the

are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed

at www.onsemi.com/site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation

or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets

and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each

customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended,

or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which

the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or

unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and

expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim

alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable

copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada

Email: [email protected]

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81−3−5817−1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

www.onsemi.com

11

CAV24C64/D

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet CAV24C64.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CAV24C64 | 64-Kb I2C CMOS Serial EEPROM | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |