|

|

PDF AA104SH02-T1 Data sheet ( Hoja de datos )

| Número de pieza | AA104SH02-T1 | |

| Descripción | SVGA LCD Module | |

| Fabricantes | Mitsubishi | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AA104SH02-T1 (archivo pdf) en la parte inferior de esta página. Total 29 Páginas | ||

|

No Preview Available !

Preliminary

TENTATIVE

All information in this technical data sheet is tentative

and subject to change without notice.

10.4” SVGA

TECHNICAL SPECIFICATION

AA104SH02--T1

MITSUBISHI ELECTRIC Corp.

MITSUBISHI Confidential

(1/29)

Date: Aug.4,’09

AA104SH02--T1_02_00

Free Datasheet http://www.datasheet4u.com/

1 page

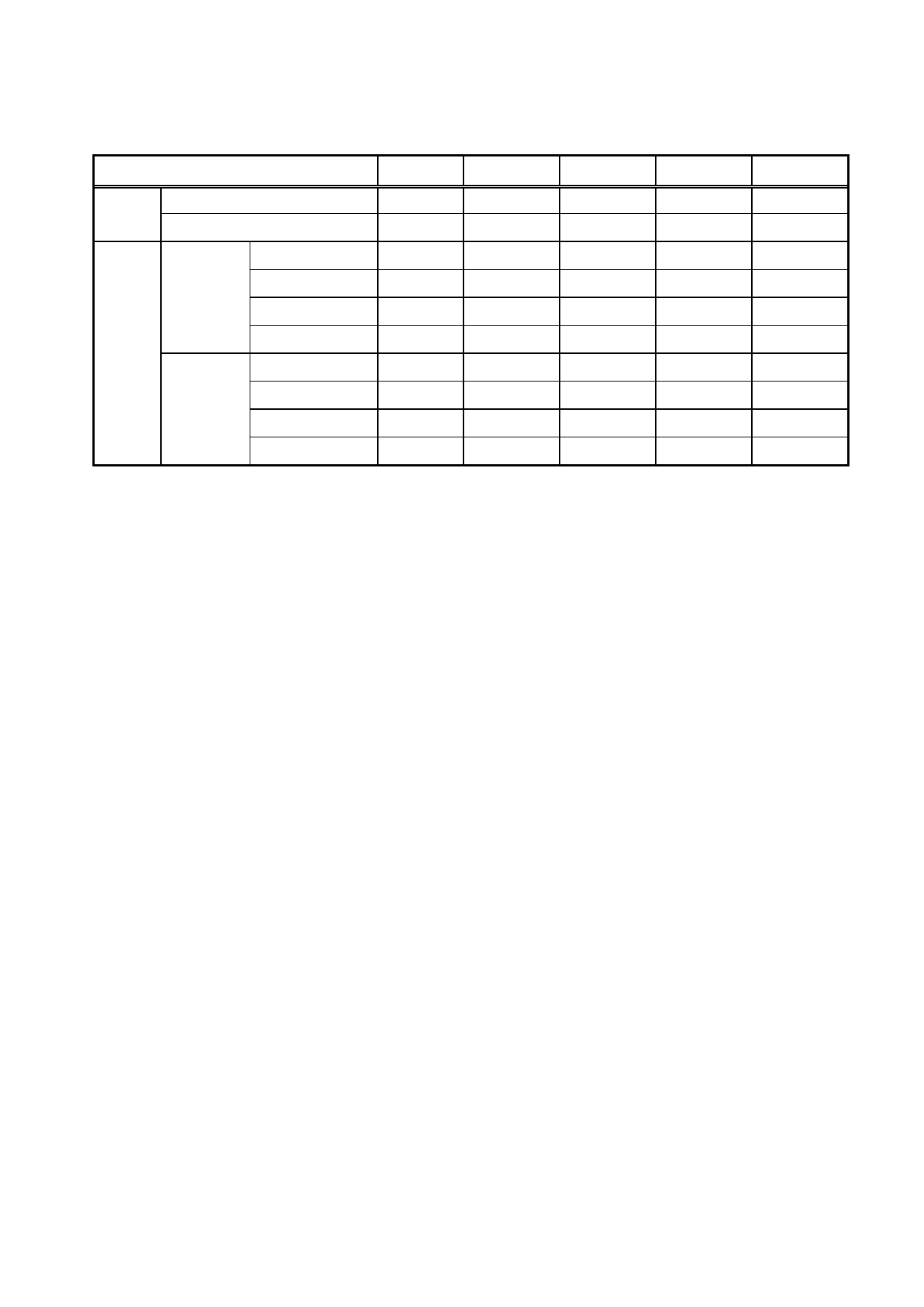

3. ABSOLUTE MAXIMUM RATINGS

ITEM

SYMBOL

MIN.

MAX

UNIT

Power Supply Voltage for LCD

VCC

0 4.0 V

Logic Input Voltage

VI

−0.3 VCC+0.3

V

Backlight (LED) Current

IF 0 180 mA

Touch Panel Voltage

TPV

-- 7.0 V

Operation Temperature (Touch Panel) Note 1,2) Top(TouchPanel)

−20

70

°C

Operation Temperature (Ambient) Note 2)

Top(Ambient)

−20

70

°C

Storage Temperature Note 2)

Tstg −30 80 °C

[Note]

1) Measured at the center of active area and at the center of panel back surface

2) Top,Tstg ≤ 40°C : 90%RH max. without condensation

Top,Tstg > 40°C : Absolute humidity shall be less than the value of 90%RH at 40°C without

condensation.

4. ELECTRICAL CHARACTERISTICS

(1) TFT-LCD

ITEM

SYMBOL MIN.

Ambient temperature: Ta = 25

TYP. MAX. UNIT Remarks

Power Supply Voltages for LCD

Power Supply Currents for LCD

Permissive Input Ripple Voltage

Logic Input Voltage

High

Low

VCC

ICC

VRP

VIH

VIL

3.0 3.3 3.6 V

*1)

--

TBD

TBD mA

*2)

-- -- 100 mVp-p VCC = +3.3 V

2.4

--

VCC

V MODE, SC

0 -- 0.8 V MODE, SC

*1) Power and signals sequence:

t1 ≤ 10ms

0 < t2 ≤ 50ms

0 < t3 ≤ 50ms

200ms ≤ t4

200ms ≤ t5

0 ≤ t6

LCD Power Supply

Logic Signal

0.9VCC

0.1VCC

VCC

data

0.9VCC

0.1VCC 0.1VCC

t1 t2

t3 t4

Backlight Power Supply

t5 t6

data: RGB DATA, DCLK, DENA, MODE, SC

MITSUBISHI Confidential

(5/29)

AA104SH02--T1_02_00

Free Datasheet http://www.datasheet4u.com/

5 Page

6. INTERFACE TIMING

LVDS transmitter input signal

(1) Timing Specifications

ITEM

SYMBOL MIN.

TYP.

MAX.

UNIT

Frequency

DCLK Period

fCLK

35

40

42 MHz

tCLK

23.8

25

28.6

ns

Active Time tHA 800 800 800 tCLK

Horizontal Blanking Time

Frequency

tHB

fH

20

35.2

256

37.9

--

39.2

tCLK

kHz

DENA

Period

tH 25.5 26.4 28.4

Active Time tVA 600 600 600

μs

tH

Vertical Blanking Time

Frequency

tVB

fV

3

55

28 -- tH

60 64.2 Hz

Period

tV 15.6 16.7 18.2 ms

[Note]

1) DENA (Data Enable) should always be positive polarity as shown in the timing specification.

2) DCLK should appear during all invalid period.

3) LVDS timing follows the timing specifications of LVDS receiver IC: THC63LVDF84B(Thine).

4) In case of blanking time fluctuation, please use following.

tVBn > tVBn-1 − 3(tH)

MITSUBISHI Confidential

(11/29)

AA104SH02--T1_02_00

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 29 Páginas | |

| PDF Descargar | [ Datasheet AA104SH02-T1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AA104SH02-T1 | SVGA LCD Module | Mitsubishi |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |