|

|

PDF HEF4043B Data sheet ( Hoja de datos )

| Número de pieza | HEF4043B | |

| Descripción | Quadruple R/S latch with 3-state outputs | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HEF4043B (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

HEF4043B

Quad R/S latch with 3-state outputs

Rev. 10 — 18 November 2011

Product data sheet

1. General description

The HEF4043B is a quad R/S latch with 3-state outputs with a common output enable

input (OE). Each latch has an active HIGH set input (1S to 4S), an active HIGH reset input

(1R to 4R) and an active HIGH 3-state output (1Q to 4Q).

When OE is HIGH, the latch output (nQ) is determined by the nR and nS inputs as shown

in Table 3. When OE is LOW, the latch outputs are in the high impedance OFF-state. OE

does not affect the state of the latch. The high impedance off-state feature allows common

bussing of the outputs.

It operates over a recommended VDD power supply range of 3 V to 15 V referenced to VSS

(usually ground). Unused inputs must be connected to VDD, VSS, or another input.

2. Features and benefits

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

Specified from 40 C to +85 C

Complies with JEDEC standard JESD 13-B

3. Applications

Four-bit storage with output enable

4. Ordering information

Table 1. Ordering information

All types operate from 40 C to +85 C.

Type number

Package

Name

Description

HEF4043BP

DIP16

plastic dual in-line package; 16 leads (300 mil)

HEF4043BT

SO16

plastic small outline package; 16 leads; body width 3.9 mm

Version

SOT38-4

SOT109-1

1 page

NXP Semiconductors

HEF4043B

Quad R/S latch with 3-state outputs

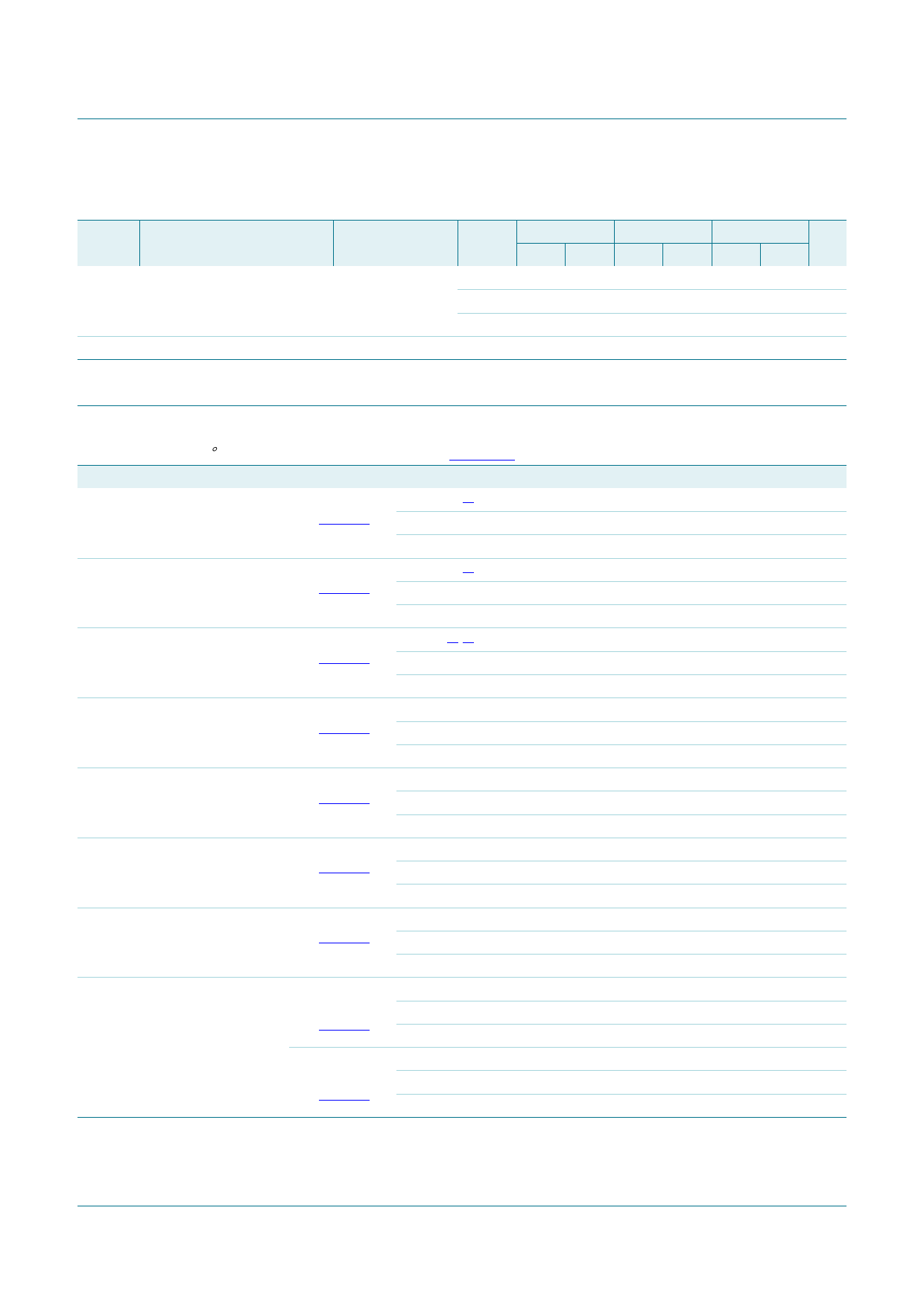

Table 6. Static characteristics …continued

VSS = 0 V; VI = VSS or VDD unless otherwise specified.

Symbol Parameter

Conditions

IDD supply current

IO = 0 A

CI input capacitance

11. Dynamic characteristics

VDD

5V

10 V

15 V

Tamb = 40 C Tamb = 25 C

Min Max Min Max

- 20 - 20

- 40 - 40

- 80 - 80

- - - 7.5

Tamb = 85 C Unit

Min Max

- 150 A

- 300 A

- 600 A

- - pF

Table 7. Dynamic characteristics

VSS = 0 V; Tamb = 25 C; For waveforms and test circuit see Section 12; unless otherwise specified.

Symbol Parameter

Conditions

VDD

Extrapolation formula Min

tPHL HIGH to LOW

nR nQ;

5 V [1] 63 ns + (0.55 ns/pF)CL -

propagation delay see Figure 4 10 V

24 ns + (0.23 ns/pF)CL -

15 V

17 ns + (0.16 ns/pF)CL -

tPLH LOW to HIGH

nS nQ;

5 V [1] 38 ns + (0.55 ns/pF)CL -

propagation delay see Figure 4 10 V

14 ns + (0.23 ns/pF)CL -

15 V

7 ns + (0.16 ns/pF)CL -

tt

transition time

nQ output;

5 V [1] [2] 10 ns + (1.00 ns/pF)CL -

see Figure 4 10 V

9 ns + (0.42 ns/pF)CL -

15 V

6 ns + (0.28 ns/pF)CL -

tPHZ HIGH to OFF-state OE nQ;

5V

propagation delay see Figure 5 10 V

-

-

Typ

90

35

25

65

25

15

60

30

20

45

20

15 V

- 10

tPLZ LOW to OFF-state OE nQ;

5V

propagation delay see Figure 5 10 V

- 50

- 20

15 V

- 10

tPZH OFF-state to HIGH OE nQ;

5V

propagation delay see Figure 5 10 V

- 25

- 15

15 V

- 10

tPZL OFF-state to LOW OE nQ;

5V

propagation delay see Figure 5 10 V

- 40

- 20

15 V

- 15

tW pulse width

nS input HIGH; 5 V

minimum width; 10 V

see Figure 4

15 V

30 15

20 10

16 8

nR input HIGH; 5 V

minimum width; 10 V

see Figure 4

15 V

30 15

20 10

16 8

Max Unit

180 ns

70 ns

50 ns

135 ns

50 ns

35 ns

120 ns

60 ns

40 ns

90 ns

35 ns

25 ns

100 ns

40 ns

25 ns

50 ns

30 ns

25 ns

80 ns

45 ns

35 ns

- ns

- ns

- ns

- ns

- ns

- ns

[1] The typical values of the propagation delay and transition times are calculated from the extrapolation formulas shown (CL in pF).

[2] tt is the same as tTHL and tTLH.

HEF4043B

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 10 — 18 November 2011

© NXP B.V. 2011. All rights reserved.

5 of 14

5 Page

NXP Semiconductors

HEF4043B

Quad R/S latch with 3-state outputs

14. Revision history

Table 11. Revision history

Document ID

Release date Data sheet status

Change notice

HEF4043B v.10

Modifications:

HEF4043B v.9

20111118

Product data sheet

-

• Table 6: IOH minimum values changed to maximum

20091216

Product data sheet

-

HEF4043B v.8

20091127

Product data sheet

-

HEF4043B v.7

20090710

Product data sheet

-

HEF4043B v.6

20081111

Product data sheet

-

HEF4043B v.5

20080729

Product data sheet

-

HEF4043B v.4

20080710

Product data sheet

-

HEF4043B_CNV v.3

19950101

Product specification

-

HEF4043B_CNV v.2

19950101

Product specification

-

Supersedes

HEF4043B v.9

HEF4043B v.8

HEF4043B v.7

HEF4043B v.6

HEF4043B v.5

HEF4043B v.4

HEF4043B_CNV v.3

HEF4043B_CNV v.2

-

HEF4043B

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 10 — 18 November 2011

© NXP B.V. 2011. All rights reserved.

11 of 14

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet HEF4043B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HEF4043B | Quadruple R/S latch with 3-state outputs | NXP Semiconductors |

| HEF4043B | Quadruple R/S latch | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |