|

|

PDF NT5CC512M8BN Data sheet ( Hoja de datos )

| Número de pieza | NT5CC512M8BN | |

| Descripción | 4Gb DDR3 SDRAM B-Die | |

| Fabricantes | Nanya | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NT5CC512M8BN (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

4Gb DDR3 SDRAM B-Die

NT5CB1024M4BN / NT5CB512M8BN / NT5CB256M16BP

NT5CC1024M4BN / NT5CC512M8BN / NT5CC256M16BP

Feature

VDD = VDDQ = 1.5V ± 0.075V (JEDEC Standard

Power Supply)

VDD = VDDQ = 1.35V -0.0675V/+0.1V

(Backward Compatible to VDD = VDDQ = 1.5V

±0.075V)

8 Internal memory banks (BA0- BA2)

Differential clock input (CK, )

Programmable Latency: 5, 6, 7, 8, 9, 10, 11

WRITE Latency (CWL): 5,6,7,8,9

POSTED CAS ADDITIVE Programmable Additive

Latency (AL): 0, CL-1, CL-2 clock

Programmable Sequential / Interleave Burst Type

Programmable Burst Length: 4, 8

Through ZQ pin (RZQ:240 ohm±1%)

8n-bit prefetch architecture

Output Driver Impedance Control

Differential bidirectional data strobe

Internal(self) calibration:Internal self calibration

OCD Calibration

Dynamic ODT (Rtt_Nom & Rtt_WR)

Auto Self-Refresh

Self-Refresh Temperature

RoHS compliance and Halogen free

Packages:

78-Balls BGA for x4/x8 components

96-Ball BGA for x16 components

REV 1.0

01/ 2012

1

Free Datasheet http://www.0PDF.com

1 page

4Gb DDR3 SDRAM B-Die

NT5CB1024M4BN / NT5CB512M8BN / NT5CB256M16BP

NT5CC1024M4BN / NT5CC512M8BN / NT5CC256M16BP

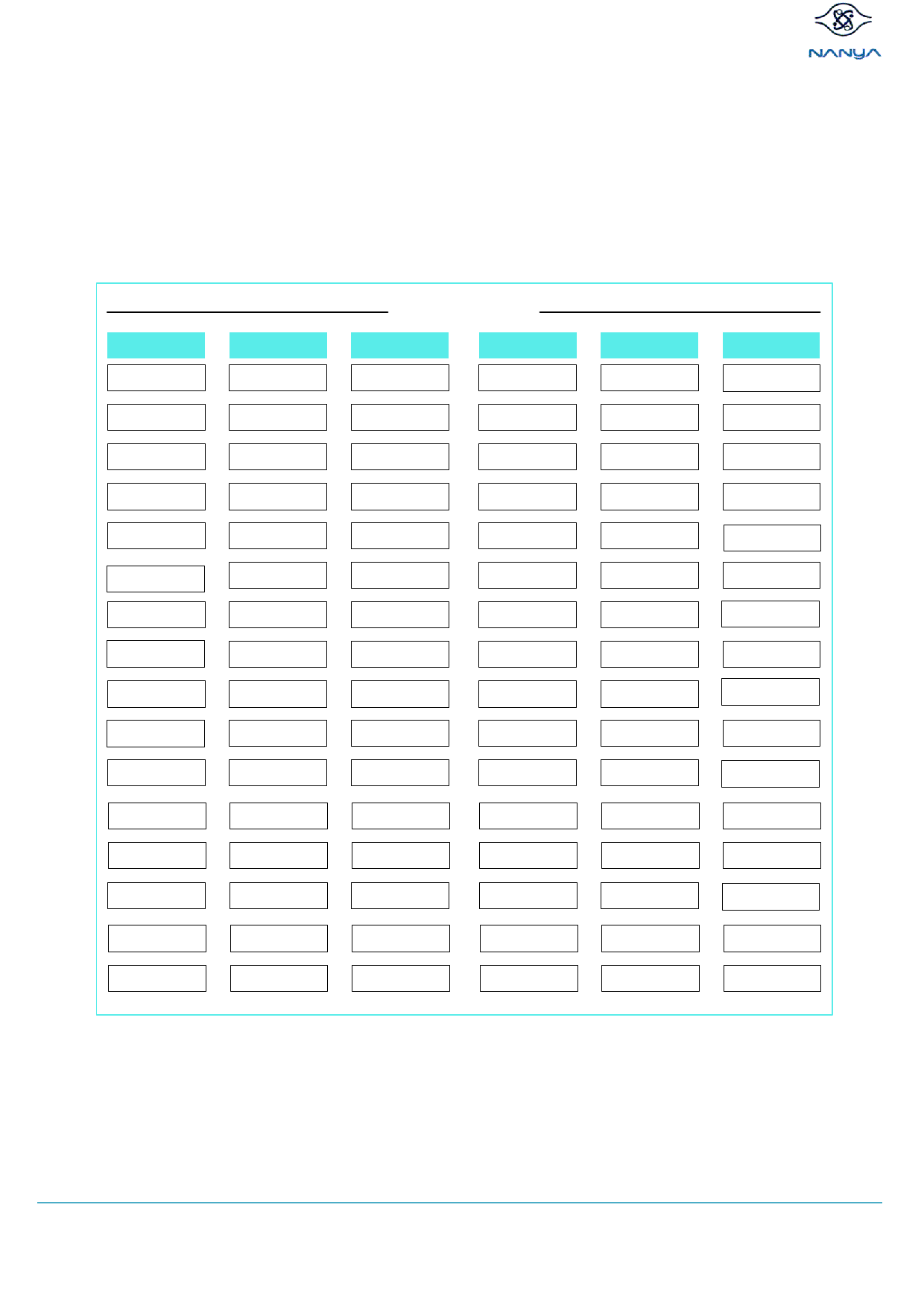

Pin Configuration – 96 balls BGA Package (x16)

< TOP View>

See the balls through the package

1

VDDQ

VSSQ

VDDQ

VSSQ

VSS

VDDQ

VSSQ

VREFDQ

NC

ODT

NC

VSS

VDD

VSS

VDD

VSS

2

DQU5

VDD

DQU3

VDDQ

VSSQ

DQL2

DQL6

VDDQ

VSS

VDD

BA0

A3

A5

A7

3

DQU7

VSS

DQU1

UDM

DQL0

DQSL

DQL4

BA2

A0

A2

A9

A13

x 16

7

A DQU4

B

C DQSU

D DQU0

E DML

F DQL1

G VDD

H DQL7

J CK

K

L A10/AP

M A15

N A12/BC#

P A1

R A11

T A14

8

VDDQ

DQU6

DQU2

VSSQ

VSSQ

DQL3

VSS

DQL5

VSS

VDD

ZQ

VREFCA

BA1

A4

A6

A8

9

VSS

VSSQ

VDDQ

VDD

VDDQ

VSSQ

VSSQ

VDDQ

NC

CKE

NC

VSS

VDD

VSS

VDD

VSS

REV 1.0

01/ 2012

5

Free Datasheet http://www.0PDF.com

5 Page

4Gb DDR3 SDRAM B-Die

NT5CB1024M4BN / NT5CB512M8BN / NT5CB256M16BP

NT5CC1024M4BN / NT5CC512M8BN / NT5CC256M16BP

Basic Functionality

The DDR3(L) SDRAM B-Die is a high-speed dynamic random access memory internally configured as an eight-bank

DRAM. The DDR3(L) SDRAM uses an 8n prefetch architecture to achieve high speed operation. The 8n prefetch

architecture is combined with an interface designed to transfer two data words per clock cycle at the I/O pins. A single

read or write operation for the DDR3(L) SDRAM consists of a single 8n-bit wide, four clock data transfer at the internal

DRAM core and two corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write operation to the DDR3(L) SDRAM are burst oriented, start at a selected location, and continue for a burst

length of eight or a ‘chopped’ burst of four in a programmed sequence. Operation begins with the registration of an Active

command, which is then followed by a Read or Write command. The address bits registered coincident with the Active

command are used to select the bank and row to be activated (BA0-BA2 select the bank; A0-A15 select the row). The

address bit registered coincident with the Read or Write command are used to select the starting column location for the

burst operation, determine if the auto precharge command is to be issued (via A10), and select BC4 or BL8 mode ‘on the

fly’ (via A12) if enabled in the mode register.

Prior to normal operation, the DDR3(L) SDRAM must be powered up and initialized in a predefined manner. The following

sections provide detailed information covering device reset and initialization, register definition, command descriptions

and device operation.

RESET and Initialization Procedure

Power-up Initialization sequence

The Following sequence is required for POWER UP and Initialization

1. Apply power ( is recommended to be maintained below 0.2 x VDD, all other inputs may be undefined).

needs to be maintained for minimum 200μs with stable power. CKE is pulled “Low” anytime before being

de-asserted (min. time 10ns). The power voltage ramp time between 300mV to VDDmin must be no greater than 200ms;

and during the ramp, VDD>VDDQ and (VDD-VDDQ) <0.3 Volts.

- VDD and VDDQ are driven from a single power converter output, AND

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one

side and must be larger than or equal to VSSQ and VSS on the other side. In addition, VTT is limited to 0.95V max once

power ramp is finished, AND

- Vref tracks VDDQ/2.

OR

- Apply VDD without any slope reversal before or at the same time as VDDQ.

- Apply VDDQ without any slope reversal before or at the same time as VTT & Vref.

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one

side and must be larger than or equal to VSSQ and VSS on the other side.

2. After is de-asserted, wait for another 500us until CKE become active. During this time, the DRAM will start

internal state initialization; this will be done independently of external clocks.

3. Clock (CK, ) need to be started and stabilized for at least 10ns or 5tCK (which is larger) before CKE goes active.

Since CKE is a synchronous signal, the corresponding set up time to clock (tIS) must be meeting. Also a NOP or

Deselect command must be registered (with tIS set up time to clock) before CKE goes active. Once the CKE registered

“High” after Reset, CKE needs to be continuously registered “High” until the initialization sequence is finished,

including expiration of tDLLK and tZQinit.

REV 1.0

01/ 2012

11

Free Datasheet http://www.0PDF.com

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet NT5CC512M8BN.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NT5CC512M8BN | 4Gb DDR3 SDRAM B-Die | Nanya |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |