|

|

PDF NAU8402 Data sheet ( Hoja de datos )

| Número de pieza | NAU8402 | |

| Descripción | Stereo 24-Bit DAC | |

| Fabricantes | Nuvoton Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NAU8402 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

NAU8402

1. GENERAL DESCRIPTION

Stereo 24-bit DAC with 2Vrms Line Out

emPowerAudio™

The NAU8402 is a high quality 24-bit stereo DAC with 2Vrms analog output capability. This device includes an

integrated charge pump enabling true ground referenced outputs and full 5.6Vpp output levels, while operating from

only a single 3.3V supply voltage. Additionally, the NAU8402 includes automatic pop/click elimination features and

high immunity to power supply and other system noise. This enables fast and efficient system integration while

minimizing external component costs. The NAU8402 is specified for operation from -40°C to +85°C. AEC-Q100 &

TS16949 compliant device is available upon request .

2. FEATURES

Stereo 24-bit DAC

Full 2Vrms output using only 3.3Vdc supply

True Ground Referenced analog outputs

Audio Performance

o 98dB SNR A-weighted performance

o -82dB THD+N

o 68dB PSRR at 1kHz

o 108dB channel separation at 1kHz

Up to 96 kHz audio sample rate

Automatic pop/click elimination and output muting

for power-on and no-signal conditions

Interfaces

I2S slave supporting up to 96 kHz sample rate

determined by clock frequency ratios.

Supports either 12.288MHz or 24.576MHz

master clock frequency w/auto rate detection for

sampling rate 24k, 48k and 96k Hz

Supports either 11.290MHz or 22.579MHz for

sampling rate 44.1kHz

Low Power, Low Voltage

Nominal Operating Voltage: 3.3V

Additional features

Low external parts count

High system noise immunity

Package: 16-pin TSSOP (Green/ROHS)

Operating voltage: 3.3-3.6V

Operating temperature range: -40° to +85°C

Applications

Game Consoles

DVD players

Set top boxes

Digital TVs

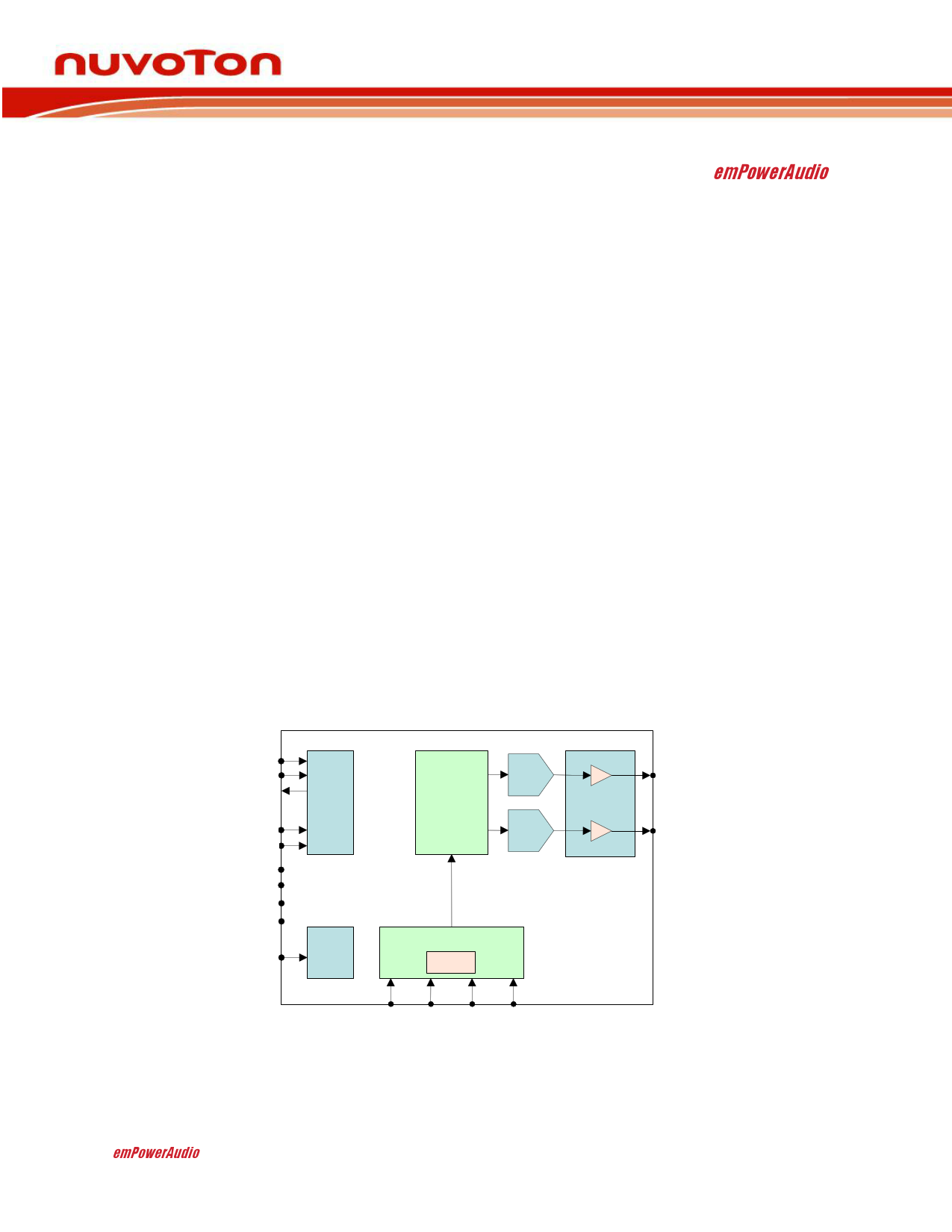

CPCA

CPCB

CPOUT

LINEVDD

LINEGND

VDDA

VREF

VSSA

VDDB

/MUTEb

Charge

Pump

Control

Interface

DAC

Digital Filters

LDAC

Line Drivers

LLINEOUT

RDAC

RLINEOUT

Digital Audio Interface

I2S

MCLK BCLK FS DACIN

emPowerAudio™

Datasheet Revision 1.62

Page 1 of 22

March 28, 2013

1 page

NAU8402

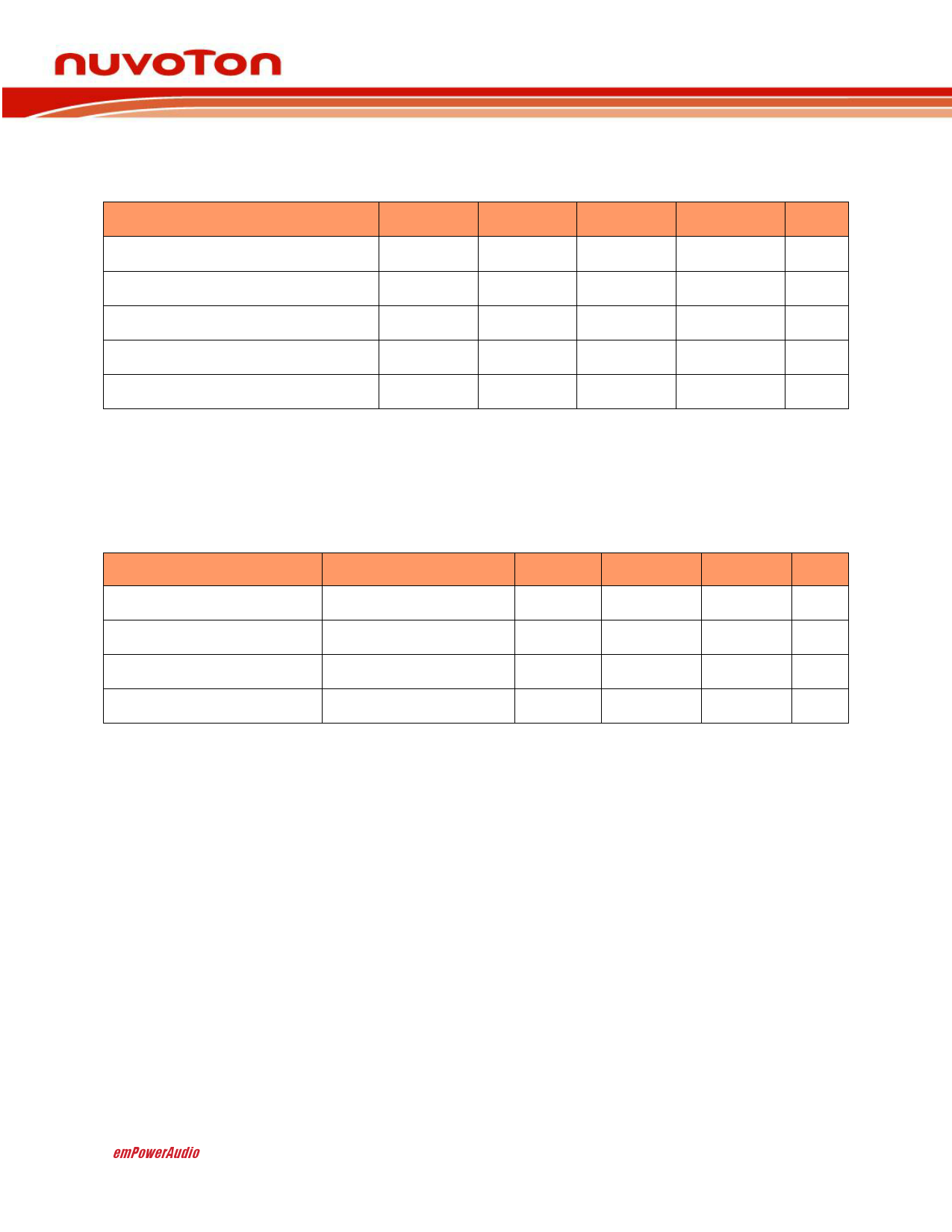

8. ABSOLUTE MAXIMUM RATINGS

DESCRIPTION

VDDB, LineVDD , VDDA supply voltages

Digital Input Voltage range

Analog Input Voltage

Temperature range

Storage Temperature

SYMBOL

VDD

DVIN

AVIN

TA

Tst

CONDITION

MIN

VDDVSS

DVIN VSS

AVIN VSSA

-0.3

VSS – 0.3

VSSA – 0.3

-40

-65

MAX

4.5

VDDB + 0.30

VDDA + 0.30

+150

+150

Units

V

V

V

C

C

CAUTION: Do not operate at or near the maximum ratings listed for extended period of time. Exposure to such

conditions may adversely influence product reliability and result in failures not covered by warranty. These devices

are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

9. OPERATING CONDITIONS

Condition

Supply voltages

Supply voltage

Ground

Operating Temperature

Symbol

LineVDD, VDDA

VDDB

LINEGND, VSSA

TA

Min Value

3.0

1.7

-40

Typical

Value

3.3

3.3

0

Max Value Units

3.6 V

3.6 V

V

+85 C

emPowerAudio™

Datasheet Revision 1.62

Page 5 of 22

March 28, 2013

5 Page

NAU8402

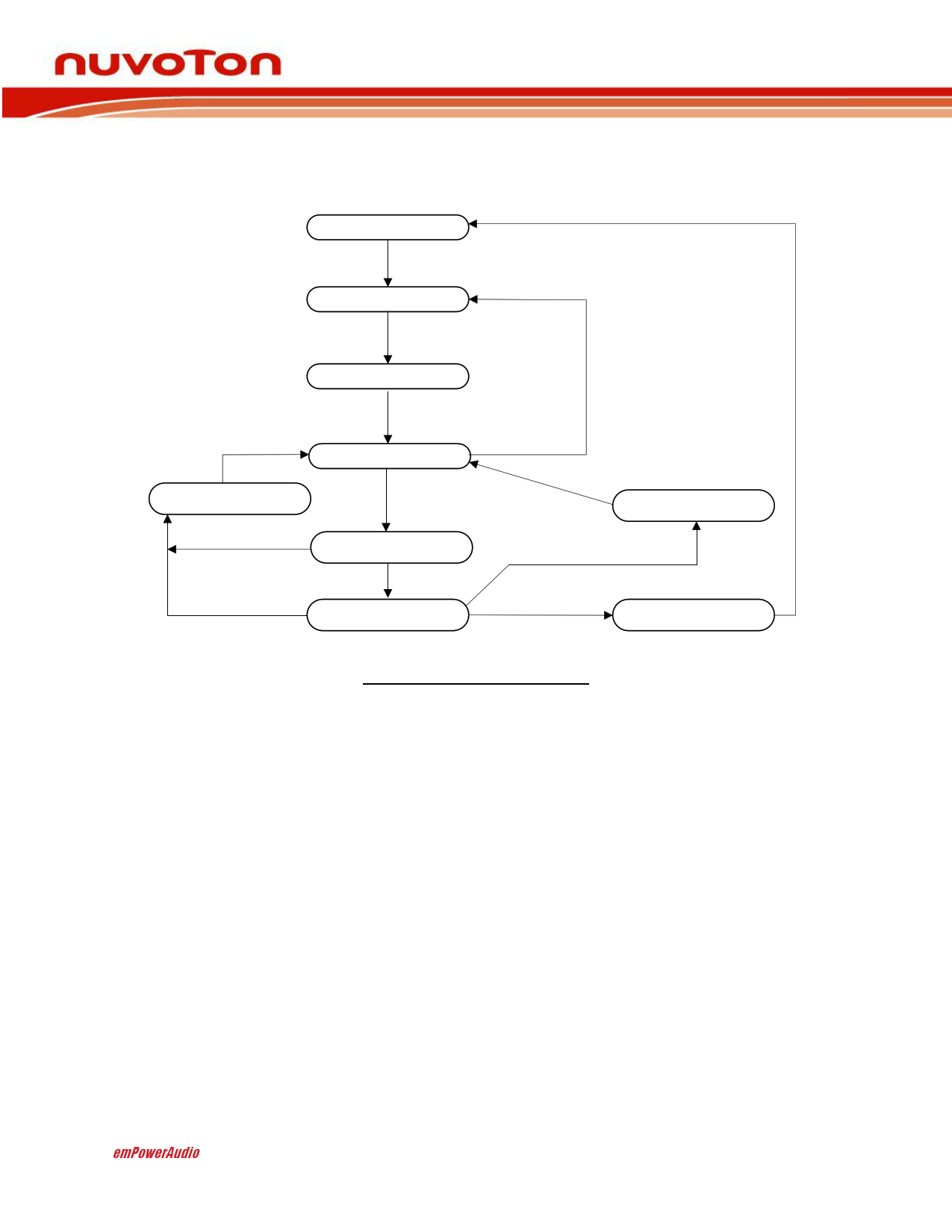

12.5MUTE / UN-MUTE SEQUENCE AND OPERATING MODES

All VDD’s 0V

Apply power

Reset state

Start MCLK

Init

Remove power

Stop MCLK

Mute complete

Mute process

Invalid MCLK/FS Ratio |

BCLK absent & /MUTE=1

Start FS & BCLK

Mute State

Mute complete

Valid MCLK/FS Ratio &

/MUTE=1 & BCLK present

Instant Mute Process

Unmute process

Valid MCLK/FS Ratio &

/MUTE=0 & BCLK present

Unmute complete

Normal mode:

Outputs enabled

MCLK=0 & FS=0 &

/MUTE=0 & BCLK=0

Instant Mute State

Figure 5: Mute / Un-mute Sequence

The NAU8402 power-up sequence is as follows:

Apply power

Start MCLK, FS & BCLK

The device initializes in the mute state upon application of clocks. The device begins the un-mute process once

all three un-mute conditions are met:

o Valid MCLK/FS ratio of 256±3 or 512±3 MCLK cycles per FS has been detected.

o BCLK is present.

o /MUTE is high.

In the un-mute process, the line driver performs a soft un-mute. This will take 341ms for the initial un-mute after

power up (see Table 3) and 2000 samples (42 ms for 48kHz FS) for any consecutive un-mute with the clocks

running. Once the line driver has been un-muted, the digital volume ramps up from full digital mute to -127.5dB

and then to full scale in 256 samples.

.

After the un-mute process completes, the device enters normal mode with analog outputs enabled and remains

there until any of the un-mute conditions are no longer true.

emPowerAudio™

Datasheet Revision 1.62

Page 11 of 22

March 28, 2013

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet NAU8402.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NAU8401 | 24-bit Stereo Audio DAC | Nuvoton Technology |

| NAU8402 | Stereo 24-Bit DAC | Nuvoton Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |