|

|

PDF HDSP-390X Data sheet ( Hoja de datos )

| Número de pieza | HDSP-390X | |

| Descripción | 20 mm (0.8 inch) Seven Segment Displays | |

| Fabricantes | Agilent(Hewlett-Packard) | |

| Logotipo | .gif) |

|

Hay una vista previa y un enlace de descarga de HDSP-390X (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Low Cost Gigabit Rate

Transmit/Receive Chip Set

Technical Data

HDMP-1012 Transmitter

HDMP-1014 Receiver

Features

• Transparent, Extended

Ribbon Cable Replacement

• Implemented in a Low Cost

Aluminum M-Quad 80

Package

• High-Speed Serial Rate 150-

1500 MBaud

• Standard 100K ECL

Interface

16, 17, 20, or 21 Bits Wide

• Reliable Monolithic Silicon

Bipolar Implementation

• On-chip Phase-Locked Loops

- Transmit Clock Generation

- Receive Clock Extraction

Applications

• Backplane/Bus Extender

• Video, Image Acquisition

• Point to Point Data Links

• Implement SCI-FI Standard

• Implement Serial HIPPI

Specification

Description

The HDMP-1012 transmitter and

the HDMP-1014 receiver are used

to build a high speed data link for

point to point communication.

The monolithic silicon bipolar

transmitter chip and receiver chip

are each provided in a standard

aluminum M-Quad 80 package.

From the user’s viewpoint, these

products can be thought of as

providing a “virtual ribbon cable”

interface for the transmission of

data. Parallel data loaded into the

Tx (transmitter) chip is delivered

to the Rx (receiver) chip over a

serial channel, which can be

either a coaxial copper cable or

optical link.

The chip set hides from the user

all the complexity of encoding,

multiplexing, clock extraction,

demultiplexing and decoding.

Unlike other links, the phase-

locked-loop clock extraction

circuit also transparently provides

for frame synchronization - the

user is not troubled with the

periodic insertion of frame

synchronization words. In

addition, the dc balance of the

line code is automatically

maintained by the chip set. Thus,

the user can transmit arbitrary

data without restriction. The Rx

chip also includes a state-machine

controller (SMC) that provides a

startup handshake protocol for

the duplex link configuration.

The serial data rate of the T/R link

is selectable in four ranges (see

tables on page 5), and extends

from 120 Mbits/s up to 1.25

Gbits/s. The parallel data interface

is 16 or 20 bit single-ended ECL,

pin selectable. A flag bit is

available and can be used as an

extra 17th or 21st bit under the

user’s control. The flag bit can

also be used as an even or odd

frame indicator for dual-frame

transmission. If not used, the link

performs expanded error

detection.

The serial link is synchronous,

and both frame synchronization

5962-0049E (6/94)

573

1 page

HDMP-1012 (Tx), HDMP-1014 (Rx)

Typical Operating Rates For 16 Bit Mode[1]

Tc = 0°C to +85°C, VEE = -4.5 V to -5.5 V

DIV1

0

0

1

1

DIV0

0

1

0

1

Parallel Word Rate

(Mword/sec)

Range

42 75.0 (max)

21 51

11 25

7.5 (min)

13

Serial Data Rate

(Mbit/sec)

Range

672 1200.0 (max)

336 808

168 404

120.0 (min)

202

Serial Baud Rate

(MBaud)

Range

840 1500.0 (max)

420 1010

210 505

150.0 (min)

253

Notes:

1. Extended operating rates to 1800 MBaud/sec (typ) are possible for Tc = 0°C to +60°C.

2. All values are typical over temperature and process, unless otherwise noted by (min) or (max).

3. Typical Serial Baud Rates for DIV1/DIV0 = 0/0 are up to 1800 MBd.

4. All values in this table are expected for a BER less than 10-14. This estimation is based on the maximum data rate characterization,

which was performed at a serial data rate of 2000 Mbits/s for a BER less than 10-11. Production units are 100% screened for less than

BER = 10-7.

5

0/0

25

,,,,0/1 420

1/0 210

505

,,,,1/1 110

253

,,100 500

FRAME RATE (Mwords/sec)

50 75

840

1010

100

1800

125

1000

BAUD RATE = 20 x FRAME RATE

1500

2000

2500

SERIAL DATA RATE (Mbaud)

Figure 2: Typical 16-bit Mode Data Rates.

HDMP-1012 (Tx), HDMP-1014 (Rx)

Typical Operating Rates For 20 Bit Mode[1]

Tc = 0°C to +85°C, VEE = -4.5 V to -5.5 V

DIV1

0

0

1

1

DIV0

0

1

0

1

Parallel Word Rate

(Mword/sec)

Range

35 62.5 (max)

18 42

9 21

6.3 (min)

10.5

Serial Data Rate

(Mbit/sec)

Range

700 1250.0 (max)

350 842

175 421

125.0 (min)

211

Serial Baud Rate

(MBaud/Sec)

Range

840 1500 (max)

420 1010

210 505

150 (min)

253

Notes:

1. Extended operating rates to 1800 MBaud/sec are possible for Tc = 0°C to +60°C.

2. All values are typical over temperature and process, unless otherwise noted by (min) or (max).

3. Typical Serial Baud Rates for DIV1/DIV0 = 0/0 are up to 1800 MBd.

4. All values in this table are expected for a BER less than 10-14. This estimation is based on the maximum data rate characterization,

which was performed at a serial data rate of 2000 Mbits/s for a BER less than 10-11. Production units are 100% screened for less than

BER = 10-7.

4

0/0

FRAME RATE (Mwords/sec)

25 50

840

75

1800

100

,,,,,0/1 420

1/0 210

505

,,,,1/1 110 253

,,100 500

1010

1000

BAUD RATE = 24 x FRAME RATE

1500

2000

2500

Figure 3. Typical 20-Bit Mode Data Rates.

SERIAL DATA RATE (Mbaud)

577

5 Page

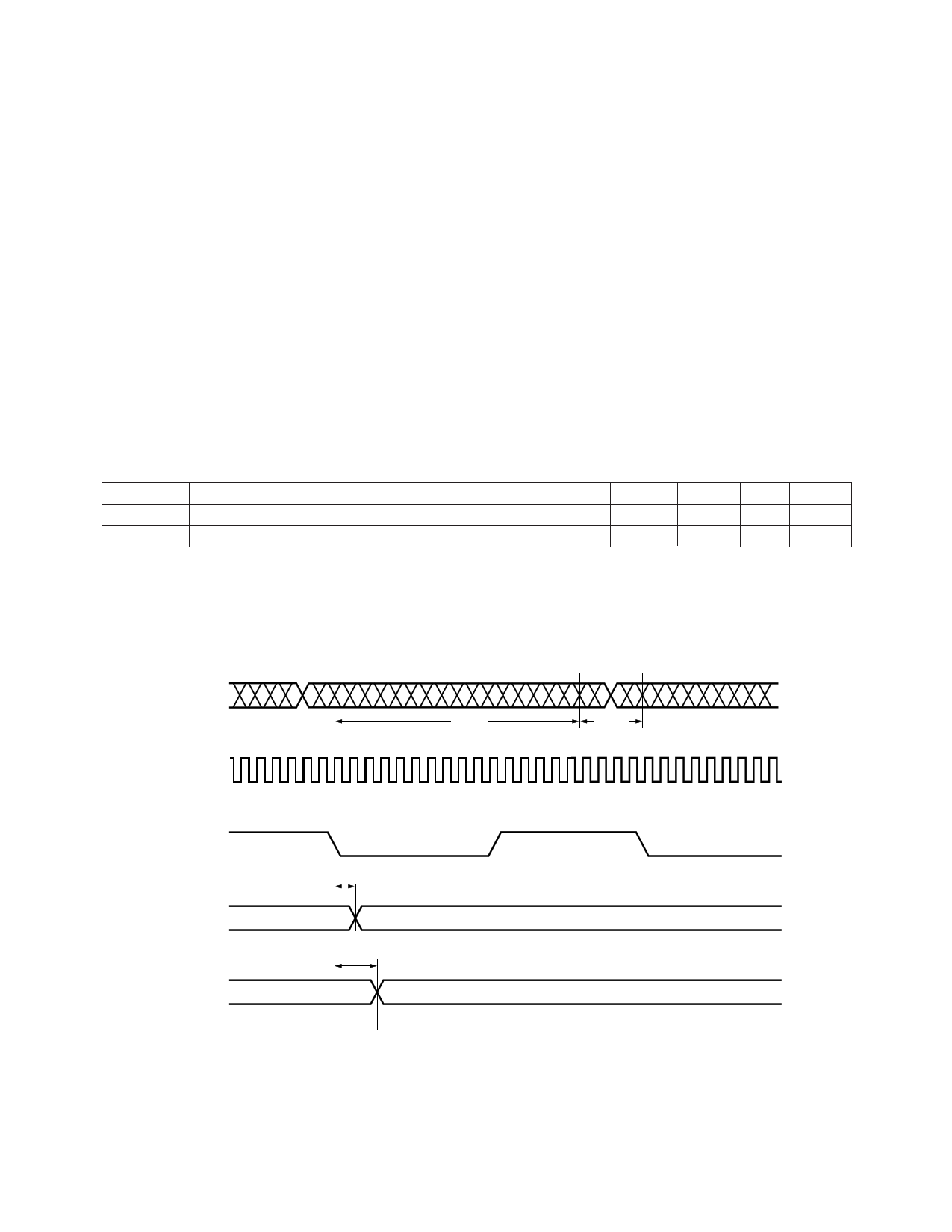

HDMP-1014 (Rx) Timing

Figure 7 is the Rx timing diagram

when the internal PLL is locked to

the incoming serial data. The

BCLK’s frequency is the same as

the input data rate. The size of

the input data frame can be either

20 bits or 24 bits, depending on

the setting of M20SEL.

Independent of the frame size,

STBROUT’s falling edge is aligned

to the data frame’s boundary,

while the rising edge is in the

center of the data frame.

The synchronous outputs, D00-

D19, LINKRDY*, DAV*, CAV*,

FF, ERROR, and FLAG, are

updated for every data frame,

with a delay of td1 after the falling

edge of STRBOUT. There is a

latency delay of two frames from

the input of the serial data frame

to the update of the synchronous

outputs.

The state machine outputs,

STAT0, and STAT1, appear with

the falling edge of STRBOUT after

a delay of td2. These outputs are

updated once every 128 frames.

HDMP-1014 (Rx) Timing Characteristics

Tc = 0°C to +85°C

Symbol

td1

td2

Parameter

Synchronous Output Delay

State Machine Output Delay

Units

nsec

nsec

Min.

Typ.

2.0

4.0

Max.

DIN

BCLK

STRBOUT

D00 - D19

LINKRDY*

DAV*, CAV*

FF, ERROR

FLAG

STAT1

STAT0

td1

td2

Figure 7. HDMP-1014 (Rx) Timing Diagram.

D-FIELD

C-FIELD

583

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HDSP-390X.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HDSP-3900 | 20 mm (0.8 inch) Seven Segment Displays | Agilent(Hewlett-Packard) |

| HDSP-3900 | (HDSP-xxxx) 7-Segment Displays | Hewlett-Packard |

| HDSP-390X | 20 mm (0.8 inch) Seven Segment Displays | Agilent(Hewlett-Packard) |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |