|

|

PDF SEC04G72C1BC2MT-xxR Data sheet ( Hoja de datos )

| Número de pieza | SEC04G72C1BC2MT-xxR | |

| Descripción | SDRAM SO-DIMM | |

| Fabricantes | Swissbit | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SEC04G72C1BC2MT-xxR (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

preliminary Data Sheet

Rev.0.9 27.08.2012

4GB DDR2 – SDRAM SO-DIMM

200 Pin SO-CDIMM

SEC04G72C1BC2MT-xxR

4GB PC2-5300 in FBGA Technology

RoHS compliant

Options:

Data Rate / Latency

Marking

DDR2 667 MT/s CL5

DDR2 533 MT/s CL4

-30

-37

Module Density

4096MB with 18 dies and 2 ranks

Standard Grade (TA)

(TC)

0°C to 70°C

0°C to 85°C

Environmental Requirements:

Operating temperature (ambient)

Standard Grade

0°C to 70°C

Operating Humidity

10% to 90% relative humidity, noncondensing

Operating Pressure

105 to 69 kPa (up to 10000 ft.)

Storage Temperature

-55°C to 100°C

Storage Humidity

5% to 95% relative humidity, noncondensing

Storage Pressure

1682 PSI (up to 5000 ft.) at 50°C

Features:

200-pin 72-bit Small Outline Clocked Dual-In-Line

Double Data Rate Synchronous DRAM Module

Module organization: dual rank 512M x 72

VDD = 1.8V ±0.1V, VDDQ 1.8V ±0.1V

1.8V I/O ( SSTL_18 compatible)

Serial Presence Detect with EEPROM

Phase-lock loop (PLL) clock driver to reduce loading

Supports ECC error detection and correction

Gold-contact pad

This module is fully pin and functional compatible to

the JEDEC PC2-6400 spec. and JEDEC- Standard

MO-224. (see www.jedec.org)

The PCB and all components are manufactured

according to the RoHS compliance specification

[EU Directive 2002/95/EC Restriction of Hazardous

Substances (RoHS)]

DDR2 - SDRAM component Micron

MT47H256M8EB-25E:C

256Mx8 DDR2 SDRAM in FBGA-60 package

Four bit prefetch architecture

DLL to align DQ and DQS transitions with CK

Eight internal device banks for concurrent operation

Programmable CAS latency (CL)

Posted CAS additive latency (AL)

WRITE latency = READ latency – 1 tCK

Programmable burst length: 4 or 8

Adjustable data-output drive strength

On-die termination (ODT)

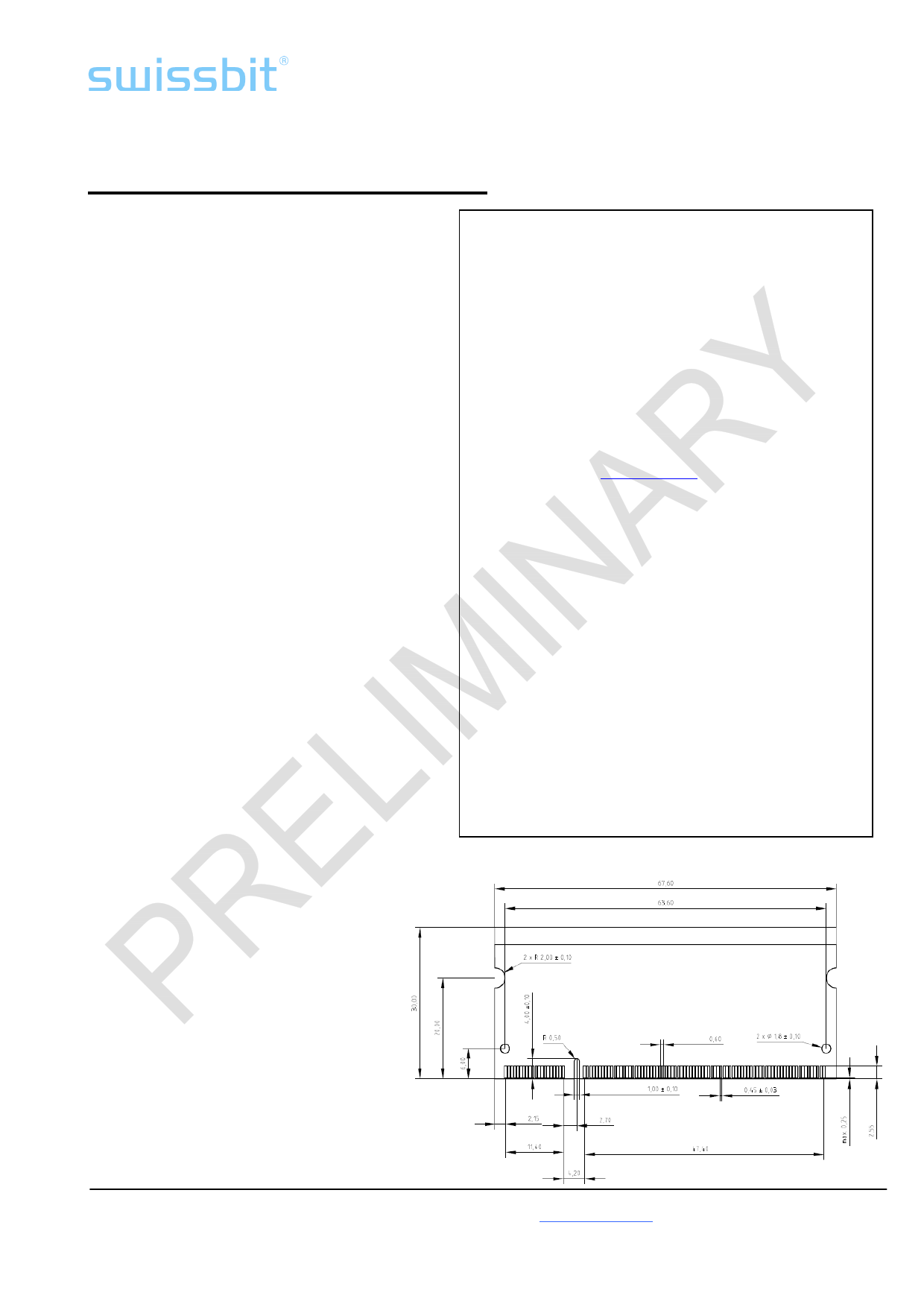

Figure: mechanical dimensions1

Swissbit AG

Industriestrasse 4

CH-9552 Bronschhofen

Fon: +41 (0) 71 913 03 03

Fax: +41 (0) 71 913 03 15

www.swissbit.com

eMail: [email protected]

1if no tolerances specified ± 0.15mm

Page 1

of 16

1 page

preliminary Data Sheet

Rev.0.9 27.08.2012

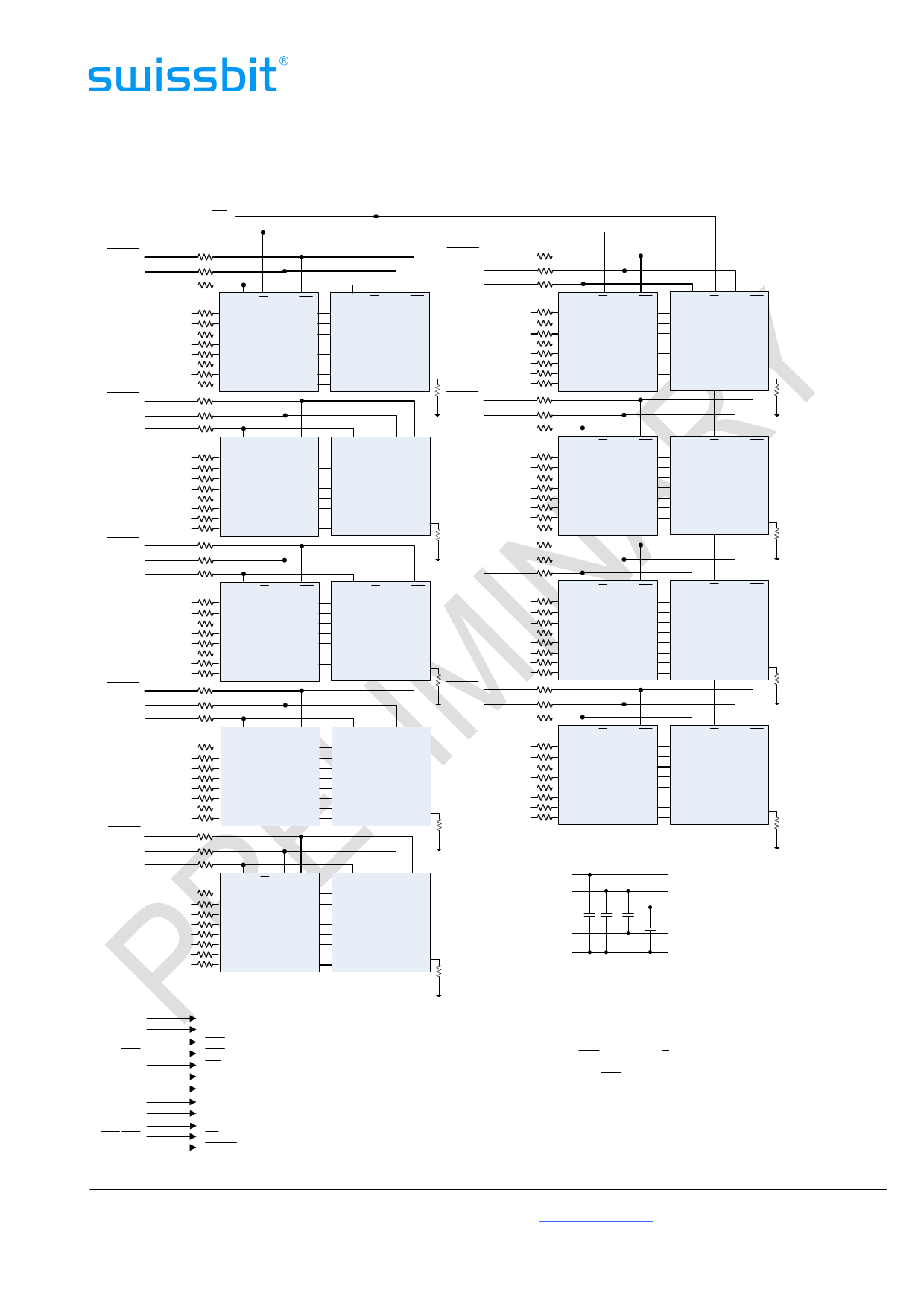

FUNCTIONAL BLOCK DIAGRAMM 4096MB DDR2 SDRAM SO-CDIMM,

2 RANKS AND 18 COMPONENTS

DQS0

DQS0

DM0

DQS1

DQS1

DM1

DQS2

DQS2

DM2

DQS3

DQS3

DM3

DQS8

DQS8

DM8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

S1

S0

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D0

ZQ

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D9

ZQ

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D1

ZQ

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CS DQS DQS

D10

ZQ

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D2

ZQ

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D11

ZQ

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D3

ZQ

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D12

ZQ

DQS4

DQS4

DM4

DQS5

DQS5

DM5

DQS6

DQS6

DM6

DQS7

DQS7

DM7

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D8

ZQ

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CS DQS DQS

D17

ZQ

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D4

ZQ

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CS DQS DQS

D13

ZQ

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D5

ZQ

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CS DQS DQS

D14

ZQ

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D6

ZQ

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CS DQS DQS

D15

ZQ

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM CS DQS DQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D7

ZQ

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CS DQS DQS

D16

ZQ

VDDSPD

VDD/VDDQ

VREFDQ

VREFCA

VSS

SPD

D0-D17

D0-D17

D0-D17

D0-D17

BA0-BA2

A0-A14

RAS

CAS

WE

ODT0

ODT1

CKE0

CKE1

CK0,CK1

CK0,CK1

RESET

BA0-BA2: SDRAM D0-D17

A0-A14: SDRAM D0-D17

RAS: SDRAM D0-D17

CAS: SDRAM D0-D17

WE: SDRAM D0-D17

ODT: SDRAM D0-D8

ODT: SDRAM D9-D17

CKE: SDRAM D0-D8

CKE: SDRAM D9-D17

CK: SDRAM D0-D17

CK: SDRAM D0-D17

RESET: SDRAM D0-D17

Notes:

1. DQ-to-I/O wiring is shown as recommended but may

be changed.

2. DQ/DQS/DQS/ODT/DM/CKE/S relationship must be

maintained as shown.

3. DQ, DM, DQS/DQS resistors: Refer to associated

topology diagram.

4. Refer to the appropriate clock wiring topology under

the DIMM wiring details section of the JEDED document.

5. For each DRAM, a unique ZQ resistor is connected to

GND. The ZQ resistor is 240O±1%.

6. Refer to associated figure for SPD details.

Swissbit AG

Industriestrasse 4

CH-9552 Bronschhofen

Fon: +41 (0) 71 913 03 03

Fax: +41 (0) 71 913 03 15

www.swissbit.com

eMail: [email protected]

Page 5

of 16

5 Page

preliminary Data Sheet

Rev.0.9 27.08.2012

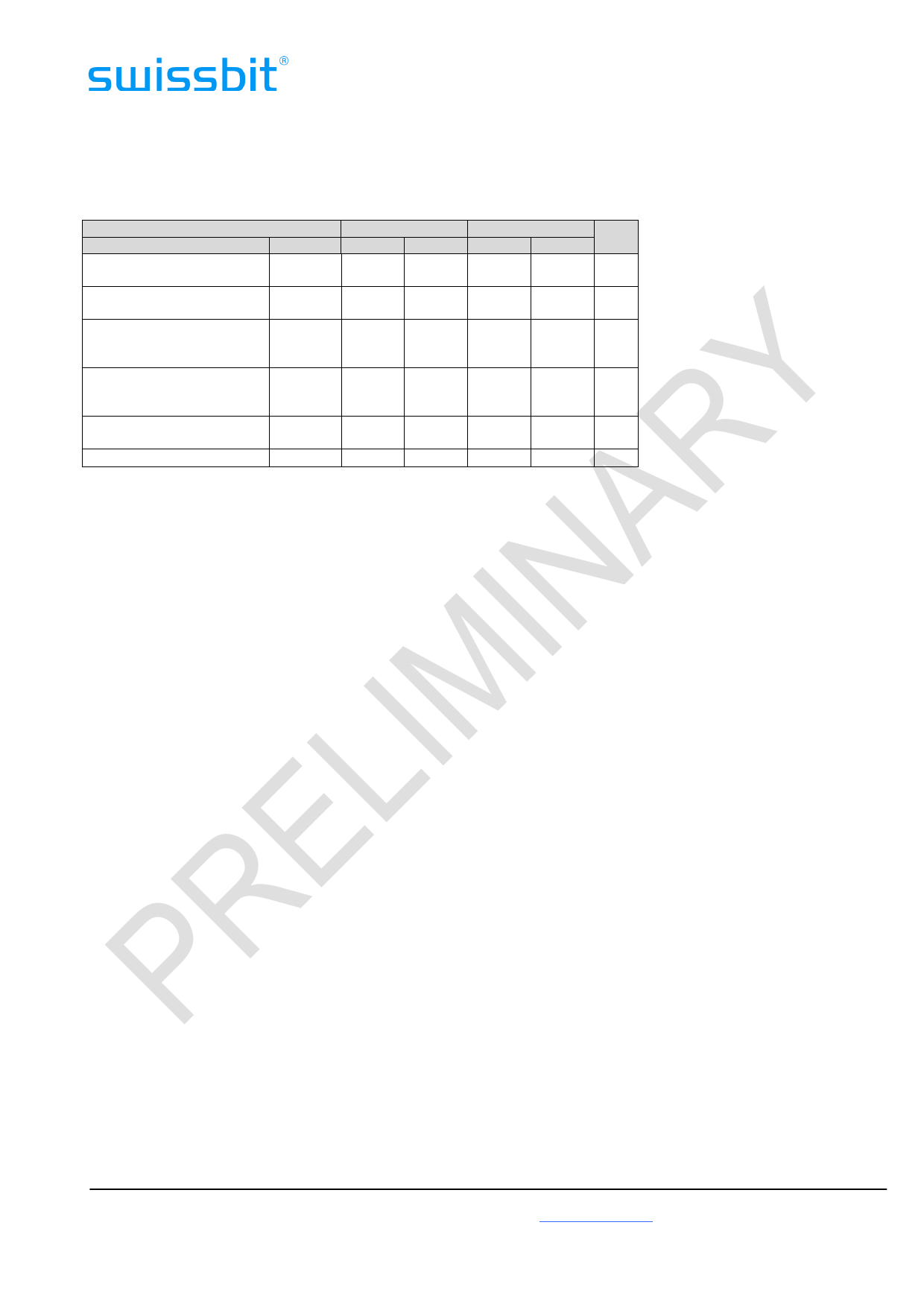

DDR2 SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND RECOMMENDED

AC OPERATING CONDITIONS (Continued)

(0°C ≤ TCASE ≤ + 85°C; VDDQ = +1.8V ± 0.1V, VDD = +1.8V ± 0.1V)

AC CHARACTERISTICS

PARAMETER

SYMBOL

ODT power-down exit

latency

tAXPD

ODT enable from MRS

command

TMOD

Exit active power-down to tXARD

READ command, MR [bit 12

= 0]

Exit active power-down to tXARDS

READ command, MR [bit 12

= 1]

Exit precharge power-down tXP

to any non-READ command

CKE minimum high/low time tCKE

5300-5-5-5

MIN MAX

8-

12 -

2-

7 – AL

-

2-

3-

4200-4-4-4

MIN MAX

8-

12 -

2-

Unit

tCK

ns

tCK

6 – AL - tCK

2 - tCK

3 - tCK

Swissbit AG

Industriestrasse 4

CH-9552 Bronschhofen

Fon: +41 (0) 71 913 03 03

Fax: +41 (0) 71 913 03 15

www.swissbit.com

eMail: [email protected]

Page 11

of 16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet SEC04G72C1BC2MT-xxR.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SEC04G72C1BC2MT-xxR | SDRAM SO-DIMM | Swissbit |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |