|

|

PDF HC161 Data sheet ( Hoja de datos )

| Número de pieza | HC161 | |

| Descripción | Presettable Counters | |

| Fabricantes | System Logic Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HC161 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

SL74HC161

Presettable Counters

High-Performance Silicon-Gate CMOS

The SL74HC161 is identical in pinout to the LS/ALS161. The device

inputs are compatible with standard CMOS outputs; with pullup

resistors, they are compatible with LS/ALSTTL outputs.

The SL74HC161 is programmable 4-bit synchronous counter that

feature parallel Load, asynchronous Reset, a Carry Output for

cascading and count-enable controls.

The SL74HC161 is binary counter with asynchronous Reset.

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2.0 to 6.0 V

• Low Input Current: 1.0 µA

• High Noise Immunity Characteristic of CMOS Devices

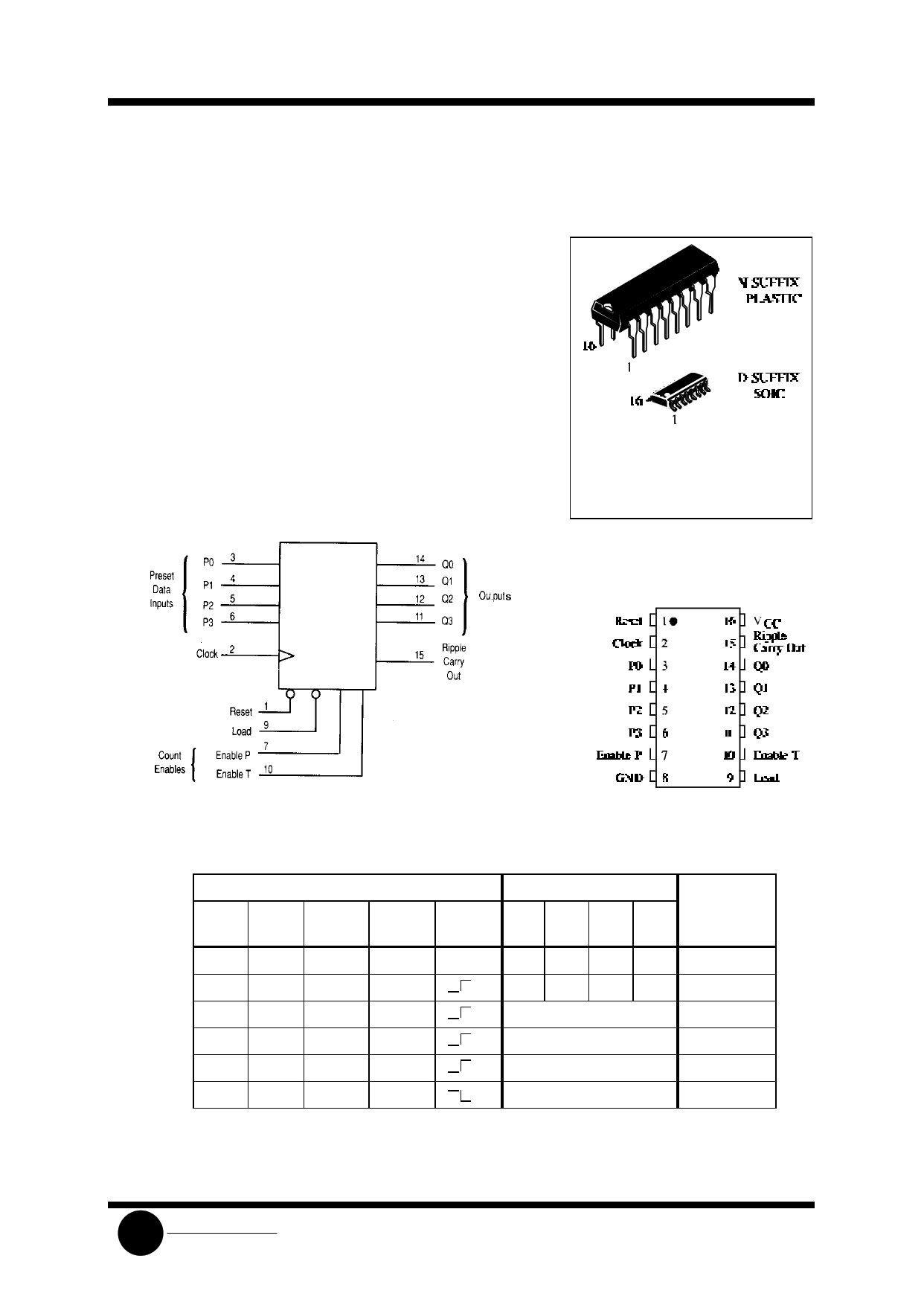

LOGIC DIAGRAM

ORDERING INFORMATION

SL74HC161N Plastic

SL74HC161D SOIC

TA = -55° to 125° C for all packages

PIN ASSIGNMENT

PIN 16 =VCC

PIN 8 = GND

FUNCTION TABLE

Inputs

Outputs

Reset Load Enable Enable Clock Q0 Q1 Q2 Q3

PT

Function

LX

X

X

X L L L L Reset to “0”

HL

X

X

P0 P1 P2 P3 Preset Data

HH

X

L

No change

No count

HH

L

X

No change

No count

HH

H

H

Count up

Count

HX

X

X

No change

No count

X=don’t care

P0,P1,P2,P3 = logic level of Data inputs

Ripple Carry Out = Enable T • Q0 • Q1 • Q2 • Q3

SLS

System Logic

Semiconductor

1 page

SL74HC161

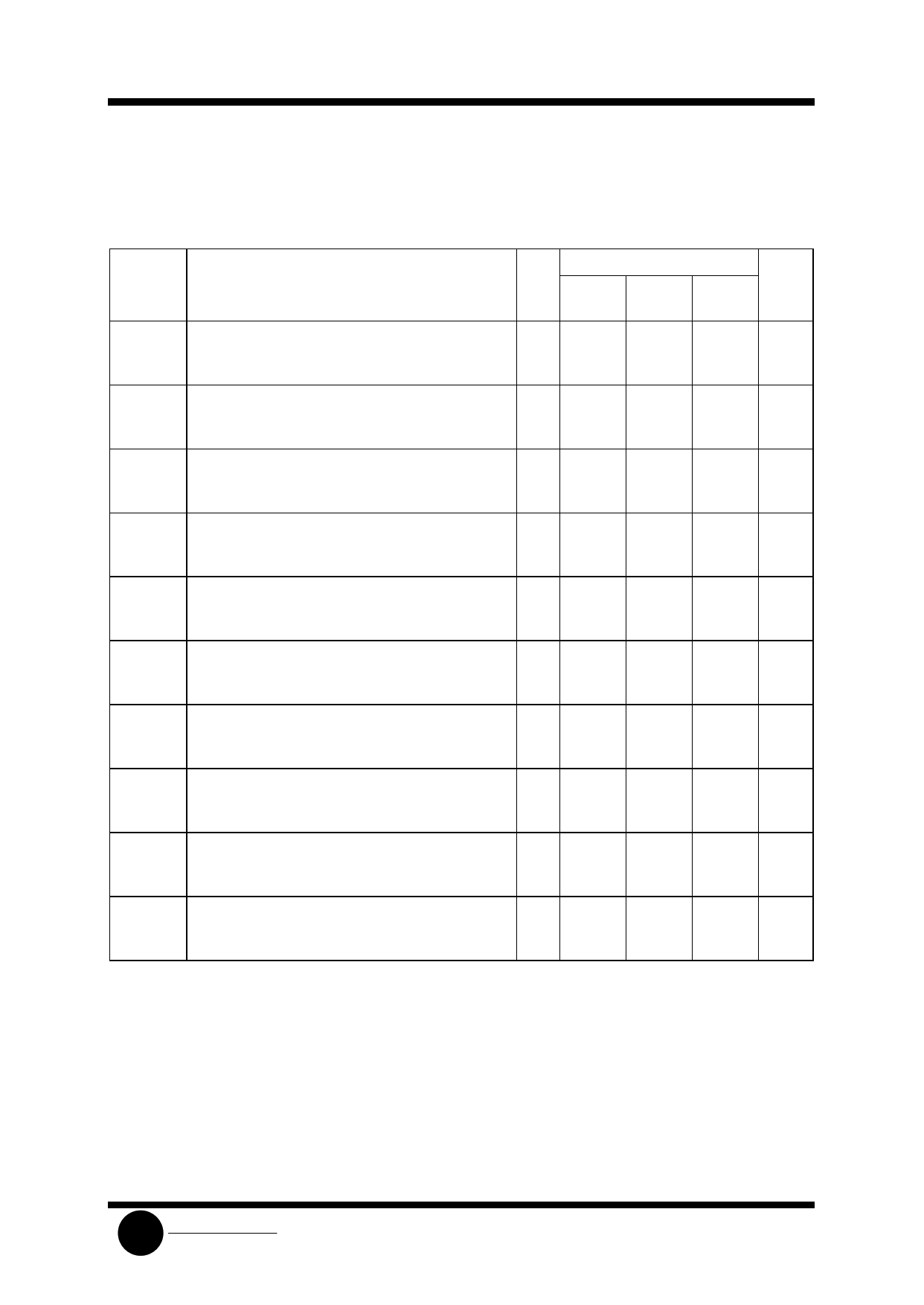

TIMING REQUIREMENTS (CL=50pF,Input tr=tf=6.0 ns)

Symbol

Parameter

VCC Guaranteed Limit

V 25 °C to ≤85°C ≤125°C

-55°C

tSU Minimum Setup Time, Preset Data Inputs to Clock 2.0 40 60 80

(Figure 4)

4.5 15 20 30

6.0 12 18 20

tSU Minimum Setup Time, Load to Clock

(Figure 4)

2.0 60 75 90

4.5 15 20 30

6.0 12 18 20

tSU Minimum Setup Time, Enable T or Enable P to 2.0 80 95 110

Clock (Figure 5)

4.5 20 25 35

6.0 17 23 25

th Minimum Hold Time, Clock to Load or Preset Data 2.0 3 3 3

Inputs (Figure 4)

4.5 3 3 3

6.0 3 3 3

th Minimum Hold Time, Clock to Enable T or Enable 2.0 3 3 3

P (Figure 5)

4.5 3 3 3

6.0 3 3 3

trec Minimum Recovery Time, Reset Inactive to Clock 2.0 80 95 110

(Figure 2)

4.5 15 20 26

6.0 12 17 23

trec Minimum Recovery Time, Load Inactive to Clock 2.0 80 95 110

(Figure 4)

4.5 15 20 26

6.0 12 17 23

tw Minimum Pulse Width, Clock (Figure 1)

2.0 60 75 90

4.5 12 15 18

6.0 10 13 15

tw Minimum Pulse Width, Reset (Figure 2)

2.0 60 75 90

4.5 12 15 18

6.0 10 13 15

tr, tf Maximum Input Rise and Fall Times

(Figure 1)

2.0 1000 1000 1000

4.5 500 500 500

6.0 400 400 400

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

SLS

System Logic

Semiconductor

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet HC161.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HC1600P03 | Hybrid Coupler | Yantel |

| HC160101C-VA | Character LCD module | HTDisplay |

| HC160101C-VA | LCD module | HTDisplay |

| HC160102C-VA | Character LCD module | HTDisplay |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |