|

|

PDF CAV25040 Data sheet ( Hoja de datos )

| Número de pieza | CAV25040 | |

| Descripción | EEPROM | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CAV25040 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

CAV25010, CAV25020,

CAV25040

1-Kb, 2-Kb and 4-Kb SPI

Serial CMOS EEPROM

Description

The CAV25010/20/40 are 1−Kb/2−Kb/4−Kb Serial CMOS

EEPROM devices internally organized as 128x8/256x8/512x8 bits.

They feature a 16−byte page write buffer and support the Serial

Peripheral Interface (SPI) protocol. The device is enabled through a

Chip Select (CS) input. In addition, the required bus signals are a clock

input (SCK), data input (SI) and data output (SO) lines. The HOLD

input may be used to pause any serial communication with the

CAV25010/20/40 device. These devices feature software and

hardware write protection, including partial as well as full array

protection.

Features

• Automotive Temperature Grade 1 (−40°C to +125°C)

• 10 MHz SPI Compatible

• 2.5 V to 5.5 V Supply Voltage Range

• SPI Modes (0,0) & (1,1)

• 16−byte Page Write Buffer

• Self−timed Write Cycle

• Hardware and Software Protection

• Block Write Protection

− Protect 1/4, 1/2 or Entire EEPROM Array

• Low Power CMOS Technology

• 1,000,000 Program/Erase Cycles

• 100 Year Data Retention

• Industrial and Extended Temperature Range

• SOIC and TSSOP 8−Lead Packages

• These Devices are Pb−Free, Halogen Free/BFR Free, and RoHS

Compliant

VCC

SI

CS

WP

HOLD

SCK

CAV25010

CAV25020

CAV25040

SO

VSS

Figure 1. Functional Symbol

http://onsemi.com

SOIC−8

V SUFFIX

CASE 751BD

TSSOP−8

Y SUFFIX

CASE 948AL

PIN CONFIGURATION

CS 1

SO

VCC

HOLD

WP SCK

VSS SI

SOIC (V), TSSOP (Y)

For the location of Pin 1, please consult the

corresponding package drawing.

Pin Name

CS

SO

WP

VSS

SI

SCK

HOLD

VCC

PIN FUNCTION

Function

Chip Select

Serial Data Output

Write Protect

Ground

Serial Data Input

Serial Clock

Hold Transmission Input

Power Supply

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 12 of this data sheet.

© Semiconductor Components Industries, LLC, 2012

January, 2012 − Rev. 0

1

Publication Order Number:

CAV25010/D

1 page

CAV25010, CAV25020, CAV25040

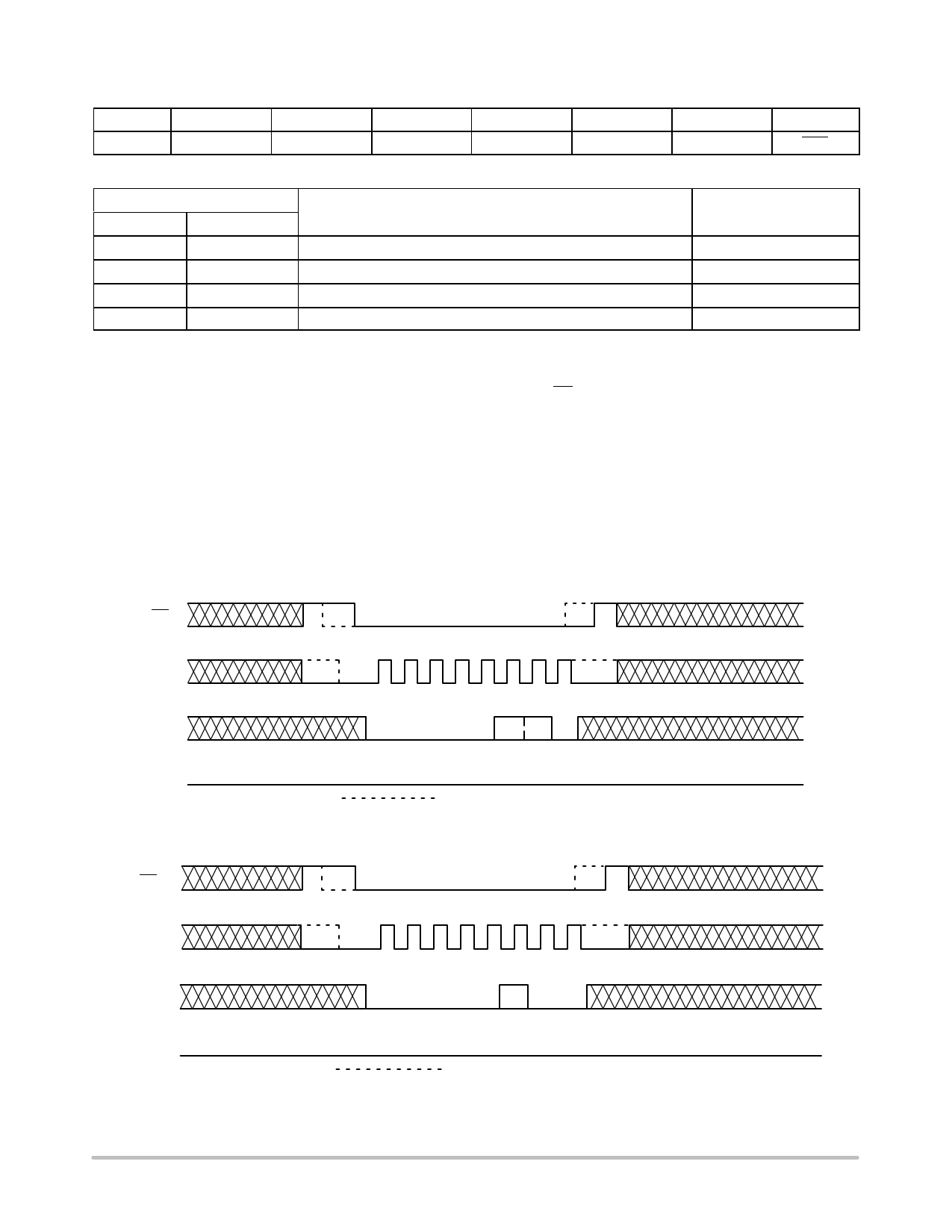

Table 8. STATUS REGISTER

76

11

5

1

4 3 2 10

1

BP1

BP0

WEL

RDY

Table 9. BLOCK PROTECTION BITS

Status Register Bits

BP1 BP0

Array Address Protected

0 0 None

0 1 CAV25010: 060−07F, CAV25020: 0C0−0FF, CAV25040: 180−1FF

1 0 CAV25010: 040−07F, CAV25020: 080−0FF, CAV25040: 100−1FF

1 1 CAV25010: 000−07F, CAV25020: 000−0FF, CAV25040: 000−1FF

Protection

No Protection

Quarter Array Protection

Half Array Protection

Full Array Protection

WRITE OPERATIONS

The CAV25010/20/40 device powers up into a write

disable state. The device contains a Write Enable Latch

(WEL) which must be set before attempting to write to the

memory array or to the status register. In addition, the

address of the memory location(s) to be written must be

outside the protected area, as defined by BP0 and BP1 bits

from the status register.

Write Enable and Write Disable

The internal Write Enable Latch and the corresponding

Status Register WEL bit are set by sending the WREN

instruction to the CAV25010/20/40. Care must be taken to

take the CS input high after the WREN instruction, as

otherwise the Write Enable Latch will not be properly set.

WREN timing is illustrated in Figure 3. The WREN

instruction must be sent prior to any WRITE or WRSR

instruction.

The internal write enable latch is reset by sending the

WRDI instruction as shown in Figure 4. Disabling write

operations by resetting the WEL bit, will protect the device

against inadvertent writes.

CS

SCK

SI

SO

Dashed Line = mode (1, 1)

0 0 0 00 1 10

HIGH IMPEDANCE

Figure 3. WREN Timing

CS

SCK

SI

SO

Dashed Line = mode (1, 1)

00 0 0 0 1 00

HIGH IMPEDANCE

Figure 4. WRDI Timing

http://onsemi.com

5

5 Page

CAV25010, CAV25020, CAV25040

PACKAGE DIMENSIONS

TSSOP8, 4.4x3

CASE 948AL−01

ISSUE O

b

e

TOP VIEW

D

A2

E1 E

A

SYMBOL

A

A1

A2

b

c

D

E

E1

e

L

L1

θ

MIN

0.05

0.80

0.19

0.09

2.90

6.30

4.30

0.50

0º

NOM

0.90

3.00

6.40

4.40

0.65 BSC

1.00 REF

0.60

MAX

1.20

0.15

1.05

0.30

0.20

3.10

6.50

4.50

0.75

8º

c

q1

SIDE VIEW

A1

Notes:

(1) All dimensions are in millimeters. Angles in degrees.

(2) Complies with JEDEC MO-153.

L1

END VIEW

L

http://onsemi.com

11

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet CAV25040.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CAV25040 | EEPROM | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |