|

|

PDF NLSX4402 Data sheet ( Hoja de datos )

| Número de pieza | NLSX4402 | |

| Descripción | 2-Bit 20 Mb/s Dual-Supply Level Translator | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NLSX4402 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

NLSX4402

2-Bit 20 Mb/s Dual-Supply

Level Translator

The NLSX4402 is a 2−bit configurable dual−supply bidirectional

auto sensing translator that does not require a directional control pin.

The VCC I/O and VL I/O ports are designed to track two different

power supply rails, VCC and VL respectively. Both the VCC and VL

supply rails are configurable from 1.5 V to 5.5 V. This allows voltage

logic signals on the VL side to be translated into lower, higher or

equal value voltage logic signals on the VCC side, and vice−versa.

The NLSX4402 translator has internal pull−up resistors on the I/O

lines. The pull−up resistors are used to pull up the I/O lines to either

VL or VCC. The NLSX4402 is an excellent match for open−drain

applications such as the I2C communication bus.

Features

• VL can be Less than, Greater than or Equal to VCC

• Wide VCC Operating Range: 1.5 V to 5.5 V

Wide VL Operating Range: 1.5 V to 5.5 V

• Enable Input and I/O Pins are Overvoltage Tolerant (OVT) to 5.5 V

• Non−preferential Powerup Sequencing

• Power−Off Protection

• Small Space Saving Package: 1.45 mm x 1.0 mm UDFN8 Package

• These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS

Compliant

Typical Applications

• I2C, SMBus

• Low Voltage ASIC Level Translation

• Mobile Phones, PDAs, Cameras

Important Information

• ESD Protection for All Pins

− Human Body Model (HBM) > 5000 V

www.onsemi.com

UDFN8

1.45 x 1.0

CASE 517BZ

MARKING

DIAGRAMS

JM

1

J = Specific Device Code

M = Date Code

LOGIC DIAGRAM

VL VCC GND

EN

I/O VL1

I/O VCC1

I/O VL2

I/O VCC2

ORDERING INFORMATION

Device

Package Shipping†

NLSX4402FMUTCG UDFN8 3000 / Tape &

(Pb−Free)

Reel

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specification

Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2015

June, 2015 − Rev. 1

1

Publication Order Number:

NLSX4402/D

1 page

NLSX4402

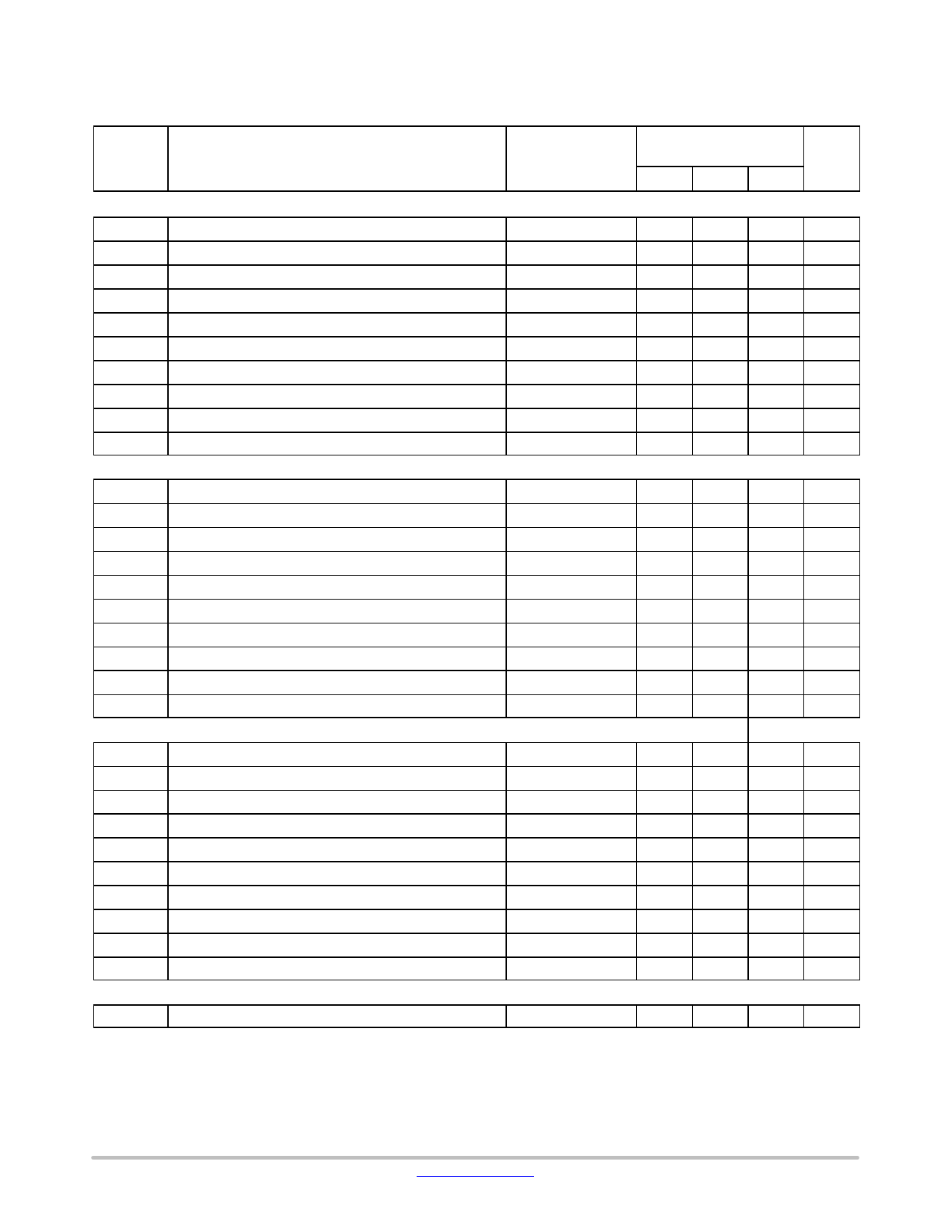

TIMING CHARACTERISTICS − RAIL−TO−RAIL DRIVING CONFIGURATIONS

(I/O test circuit of Figures 3 and 4, CLOAD = 15 pF, driver output impedance ≤ 50 W, RLOAD = 1 MW)

−405C to +855C

(Notes 3 & 4)

Symbol

Parameter

Test Conditions Min Typ Max Unit

VL = 1.5 V, VCC = 1.5 V

tRVCC

tFVCC

tRVL

tFVL

tPDVL−VCC

tPDVCC−VL

tEN

tDIS

tPPSKEW

MDR

I/O VCC Rise Time

I/O VCC Fall Time

I/O VL Rise Time

I/O VL Fall Time

Propagation Delay (Driving I/O VL, VL to VCC)

Propagation Delay (Driving I/O VCC, VCC to VL)

Enable Time

Disable Time

Part−to−Part Skew

Maximum Data Rate

9 32 ns

11 20 ns

20 30 ns

10 13 ns

7 16 ns

12 15 ns

50 ns

300 ns

2 ns

15 Mbps

VL = 1.5 V, VCC = 5.5 V

tRVCC I/O VCC Rise Time

tFVCC I/O VCC Fall Time

tRVL I/O VL Rise Time

tFVL I/O VL Fall Time

tPDVL−VCC Propagation Delay (Driving I/O VL, VL to VCC)

tPDVCC−VL Propagation Delay (Driving I/O VCC, VCC to VL)

tEN Enable Time

tDIS Disable Time

tPPSKEW Part−to−Part Skew

MDR Maximum Data Rate

9 12 ns

17 30 ns

2 4 ns

3 7 ns

14 24 ns

3 5 ns

40 ns

250 ns

2 ns

20 Mbps

VL = 1.8 V, VCC = 2.8 V

tRVCC I/O VCC Rise Time

tFVCC I/O VCC Fall Time

tRVL I/O VL Rise Time

tFVL I/O VL Fall Time

tPDVL−VCC Propagation Delay (Driving I/O VL, VL to VCC)

tPDVCC−VL Propagation Delay (Driving I/O VCC, VCC to VL)

tEN Enable Time

tDIS Disable Time

tPPSKEW Part−to−Part Skew

MDR Maximum Data Rate

11 18 ns

10 15 ns

12 15 ns

5 8 ns

7 10 ns

5 9 ns

50 ns

300 ns

2 ns

20 Mbps

VL = 2.5 V, VCC = 3.6 V

tRVCC I/O VCC Rise Time

8 12 ns

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. Typical values are for the specified VL and VCC at TA = +25°C. All units are production tested at TA = +25°C.

4. Limits over the operating temperature range are guaranteed by design.

5. Skew is the variation of propagation delay between output signals and applies only to output signals on the same port (I/O_VLn or I/O_VCCn)

and switching with the same polarity (LOW−to−HIGH or HIGH−to−LOW). Skew is defined by applying a single input to the two input channels

and measuring the difference in propagation delays between the output channels.

www.onsemi.com

5

5 Page

PULSE

GENERATOR

NLSX4402

VCC

DUT

RT

R1

CL RL

2xVCC

OPEN

Test Switch

tPZH, tPHZ

Open

tPZL, tPLZ

2 x VCC

CL = 15 pF or equivalent (Includes jig and probe capacitance)

RL = R1 = 50 kW or equivalent

RT = ZOUT of pulse generator (typically 50 W)

Figure 8. Test Circuit for Enable/Disable Time Measurement

Input

tR

tPLH

Output

90%

50%

10%

90%

50%

10%

tR

tF

VCC

GND

tPHL

tF

EN

Output

Output

50%

tPZL tPLZ

50%

tPZH tPHZ

50%

VL

10%

90%

GND

HIGH

IMPEDANCE

VOL

VOH

HIGH

IMPEDANCE

Figure 9. Timing Definitions for Propagation Delays and Enable/Disable Measurement

www.onsemi.com

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet NLSX4402.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NLSX4402 | 2-Bit 20 Mb/s Dual-Supply Level Translator | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |