|

|

PDF 74LV4052 Data sheet ( Hoja de datos )

| Número de pieza | 74LV4052 | |

| Descripción | Dual 4-channel analog multiplexer/demultiplexer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LV4052 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

74LV4052

Dual 4-channel analog multiplexer/demultiplexer

Rev. 4 — 1 July 2013

Product data sheet

1. General description

The 74LV4052 is a low-voltage CMOS device and is pin and function compatible with the

74HC/HCT4052.

The 74LV4052 is a dual 4-channel analog multiplexer/demultiplexer with a common select

logic. Each multiplexer has four independent inputs/outputs (nY0 to nY3) and a common

input/output (nZ). The common channel select logics include two digital select inputs (S0

and S1) and an active LOW enable input (E). With E LOW, one of the four switches is

selected (low impedance ON-state) by S0 and S1. With E HIGH, all switches are in the

high impedance OFF-state, independent of S0 and S1. VCC and GND are the supply

voltage pins for the digital control inputs (S0, S1 and E). The VCC to GND ranges are 1.0 V

to 6.0 V. The analog inputs/outputs (nY0, to nY3, and nZ) can swing between VCC as a

positive limit and VEE as a negative limit. VCC - VEE may not exceed 6.0 V. For operation

as a digital multiplexer/demultiplexer, VEE is connected to GND (typically ground).

2. Features and benefits

Optimized for low-voltage applications: 1.0 V to 6.0 V

Accepts TTL input levels between VCC = 2.7 V and VCC = 3.6 V

Low ON resistance:

145 (typical) at VCC VEE = 2.0 V

90 (typical) at VCC VEE = 3.0 V

60 (typical) at VCC VEE = 4.5 V

Logic level translation:

To enable 3 V logic to communicate with 3 V analog signals

Typical ‘break before make’ built in

ESD protection:

HBM JESD22-A114E exceeds 2000 V

MM JESD22-A115-A exceeds 200 V

Multiple package options

Specified from 40 C to +85 C and from 40 C to +125 C

1 page

NXP Semiconductors

74LV4052

Dual 4-channel analog multiplexer/demultiplexer

6. Functional description

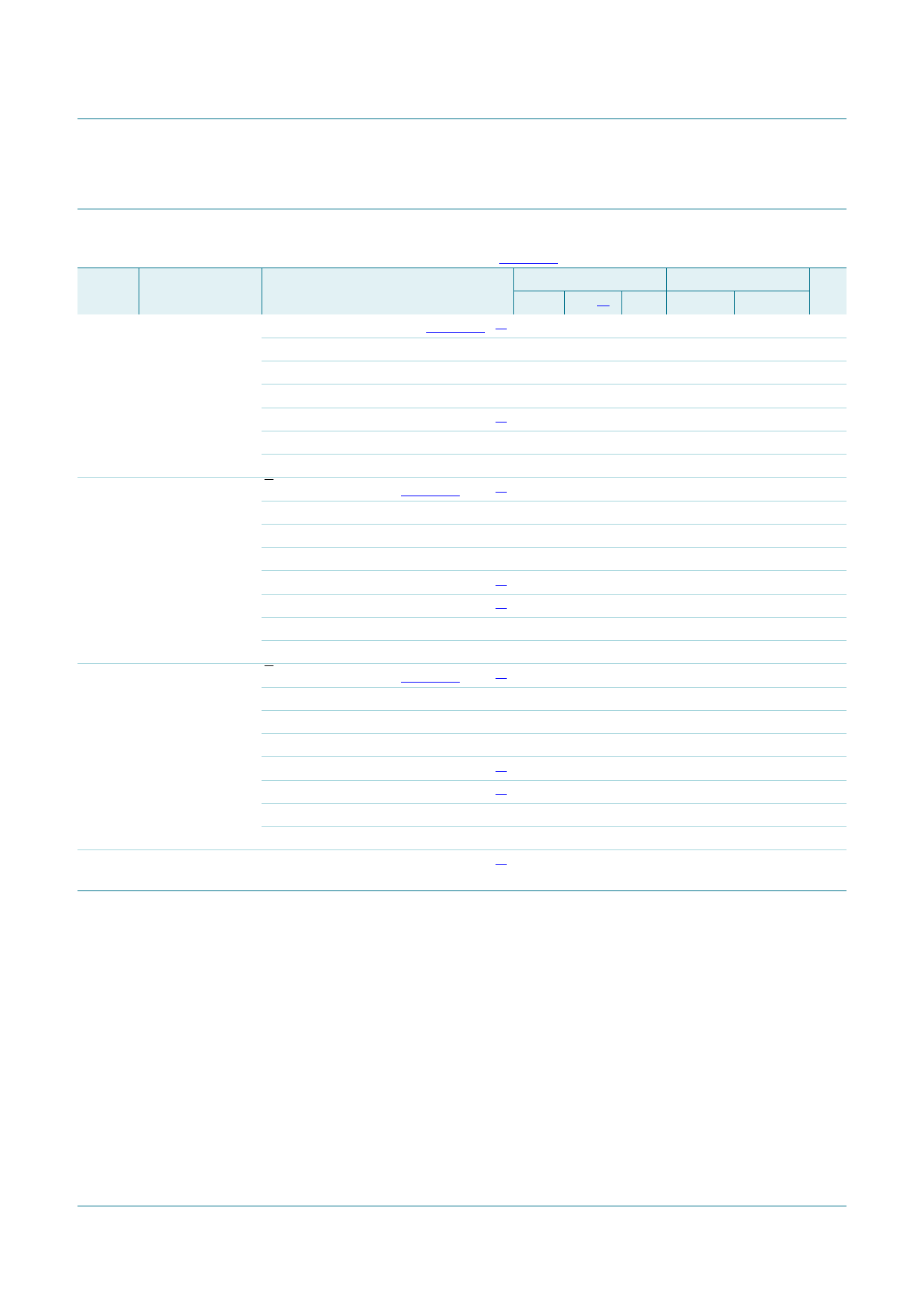

Table 3.

Input

E

L

L

L

L

H

Function table[1]

S1

L

L

H

H

X

S0

L

H

L

H

X

[1] H = HIGH voltage level; L = LOW voltage level; X = don’t care.

7. Limiting values

Channel on

nY0 and nZ

nY1 and nZ

nY2 and nZ

nY3 and nZ

none

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS = 0 V (ground).

Symbol

Parameter

Conditions

Min Max Unit

VCC supply voltage

[1] 0.5

+7.0

V

IIK

input clamping current VI < 0.5 V or VI > VCC + 0.5 V

[2] -

20 mA

ISK switch clamping current VSW < 0.5 V or VSW > VCC + 0.5 V [2] -

20 mA

ISW switch current

VSW > 0.5 V or VSW < VCC + 0.5 V;

source or sink current

[2] -

25 mA

Tstg storage temperature

Ptot total power dissipation Tamb = 40 C to +125 C

DIP16 package

65

[3]

-

+150

750

C

mW

SO16 package

- 500 mW

SSOP16 and TSSOP16 package

-

400 mW

[1] To avoid drawing VCC current out of terminal nZ, when switch current flows into terminals nYn, the voltage drop across the bidirectional

switch must not exceed 0.4 V. If the switch current flows into terminal nZ, no VCC current flows out of terminals nYn. In this case, there is

no limit for the voltage drop across the switch, but the voltages at nYn and nZ may not exceed VCC or VEE.

[2] The minimum input voltage rating may be exceeded if the input current rating is observed.

[3] For DIP16 package: above 70 C the value of Ptot derates linearly with 12 mW/K.

For SO16 package: above 70 C the value of Ptot derates linearly with 8 mW/K.

For SSOP16 and TSSOP16 packages: above 60 C the value of Ptot derates linearly with 5.5 mW/K.

74LV4052

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 1 July 2013

© NXP B.V. 2013. All rights reserved.

5 of 26

5 Page

NXP Semiconductors

74LV4052

Dual 4-channel analog multiplexer/demultiplexer

10. Dynamic characteristics

Table 8. Dynamic characteristics

Voltages are referenced to GND (ground = 0 V). For test circuit, see Figure 14.

Symbol Parameter

Conditions

40 C to +85 C

Min Typ[1] Max

tpd propagation delay nYn to nZ, nZ to nYn; see Figure 12 [2]

VCC = 1.2 V

- 25 -

VCC = 2.0 V

- 9 17

VCC = 2.7 V

VCC = 3.0 V to 3.6 V

-

[3] -

6 13

5 10

VCC = 4.5 V

- 49

ten enable time

VCC = 6.0 V

E, Sn to nYn, nZ; see Figure 13

-

[2]

37

VCC = 1.2 V

- 190 -

VCC = 2.0 V

- 65 121

VCC = 2.7 V

VCC = 3.0 V to 3.6 V; CL = 15 pF

VCC = 3.0 V to 3.6 V

[3]

[3]

-

-

-

48 89

30 -

36 71

VCC = 4.5 V

- 32 60

tdis disable time

VCC = 6.0 V

E, Sn to nYn, nZ; see Figure 13

-

[2]

25 46

VCC = 1.2 V

- 125 -

VCC = 2.0 V

- 43 80

VCC = 2.7 V

VCC = 3.0 V to 3.6 V; CL = 15 pF

VCC = 3.0 V to 3.6 V

[3]

[3]

-

-

-

33 59

22 -

26 48

VCC = 4.5 V

- 23 41

VCC = 6.0 V

CPD power dissipation CL = 50 pF; fi = 1 MHz;

capacitance

VI = GND to VCC

-

[4] -

18 32

57 -

40 C to +125 C Unit

Min Max

- - ns

- 20 ns

- 15 ns

- 12 ns

- 10 ns

- 8 ns

- - ns

- 146 ns

- 108 ns

- - ns

- 86 ns

- 73 ns

- 56 ns

- - ns

- 95 ns

- 71 ns

- - ns

- 57 ns

- 49 ns

- 38 ns

- - pF

[1] All typical values are measured at Tamb = 25 C.

[2] tpd is the same as tPLH and tPHL.

ten is the same as tPZL and tPZH.

tdis is the same as tPLZ and tPHZ.

[3] Typical values are measured at nominal supply voltage (VCC = 3.3 V).

[4] CPD is used to determine the dynamic power dissipation (PD in W).

PD = CPD VCC2 fi N + ((CL Csw VCC2 fo) where:

fi = input frequency in MHz, fo = output frequency in MHz

CL = output load capacitance in pF

Csw = maximum switch capacitance in pF;

VCC = supply voltage in Volts

N = number of inputs switching

(CL VCC2 fo) = sum of the outputs.

74LV4052

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 1 July 2013

© NXP B.V. 2013. All rights reserved.

11 of 26

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet 74LV4052.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LV4051 | 8-channel analog multiplexer/demultiplexer | Philips |

| 74LV4052 | Dual 4-channel analog multiplexer/demultiplexer | Philips |

| 74LV4052 | Dual 4-channel analog multiplexer/demultiplexer | NXP Semiconductors |

| 74LV4053 | Triple 2-channel analog multiplexer/demultiplexer | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |