|

|

PDF PC1030N Data sheet ( Hoja de datos )

| Número de pieza | PC1030N | |

| Descripción | NTSC/PAL CMOS Image Sensor | |

| Fabricantes | Pixelplus | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PC1030N (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

Brief Data sheet

Issue No : PD-701-028

1/4 inch VGA class Analog/Digital Output

NTSC/PAL CMOS Image Sensor

PC1030N

Rev 1.2

Last update : 14 . Dec. 2010

6th Floor, Gyeonggi R&DB Center, 906-5 Iui-dong, Yeongtong-gu,

Suwon-si, Gyeonggi-do, 443-766, Korea

Tel : 82-31-888-5300, FAX : 82-31-888-5398

Copyright ⓒ 2009, Pixelplus Co.,Ltd

ALL RIGHTS RESERVED

1 page

PC1030N

1/4 inch VGA class Analog/Digital Output

NTSC/PAL CMOS Image Sensor

▶ PIN Descriptions

PIN Name

I/O

No. Type

1 HSYNC

O

2 D6

3 D7

4 VSYNC

5 RSTB

O

O

O

I

6 AVDD

7 N.C

8 N.C

9 AGND

10 STDBY

P

P

I

11 CVDD

12 CP

13 CN

14 AVDD1

15 AGND1

16 CGND

17 REXT

18 TE

19 D0

20 D1

21 D2

22 D3

23 X1

24 X2

25 PCLK

26 LEDCTRL0

P

O

O

P

P

P

I

I

O

O

O

O

I

O

O

O

[ Table 2 ] Pin Descriptions

Functions / Descriptions

Horizontal synchronization pulse. HSYNC is high ( or low ) for the horizontal window of

interest. It can be programmed to appear or not outside the vertical window of interest.

Bit 6 of parallel data output.

Bit 7 of parallel data output.

Vertical sync : Indicates the start of a new frame.

System reset must remain low for at least 8 master clocks after power is stabilized. When

the sensor is reset, all registers are set to their default values.

Analog Power supply : 2.8V DC with 0.1uF capacitor to AGND.

Analog Power ground

Power standby mode. When STDBY=‘1’ there’s no current flow in any analog circuit

branch, neither any beat of digital clock. D<9:0> and PCLK, HSYNC, VSYNC pins can

be programmed to tri-state or all ‘1’ or all ‘0’. But it is possible to control internal registers

through I2C bus interface in STDBY mode. All registers retain their current values.

DAC Power supply : 2.8V DC with 0.1uF capacitor to AGND.

Composite signal. (Connect to 75ohm to AGND)

Connect 37.5ohm to AGND

Analog Power supply : 2.8V DC with 0.1uF capacitor to AGND.

Analog Power ground

DAC Power ground.

External Resistor. The resistor value can be changed by user tuning. (Connect to 30Kohm

to AGND)

Chip Test Mode enable. (Connect to HGND)

Bit 0 of parallel data output.

Bit 1 of parallel data output.

Bit 2 of parallel data output.

Bit 3 of parallel data output.

Master clock input pad or Crystal input pad

Crystal output pad

Pixel clock. Data can be latched by external devices at the rising or falling edge of PCLK.

The polarity and drivability can be controlled.

LED Control bit 0. LEDCTRL[1:0] provide 2bit combination of enable signal which can

turn-on LED device when low light condition.

PD-701-028 Rev 1.2

5/11 CrystalImage & ImagingInnovation

5 Page

PC1030N

1/4 inch VGA class Analog/Digital Output

NTSC/PAL CMOS Image Sensor

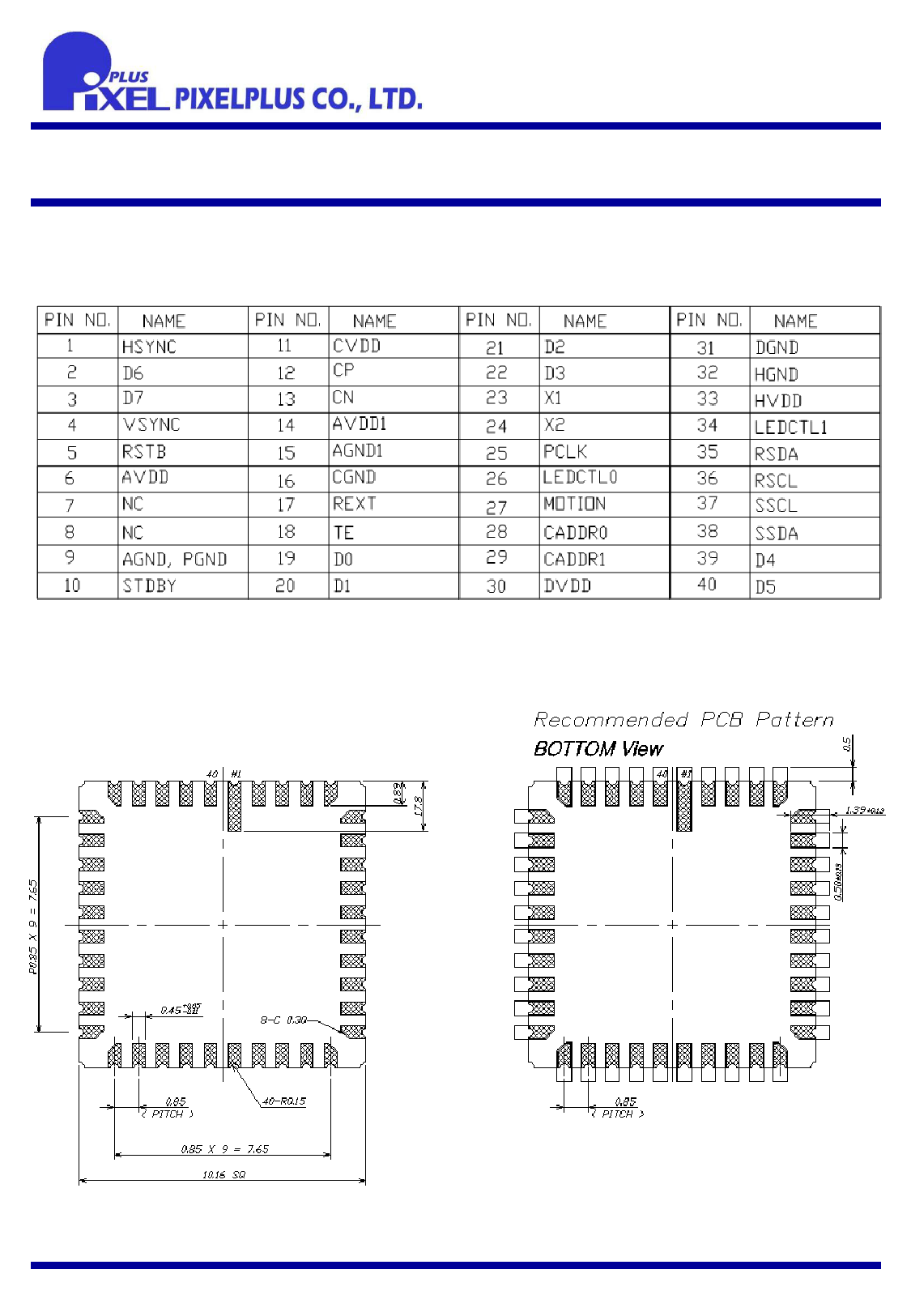

Package Pin Assignment Table

Recommended PCB PAD Size for SMT

40CLCC Package Bottom View

PD-701-028 Rev 1.2

11/11

CrystalImage & ImagingInnovation

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet PC1030N.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PC1030N | NTSC/PAL CMOS Image Sensor | Pixelplus |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |